# **SPKA4 MP Server System**

**Technical Product Specification**

**Revision 1.2**

July 2000

Enterprise Platforms Group Server Products Division

# **Revision History**

| Date      | Revision<br>Number | Modifications   |

|-----------|--------------------|-----------------|

| July 2000 | 1.2                | Initial Release |

|           |                    |                 |

|           |                    |                 |

|           |                    |                 |

# Disclaimers

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications. Intel may make changes to specifications and product descriptions at any time, without notice.

The SPKA4 MP Server System may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata will be available on request.

$l^2C$  is a two-wire communications bus/protocol developed by Philips\*. SMBus is a subset of the  $l^2C$  bus/protocol and was developed by Intel. Implementations of the  $l^2C$  bus/protocol or the SMBus bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

Copyright © Intel Corporation 2000.

\*Other brands and names are the property of their respective owners.

< This page intentionally left blank. >

# **Table of Contents**

| 1. In | ntrod | uction1-1                               |

|-------|-------|-----------------------------------------|

| 2. S  | PKA   | 4 MP Server Chassis Feature Overview2-1 |

| 2.1   | Ch    | assis Features2-1                       |

| 2.2   | Ho    | t-plug PCI2-1                           |

| 2.3   | Fro   | ont Bezel Features2-1                   |

| 2.4   | Se    | curity2-1                               |

| 2.5   | I/O   | Panel2-1                                |

| 2.6   | Ch    | assis Dimensions2-2                     |

| 2.7   | Ch    | assis View2-2                           |

| 3. P  | ower  | <sup>·</sup> Supply Subsystem3-1        |

| 3.1   | Po    | wer Supply Subsystem Feature Overview   |

| 3.2   | Po    | wer Supply Mechanicals3-2               |

| 3.    | .2.1  | Airflow                                 |

| 3.    | .2.2  | Temperature3-3                          |

| 3.    | .2.3  | Acoustics                               |

| 3.    | .2.4  | DC Output Connector                     |

| 3.3   | Po    | wer Supply Electricals                  |

| 3.    | .3.1  | Efficiency                              |

| 3.    | .3.2  | AC Input Voltage Specification          |

| 3.4   | DC    | COutput Specification                   |

| 3.    | .4.1  | DC Outputs Rating                       |

| 3.    | .4.2  | DC Output Maximum Rating                |

|    | 3.4 | .3   | Power Timing                      | 3 |

|----|-----|------|-----------------------------------|---|

| 3  | 3.5 | Pro  | otection Circuits                 | C |

|    | 3.5 | 5.1  | Over-voltage Protection           | C |

|    | 3.5 | 5.2  | Over-current Limit                | 1 |

|    | 3.5 | 5.3  | Over-temperature Protection (OTP) | 1 |

|    | 3.5 | 5.4  | Short Circuit Protection          | 1 |

|    | 3.5 | 5.5  | Hot Swap3-1                       | 1 |

|    | 3.5 | 5.6  | Forced Load Sharing3-12           | 2 |

|    | 3.5 | 5.7  | Control Signals                   | 2 |

|    | 3.5 | 6.8  | LED Indicators                    | 6 |

| 4. | Ро  | wer  | Distribution Board4-1             |   |

| 2  | 4.1 | Intr | roduction4-                       | 1 |

|    | 4.1 | .1   | Feature Overview4-                | 1 |

| 2  | 1.2 | Ph   | ysical Description4-              | 1 |

|    | 4.2 | 2.1  | Location4-2                       | 2 |

| 2  | 4.3 | Ele  | ectrical Connections4-2           | 2 |

| 2  | 1.4 | Po   | wer Supply Connectors4-3          | 3 |

| 2  | 4.5 | Ba   | seboard Power Connectors4-3       | 3 |

| 2  | 4.6 | Ba   | seboard Auxiliary4-4              | 4 |

| 2  | 4.7 | Pe   | ripheral Power Connector4-        | 5 |

| 2  | 4.8 | Po   | wer Output4-6                     | 6 |

| 2  | 1.9 | Se   | rver Management Features4-6       | 6 |

| 5. | Sy  | ster | m Cooling5-1                      |   |

| Ę  | 5.1 | Fa   | ns5-*                             | 1 |

| Ę  | 5.2 | He   | at Load5-2                        | 2 |

|    |     |      |                                   |   |

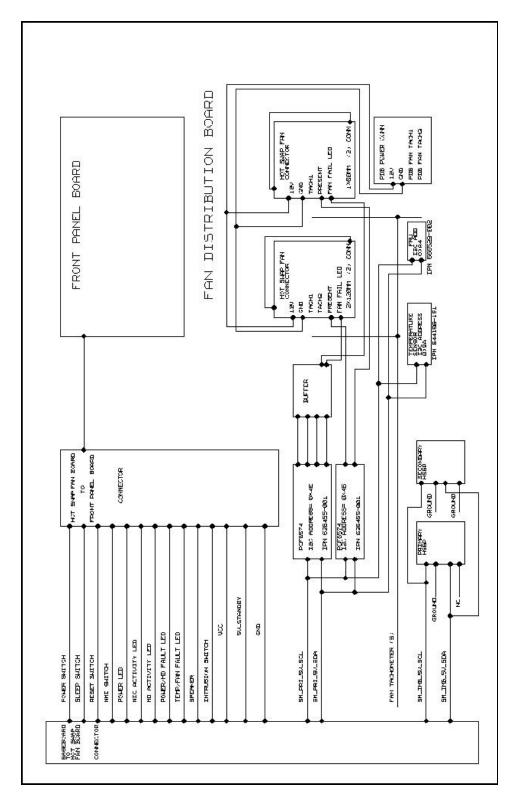

| 5  | 5.3 I        | an Distribution Board5-2                                  |

|----|--------------|-----------------------------------------------------------|

|    | 5.3.1        | FDB Features5-4                                           |

|    | 5.3.2        | Physical Description5-4                                   |

|    | 5.3.3        | Electrical Connections5-4                                 |

|    | 5.3.4        | Functional Architecture5-7                                |

| 6. | Syst         | em Peripheral Bays6-1                                     |

| 6  | 6.1 3        | 3.5" Floppy Drive Bay6-1                                  |

| 6  | 5.2 5        | 5.25" Drive Bays                                          |

| 6  | 6.3 I        | nternal 3.5" Hard Drive Bays with Hot-swap SCSI Backplane |

|    | 6.3.1        | Hot-swap SCSI Drive Bay Drawings6-2                       |

| 7. | SCS          | I Backplane Board Set7-1                                  |

| 7  | '.1 F        | Feature Overview7-1                                       |

| 7  | 7.2 I        | Placement Diagrams7-2                                     |

|    | 7.2.1        | SCSI Bus Considerations7-4                                |

|    | 7.2.2        | SCSI Bus Notes7-5                                         |

|    | 7.2.3        | Deviations from SAF-TE Specification7-5                   |

| 7  | 7.3 <i>/</i> | Architectural Overview7-5                                 |

|    | 7.3.1        | Wide SCSI Connector7-6                                    |

|    | 7.3.2        | SCA-2 Connectors7-6                                       |

|    | 7.3.3        | SCSI Multi-mode Termination7-6                            |

|    | 7.3.4        | SCSI Interface7-6                                         |

|    | 7.3.5        | Power Control7-6                                          |

|    | 7.3.6        | FET Short Protection                                      |

|    | 7.3.7        | 7-7 Microcontroller                                       |

|    | 7.3.8        | Device SCSI ID                                            |

| 7.3    | 3.9         | Hard Drive Fault LED                                          | 7-7  |

|--------|-------------|---------------------------------------------------------------|------|

| 7.3    | 3.10        | IMB (l <sup>2</sup> C* bus)                                   | 7-8  |

| 7.3    | 3.11        | Fan                                                           | 7-8  |

| 7.3    | 3.12        | Temperature                                                   | 7-8  |

| 7.3    | 3.13        | Serial EEPROM                                                 | 7-8  |

| 7.4    | Firi        | mware Information                                             | 7-8  |

| 7.5    | Inte        | erface Specifications                                         | 7-8  |

| 7.5    | 5.1         | SCSI Input Connector 68P                                      | 7-8  |

| 7.5    | 5.2         | Cables                                                        | 7-13 |

| 8. Fro | ont         | Panel Board                                                   | 8-1  |

| 8.1    | Co          | nnector Pinout                                                | 8-1  |

| 8.1    | 1.1         | Fan Distribution Board/Front Panel Interface (J3)             | 8-1  |

| 8.1    | .2          | Chassis Intrusion Switch Connector Interface (J1, J2)         | 8-2  |

| 8.2    | Sig         | Inal Descriptions                                             | 8-2  |

| 8.3    | SK          | A4 Front Panel Mechanical Outline                             | 8-4  |

| 9. SK  | <b>(</b> A4 | Board Set                                                     | 9-1  |

| 9.1    | SK          | A4 Architecture Overview                                      | 9-1  |

| 10. Sy | ster        | n Interconnection                                             | 10-1 |

| 10.1   | I/          | O Panel Connectors                                            | 10-1 |

| 10.2   | S           | System Internal Cables                                        | 10-1 |

| 10.3   | S           | System Cabling Diagram                                        | 10-3 |

| 11. Ce | ertifi      | cation                                                        | 11-5 |

| 11.1   | S           | Safety Standards/Certifications                               | 11-5 |

| 11.2   | E           | Electromagnetic Compatibility (EMC) Regulations               | 11-5 |

| 11.3   | Ν           | Iandatory/Standard Certifications; Registration; Declarations | 11-6 |

| 12. Env  | vironmental Limits                        | 12-1 |

|----------|-------------------------------------------|------|

| 12.1     | System Office Environment                 | 12-1 |

| 12.2     | System Environmental Testing              | 12-1 |

| 13. Reli | iability, Serviceability and Availability | 13-1 |

| Append   | dix A: Glossary                           | i    |

| Append   | dix B: Reference Documents                | ii   |

# **List of Figures**

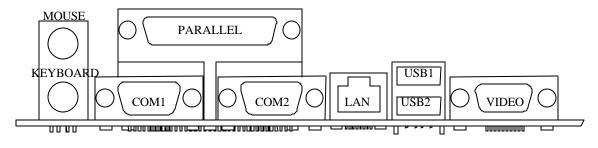

| Figure 2-1: I/O Connectors                                                                 | .2-2 |

|--------------------------------------------------------------------------------------------|------|

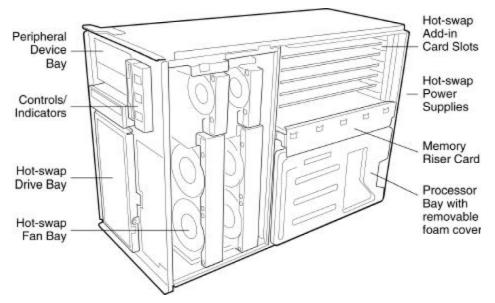

| Figure 2-2: SPKA4 MP Server System Drawing with Side Panels and Front Panel<br>Removed     | .2-2 |

| Figure 2-3: SPKA4 MP Server System Photograph with Side Panels and Front Panel<br>Removed  | 2-3  |

| Figure 3-1: Location of the Power Supplies in the SPKA4 Pedestal Configuration (rear view) |      |

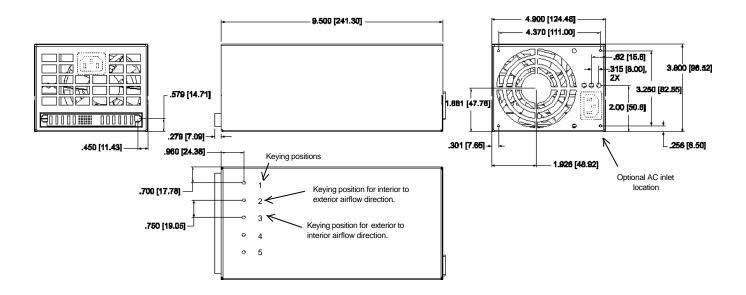

| Figure 3-2: Power Supply Mechanical Drawing                                                | .3-3 |

| Figure 3-3: Connector Pin Locations                                                        | .3-5 |

| Figure 3-4: Output Voltage Timing                                                          | .3-9 |

| Figure 3-5: Turn On/Off Timing                                                             | 3-10 |

| Figure 4-1: Power Distribution Board Diagram                                               | .4-2 |

| Figure 4-2: Power Supply Mating Connector Pin Locations                                    | .4-3 |

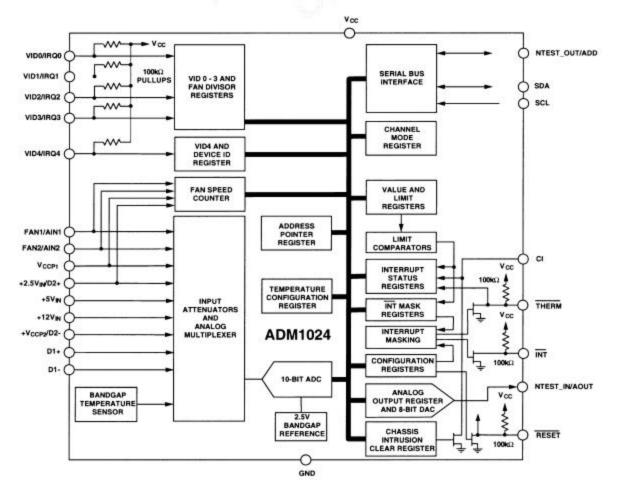

| Figure 4-3: ADM1024* Block Diagram                                                         | .4-6 |

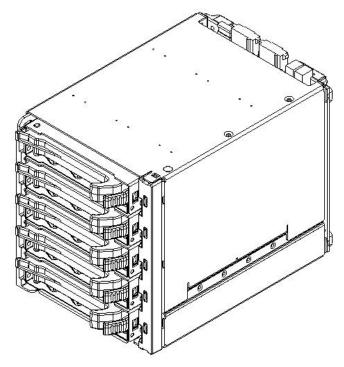

| Figure 5-1: SPKA4 Dual Fan Assembly for Processor Cooling                                  | 5-1  |

| Figure 5-2: SPKA4 Fan Assembly for Add-in card Cooling                                     | 5-1  |

| Figure 5-3: SPKA4 System Showing Four Hot-swappable Fan Assemblies                         | 5-2  |

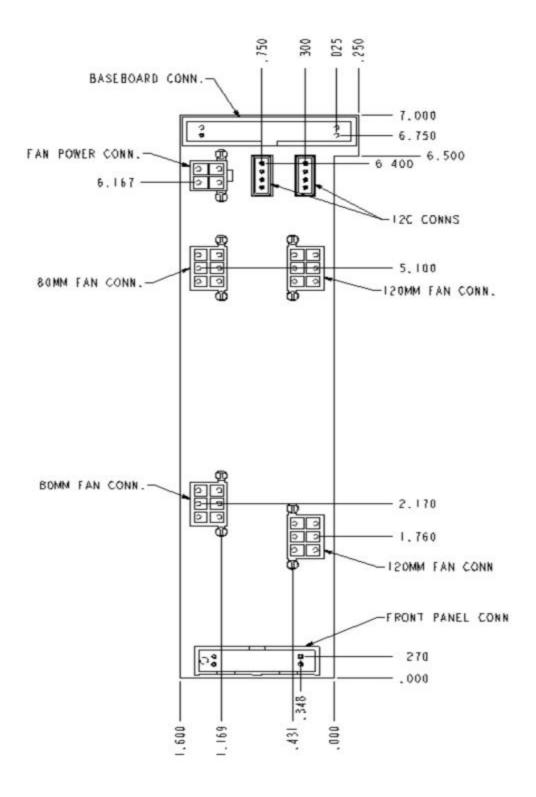

| Figure 5-4: FDB Fan Connectors                                                             | 5-3  |

| Figure 5-5: Fan Distribution Board Location                                                | .5-4 |

| Figure 5-6: Functional Architecture                                                        | .5-8 |

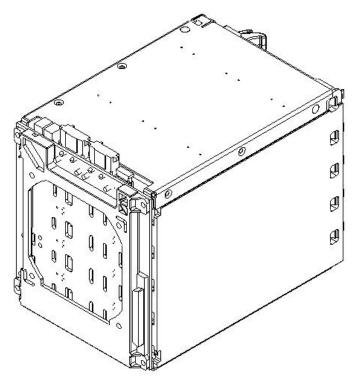

| Figure 6-1: Hot-swap Drive Bay, Front Isometric View                                       | .6-2 |

| Figure 6-2: Hot-swap Drive Bay, Rear Isometric View                                        | .6-3 |

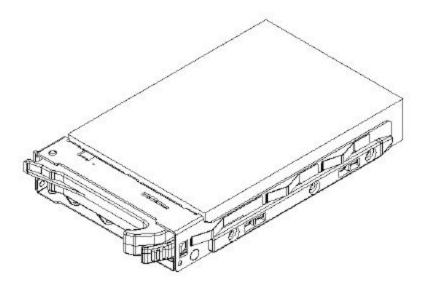

| Figure 6-3: Hot-swap Drive Carrier with Drive Installed                                    | .6-3 |

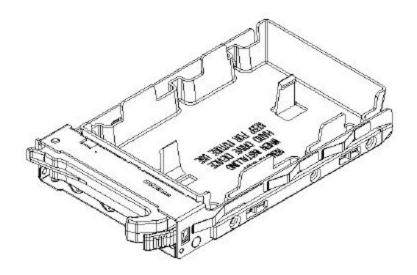

| Figure 6-4: Drive Carrier with Air Baffle Installed                                        | .6-4 |

| Figure 7-1: SPKA4 SCSI Backplane Placement                                                 | 7-3  |

| Figure 7-2: SPKA4 SAF-TE Board Placement                                                   | 7-4  |

| Figure 7-3: Functional Block Diagram                                                       | .7-6 |

| Figure 7-4: SCSI Input Connector 68P Non-shielded                                          | 7-9  |

| Figure 7-5: SCA-2 Connector 80P                                                            | 7-10 |

| Figure 8-1: SKA4 Front Panel Mechanical Specification                                      | .8-4 |

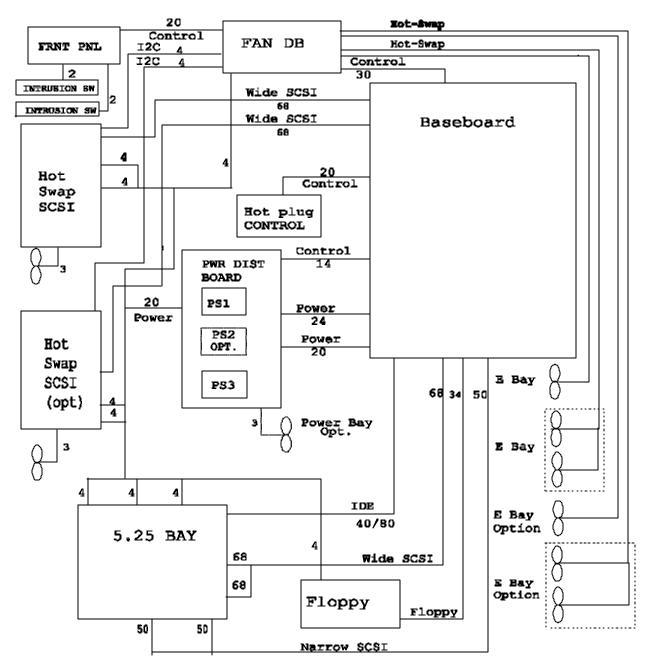

| Figure 10-1: SPKA4 MP Server System Cabling Diagram10-3 |

|---------------------------------------------------------|

|---------------------------------------------------------|

# **List of Tables**

| Table 2-1: System Dimensions                                        | 2-2  |

|---------------------------------------------------------------------|------|

| Table 3-1: Airflow                                                  | 3-3  |

| Table 3-2: Temperature                                              | 3-3  |

| Table 3-3: Signal Descriptions                                      |      |

| Table 3-4: Output Connector Pinout                                  |      |

| Table 3-5: AC Input Voltage Rating                                  | 3-5  |

| Table 3-6: AC Line Sag Transient Performance                        | 3-6  |

| Table 3-7: AC Line Surge Transient Performance                      | 3-6  |

| Table 3-8: DC Output Voltage Limits                                 |      |

| Table 3-9: 375 W Load Ratings                                       |      |

| Table 3-10: Total System Load at Line AC Input (for reference only) | 3-8  |

| Table 3-11: Output Voltage Timing                                   | 3-8  |

| Table 3-12: Turn On/Off Timing                                      | 3-9  |

| Table 3-13: Over-voltage Limits                                     | 3-10 |

| Table 3-14: Over-current Protection                                 | 3-11 |

| Table 3-15: PS-ON Signal Characteristic                             | 3-12 |

| Table 3-16: PWOK Signal Characteristics                             | 3-13 |

| Table 3-17: PSKILL Signal Characteristics                           | 3-13 |

| Table 3-18: FAIL Signal Characteristics                             | 3-14 |

| Table 3-19: PRFL Signal Characteristics                             | 3-14 |

| Table 3-20: PRESENT <sup>#</sup> Signal Characteristics             | 3-14 |

| Table 3-21: Power Supply FANC                                       | 3-15 |

| Table 3-22: LED Indicators                                          | 3-16 |

| Table 3-23: Power Supply LED Indicators and Control Signal Logic    | 3-16 |

| Table 4-1: Signal Pins and Power Blades                             | 4-3  |

| Table 4-2: Baseboard Power Connectors                               | 4-3  |

| Table 4-3: Connector Pinout                                         | 4-4  |

| Table 4-4: Baseboard Auxiliary                                      | 4-4  |

| Table 4-5: Peripheral Power Connector                      | 4-5  |

|------------------------------------------------------------|------|

| Table 4-6: Power Form Capabilities                         | 4-6  |

| Table 4-7: Connection of Signals to ADM1024*               | 4-6  |

| Table 5-1: Baseboard Connector (J9)                        | 5-5  |

| Table 5-2: Front Panel Connector (J4)                      | 5-6  |

| Table 5-3: Hot-swap Fan Connectors (J1, J2, J5, J6)        | 5-6  |

| Table 5-4: Power Connector (J3)                            | 5-7  |

| Table 5-5: Hot-swap SCSI Backplane Connector (J7, J8)      | 5-7  |

| Table 7-1: SCSI ID Assignment 3 x 1.6" Backplane           | 7-7  |

| Table 7-2: SCSI ID Assignment 5 x 1" Backplane             | 7-7  |

| Table 7-3: SCSI Input Connector (J1D1)                     | 7-9  |

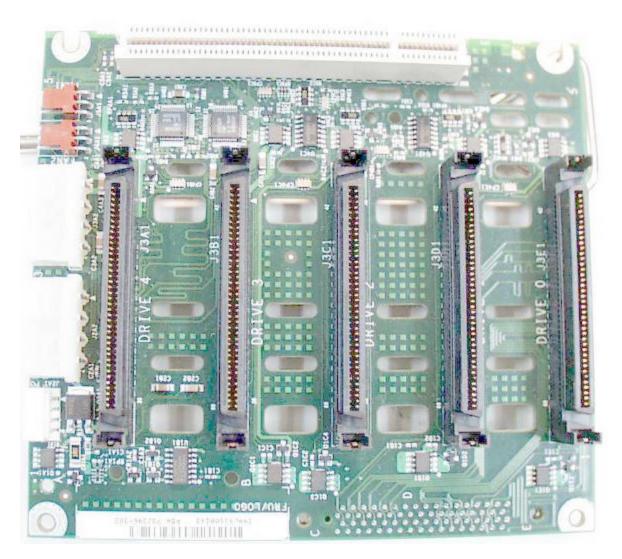

| Table 7-4: SCA-2 Connectors (J3E1, J3D1, J3C1, J3B1, J3A1) | 7-10 |

| Table 7-5. I <sup>2</sup> C* Connector (J2A1)              | 7-11 |

| Table 7-6. Power Connector (J4A1, J3A2)                    | 7-11 |

| Table 7-7. Fan Connector                                   | 7-12 |

| Table 7-8 PCI Connector (J5C1)                             | 7-12 |

| Table 8-1: Front Panel Features                            | 8-1  |

| Table 8-2: Fan Distribution Board/Front Panel Interface    | 8-2  |

| Table 8-3: Chassis Intrusion Switch Connector Interface    | 8-2  |

| Table 8-4: Signal Descriptions                             | 8-2  |

| Table 12-1: System Office Environment Summary              | 12-1 |

# 1. Introduction

This product specification details the features of the SPKA4 MP server system. Low cost, time to market, modularity, and utilization for multiple configurations are primary considerations in the design. The chassis has user friendly features, and is accessible and serviceable.

The SPKA4 MP server system also incorporates features for high availability servers. This includes power and cooling systems with optional redundancy, hot-swap or easy to replace fans, hot-plug PCI slots, and a mass storage system with hot-swappable hard drives. These are key components for increasing the availability of the server. Since the fans and power supplies typically have the lowest Mean Time Between Failure (MTBF) specifications, the optional redundancy of these components will permit the system to continue to operate with a failed fan or power supply and continue to operate, for a limited time, while replacing a power supply. With the use of RAID technology, the system can continue to operate with hard drive failures. The hot-plug hard drives allow a failed hard drive to be replaced while the system continues to operate.

This product specification details the following:

- ?? SPKA4 chassis features.

- ?? Power supply subsystem.

- ?? Chassis cooling.

- ?? Peripheral bays.

- ?? Front panel.

- ?? Baseboard.

- ?? I/O and interconnects.

- ?? System configuration.

- ?? System certifications.

- ?? Environmental limits.

- ?? Reliability, serviceability, and availability.

< This page intentionally left blank. >

# 2. SPKA4 MP Server Chassis Feature Overview

# 2.1 Chassis Features

The SPKA4 MP server chassis is 12.25 inches wide, 18.06 inches high, and 25.25 inches deep in the pedestal configuration. The chassis is designed to be modular with a base unit with two easily removable units, one to hold the front panel and drive bays (C-tilt) and one to hold the baseboard and I/O panels (E-bay). The base section is U shaped and holds the power supplies and the power distribution board. The E-bay drops in at the rear of the base unit and the C-tilt drops in from the front. Two captive screws in the front cover fasten both the C-tilt and the Ebay to the base unit. The E-bay fans are plugged into a hot-swap fan holder and installed above the drives and in front of the E-bay. Three bays are supplied in the back of the chassis base unit for power supplies. There are two covers on the right side to provide EMI shielding. One cover provides tool-less access to the hot-plug PCI slots and allows a secondary cover to be removed to provide access to the rest of the baseboard electronics. The second (front) cover allows access to the hot-swappable cooling fans.

A pedestal kit (SKCBPEDMT), consisting of one top cover, one side cover, a pedestal bezel, and two feet, is utilized for pedestal applications.

A rack mount kit (SKCBRACKMT), consisting of two rails, two handles, four brackets, and a rack bezel, can be installed allowing the system to be mounted in a rack as a 7U-rack unit.

# 2.2 Hot-plug PCI

The system has six hot-plug PCI slots, which are accessible under the side/top access cover, and which can be removed, without tools, while the system continues to run. For each PCI slot, there is a thumb-latch to retain the PCI card, a push-button switch that informs the system software when it is pressed, and a pair of LEDs that show the state of the PCI slot.

# 2.3 Front Bezel Features

The front bezel is a multiple-part plastic molding. There is one key-lockable door covering the drive bays. The front panel indicator LEDs, power switch, sleep switch, reset switch, and NMI switch are on the upper right for the pedestal chassis.

# 2.4 Security

At the system level, a variety of security options are provided. A three-position key locks either the front part of the side access cover or the front part of the side access cover and the front bezel door. In addition, there are intrusion switches for the front and rear parts of the side access cover and provision for a small padlock on the drive bay (3.5") door. Provision for a Kensington\* lock is provided in the rear panel.

# 2.5 I/O Panel

All input/output connectors are accessible at the back of the chassis. The built-in interfaces on the baseboard are mapped in the figure below.

Figure 2-1: I/O Connectors

# 2.6 Chassis Dimensions

#### Table 2-1: System Dimensions

| Configuration   | Pedestal                      | Rack                           |

|-----------------|-------------------------------|--------------------------------|

| Height          | 18.06 inches with feet        | 7U                             |

| Width           | 12.22 inches                  | Fits 19" standard rack         |

| Depth           | 25.25 inches                  | 25.25 inches                   |

| Clearance Front | 12 inches                     | Rack must not restrict airflow |

| Clearance Rear  | 9 inches                      | Rack must not restrict airflow |

| Clearance Side  | 0 inches                      | NA                             |

| Weight          | 120 lb. maximum configuration | 120 lb. maximum configuration  |

# 2.7 Chassis View

Figure 2-2: SPKA4 MP Server System Drawing with Side Panels and Front Panel Removed

Figure 2-3: SPKA4 MP Server System Photograph with Side Panels and Front Panel Removed

< This page intentionally left blank. >

# 3. Power Supply Subsystem

# 3.1 **Power Supply Subsystem Feature Overview**

This section defines the SSI compliant 375 watt SPKA4 power supply, a universal input switching power supply. The power supply is power factor corrected at AC input with forced current sharing and remote sense regulation at DC output. The supply can be used either singly or with its DC outputs paralleled with other identical supplies to form a redundant power system with hot swap replacement capability. The supply +5 VDC standby output will be present whenever AC power is applied. The power supply is rated to supply the following DC voltage levels:

- ?? +3.3 VDC at 34 A.

- ?? +5 VDC at 34 A.

- ?? +12 VDC at 18 A peak 18.5 A <10mS.

- ?? -12 VDC at 1.0 A.

- ?? +5 V standby at 2 A.

Maximum continuous power output of any combined DC loading shall not exceed 375 watts.

The SPKA4 power subsystem is a modular design. The system may be configured with one, two, or three power supplies. These configurations are referenced as Entry Level Power, Maximum Level Power, and Maximum Level Redundant Power. The power sharing circuitry is internal to each supply and a power distribution board is used for connecting the power supplies together and for connecting the power supplies to the system.

For Maximum Level Redundant Power systems, the loss of a single power supply will not affect the operation of the system. A Power Supply Failure LED on the front panel will be turned on, and the failed supply can be replaced with the system operating. Each supply has LEDs on the rear which indicate the state of the power supply.

Each power supply has its own power cord with a detail provided in the power supply handle to hold the cord and prevent accidental disconnection from the supply. All supplies should be connected to the same AC mains branch circuit.

The power supply is inserted into and removed from the chassis from the rear and is held in place with a pivoting handle which is secured by four screws.

The power supply is located inside an Intel<sup>®</sup> system assembly. The location and orientation are shown in the figure below. A system may contain one, two, or three power supplies.

Figure 3-1: Location of the Power Supplies in the SPKA4 Pedestal Configuration (rear view)

# 3.2 **Power Supply Mechanicals**

The SPKA4 MP system power supply conforms to the Midrange SSI power supply specification and is equipped with a pivoting latch/handle to allow easy insertion/removal from the system.

The chassis for the power supply has been designed for a 92-mm size fan. There are keying positions on the power supply, which prevents a power supply with the wrong airflow direction from being plugged into a system. Figure 3-2 shows the physical size of the supply with connector locations. The AC inlet can be located on the interior or exterior face of the power supply. The power supply has a required handle and faceplate assembly, which pivots to assist insertion and extraction and provides retention.

Figure 3-2: Power Supply Mechanical Drawing

#### 3.2.1 Airflow

The airflow intake is from the DC connector face, and the air is exhausted on the handle face of the supply.

The minimum airflow required by the power supply for cooling at high and low fan speeds ( $Q_{high}$ ,  $Q_{low}$ ) is shown in Table 3-1.

#### Table 3-1: Airflow

| Item              | Description                                                                                 | Min. | Max. | Units |

|-------------------|---------------------------------------------------------------------------------------------|------|------|-------|

| Q <sub>high</sub> | Airflow through power supply; max. load,<br>T <sub>ambient</sub> =50?C, 5000 ft. elevation. | 21   |      | CFM   |

| Q <sub>low</sub>  | Airflow through power supply; max. load,<br>T <sub>ambient</sub> =35?C, 5000 ft. elevation. | 17   |      | CFM   |

### 3.2.2 Temperature

#### Table 3-2: Temperature

| Item                | Description                                                                                                                                                            | Min. | Max.     | Units |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|-------|

| T <sub>op</sub>     | Operating temperature range.                                                                                                                                           | 0    | 50       | ?C    |

| ?T <sub>ps</sub>    | Temperature rise from inlet air to outlet air of<br>power supply.<br>375 W output power, 21CFM, sea level, 25?C inlet<br>air.<br>17CFM, 375 W output power, sea level. |      | 21<br>26 | ?C    |

| T <sub>non-op</sub> | Non-operating temperature range.                                                                                                                                       | -40  | 70       | ?C    |

| T <sub>case</sub>   | Maximum case temperature of any external surface of the power supply enclosure; $T_{op}$ =25?C.                                                                        |      | 50       | ?C    |

## 3.2.3 Acoustics

The power supply incorporates a 92mm low noise fan to exhaust air from the peripheral bay. These fans have thermal sensors for speed control and incorporate a tachometer output.

The power supply runs at LOW fan speed under the conditions defined for  $Q_{low}$  in Table 3-1. The power supply has less than 43 dBA of sound pressure noise ( $L_p$ ) at any bystander microphone location when operating at LOW fan speed. Sound pressure is a measurement of the total noise at the specified microphone location in the room.

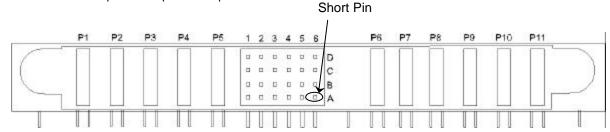

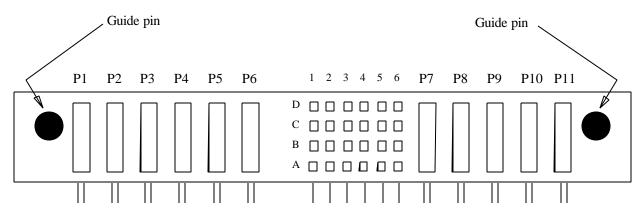

## 3.2.4 DC Output Connector

DC power and control signals are interfaced to the system distribution and control subsystem via connectors which dock with mating connectors when the power supply is inserted into the system power distribution board. The output connector is a blind mating type connector that connects the power supplies' output voltages, control signals, and alarm signals. Connector pin assignments are listed in Table 3-4, and show the pin locations for the output connector. The signal pins are 3A rated contacts. Pin A6 is shortened to allow for hot-swapping of the power supply. The connector is keyed to the power supply by the positioning of the guide/keying pins on either side of the connector. The keying location for the recommended connector is A1.

| Table | 3-3: | Signal   | Descriptions |

|-------|------|----------|--------------|

| labic | 00.  | Gigiliai | Descriptions |

| Signal            | Description          | Signal               | Description               | Signal | Description                    |

|-------------------|----------------------|----------------------|---------------------------|--------|--------------------------------|

| 12LS              | 12 V load share bus  | PWOK                 | Power OK output           | 5VSB   | 5 V standby output             |

| 5LS               | 5 V load share bus   | ACOK <sup>#</sup>    | AC OK output              | -12 V  | -12 V output                   |

| 3.3LS             | 3.3 V load share bus | ACRange              | AC input range select     | SCL    | I <sub>2</sub> C clock signal  |

| 12VS              | 12 V remote sense    | PSKILL               | Supply fast shutdown      | SDA    | I <sub>2</sub> C data signal   |

| 5VS               | 5 V remote sense     | FAIL                 | Failure signal            | A0     | I <sub>2</sub> C address bit 0 |

| 3.3VS             | 3.3 V remote sense   | PRFL                 | Predictive failure signal | A1     | I <sub>2</sub> C address bit 1 |

| ReturnS           | Return remote sense  | PRESENT <sup>#</sup> | Power supply present      | FANC   | Fan control signal             |

| PSON <sup>#</sup> | Power enable input   |                      |                           |        |                                |

#### Table 3-4: Output Connector Pinout

| Signal Pins |              |       |       |                 |    |                  |    |      |      |                   |    |       |                  |

|-------------|--------------|-------|-------|-----------------|----|------------------|----|------|------|-------------------|----|-------|------------------|

|             | 1            | 1     | 2     |                 | 3  |                  |    | 4    |      | 5                 |    | 6     |                  |

| D           | 1            | 12LS  | PWOK  |                 | A  | COK <sup>#</sup> |    | ACRa | nge  | ReturnS           |    | -12 \ | V                |

| С           | A            | 40    | SCL   |                 | F  | AIL              |    | PRFL |      | 12VS              |    | 3.3V  | ′SB <sup>1</sup> |

| В           | A            | 41    | SDA   |                 | 3. | .3VS             |    | 5VS  |      | Reserved          |    | +5V3  | SB               |

| А           | 3            | 3.3LS | PRESE | NT <sup>#</sup> | F, | ANC              |    | 5LS  |      | PSON <sup>#</sup> |    | PSK   | ILL              |

|             | Power Blades |       |       |                 |    |                  |    |      |      |                   |    |       |                  |

| P1          | P2           | P3    | P4    | P5              |    | P6               | P7 |      | P8   | P9                | P1 | 0     | P11              |

| Reserved    | +12          | V GND | GND   | GND             |    | GND              | GN | ١D   | +5 V | +5 V              | +3 | .3 V  | +3.3 V           |

#### Notes:

Signals that can be defined as low true or high true use the following convention:  $signal^{\#} = low true$

<sup>1</sup> The 3.3 VSB output is an optional output.

#### Figure 3-3: Connector Pin Locations

Note: PIN # A6 will be shorter than all others for PSKILL implementation.

# **3.3 Power Supply Electricals**

## 3.3.1 Efficiency

The power supply has a minimum efficiency of 60% to its DC output pins at maximum load currents, at rated nominal input voltages and frequencies.

## 3.3.2 AC Input Voltage Specification

The system is specified to operate, without switching, from 100-120 Vac, 200-240 Vac, at 50 or 60 Hz. The power supply incorporates universal power input with active Power Factor Correction (PFC) which shall reduce line harmonics in accordance with the EN61000-3-2 and JEIDA MITI standards. The system is tested to meet these line voltages, and has been tested (but not specified) at +10% and -10% of the voltage ranges, and similarly ? 3 Hz on the line input frequency.

The system is specified to operate without error with line source interruptions not to exceed 20 milliseconds at nominal line conditions and full power supply output load.

The power supply must operate within all specified limits over the following input voltage range. Harmonic distortion of up to 10% THD must not cause the power supply to go out of specified limits.

| Parameter     | Minimum             | Rated                   | Maximum             | Maximum Input<br>Current (375 W) |

|---------------|---------------------|-------------------------|---------------------|----------------------------------|

| Voltage (110) | 90 V <sub>ms</sub>  | 100-127 V <sub>ms</sub> | 132 V <sub>ms</sub> | 7.1 A <sub>ms</sub>              |

| Voltage (220) | 180 V <sub>ms</sub> | 200-240 V <sub>ms</sub> | 264 V <sub>ms</sub> | 3.5 A <sub>ms</sub>              |

| Frequency     | 47 Hz               |                         | 63 Hz               |                                  |

| Table | 3-5  | AC | Innut | Voltage | Rating |

|-------|------|----|-------|---------|--------|

| Table | 5-5. | 70 | mput  | vonage  | naung  |

#### 3.3.2.1 AC Line Dropout

An AC line dropout is defined to be when the AC input drops to 0 VAC for one cycle or less of the AC input during any phase of the AC line. During an AC dropout, the power supply must meet dynamic voltage regulation requirements over the rated load. An AC line dropout shall not cause any tripping of control signals or protection circuits. If the AC dropout lasts longer than one cycle of the AC line, then the power supply should recover and meet all turn on requirements. The power supply must meet the AC dropout requirement over rated AC voltages, frequencies, and output loading conditions. Any dropout of the AC line shall not cause damage to the power supply.

#### 3.3.2.2 AC Line Transient Specification

AC line transient conditions are defined as "sag" and "surge" conditions. The "sag" conditions are also commonly referred to as "brownout." The "sag" condition is defined as the AC line voltage dropping below nominal voltage. The "surge" conditions are defined as when the AC line voltage rises above nominal voltage. The power supply shall meet the performance requirements under the AC line sag and surge conditions shown in Table 3-6 and Table 3-7, respectively.

|                 | AC Line Sag |                                       |                   |                                                |  |  |  |  |

|-----------------|-------------|---------------------------------------|-------------------|------------------------------------------------|--|--|--|--|

| Duration        | Sag         | Operating AC Voltage                  | Line<br>Frequency | Performance Criteria                           |  |  |  |  |

| Continuous      | 10%         | 100VAC-127VAC<br>200VAC-240VAC        | 50/60 Hz          | No loss of function or performance.            |  |  |  |  |

| 0 to 1 AC cycle | 100%        | 100VAC-127VAC<br>200VAC-240VAC        | 50/60 Hz          | No loss of function or performance.            |  |  |  |  |

| > 1 AC cycle    | >10%        | No loss of function or<br>performance | 50/60 Hz          | Loss of function acceptable, self recoverable. |  |  |  |  |

#### Table 3-6: AC Line Sag Transient Performance

#### Table 3-7: AC Line Surge Transient Performance

| AC Line Surge  |       |                      |           |                                     |  |  |  |

|----------------|-------|----------------------|-----------|-------------------------------------|--|--|--|

| Duration       | Surge | Operating AC Voltage | Line      | Performance Criteria                |  |  |  |

|                |       |                      | Frequency |                                     |  |  |  |

| Continuous     | 10%   | 100VAC-120VAC        | 50/60 Hz  | No loss of function or              |  |  |  |

|                |       | 200VAC-240VAC        |           | performance.                        |  |  |  |

| 0 to 1/2 cycle | 30%   | 110VAC, 220VAC       | 50/60 Hz  | No loss of function or performance. |  |  |  |

## 3.3.2.3 Power Recovery

The power supply shall recover automatically after an AC power failure. AC power failure is defined to be any loss of AC power that exceeds the dropout criteria defined in the AC line dropout section above.

# 3.4 DC Output Specification

The power supply DC output specifications shall be met by one supply, by two supplies, or by three supplies operating with their outputs directly paralleled. When operated in parallel, the supplies shall equally share the total load currents within the limits specified herein while meeting all performance requirements of individual supplies. Failure of a supply in a paralleled group or removal of an operational or failed supply from a paralleled group shall not cause DC output transients in excess of the limits specified. Adding an operational or failed supply to a paralleled group shall not cause DC output transients in excess of the limits specified.

Steady state DC output voltages at the remote sense points shall remain within the limits of Table 3-8, for all combinations of operating line, load, load transient, and environment specified herein.

| Parameter     | Min.    | Nom.   | Max.    | Units | Tolerance  |

|---------------|---------|--------|---------|-------|------------|

| +3.3V         | + 3.25  | + 3.30 | + 3.35  | V     | ? 1.5%     |

| +5V           | + 4.90  | +5.00  | + 5.10  | V     | ? 2%       |

| +12V          | + 11.76 | +12.00 | + 12.24 | V     | ? 2%       |

| -12V          | - 13.08 | -12.00 | - 11.40 | V     | + 9% & -5% |

| +5V Standby † | + 4.85  | +5.00  | + 5.20  | V     | + 4% & -3% |

#### Table 3-8: DC Output Voltage Limits

#### Notes:

+ +5V standby shall be in reference to the common remote sense returning potential.

## 3.4.1 DC Outputs Rating

The power supply shall meet the static regulation requirements under the loading conditions specified in Table 3-9. The combined continuous output load applied to the power supply shall not exceed 375 W. If the power supply exceeds 385 W, the power supply should not be subjected to this current draw for more than 12 seconds.

|             | Single Power Supply Maximum Output Current |                    |        |  |  |  |

|-------------|--------------------------------------------|--------------------|--------|--|--|--|

| Voltage     | Minimum Continuous                         | Maximum Continuous | Peak   |  |  |  |

| +3.3V       | 0.5 A                                      | 34 A               |        |  |  |  |

| +5V         | 0.5 A                                      | 34 A               |        |  |  |  |

| +12V        | 0.5 A                                      | 18 A               | 18.5 A |  |  |  |

| -12V        | 0 A                                        | 1.0 A              |        |  |  |  |

| +5V Standby | 0 A                                        | 2 A                |        |  |  |  |

#### Table 3-9: 375 W Load Ratings

#### Notes:

Under some circumstances, a power supply may have 0 load on any or all of its outputs. Under these conditions, the power supply does not need to meet the output regulation specification described in this document, but it must operate without tripping the over-voltage protection circuit or any other fault protection circuitry. When the supply is subsequently loaded, it must begin to regulate and source current without fault.

The total system maximum load condition at AC input is also shown in Table 3-10 below for reference only. Either two or three power supplies can support the total system maximum load.

|             | Total System Maximum Load Condition |                    |      |  |  |  |

|-------------|-------------------------------------|--------------------|------|--|--|--|

| Voltage     | Minimum Continuous                  | Maximum Continuous | Peak |  |  |  |

| +3.3V       | 1.5 A                               | 58 A               |      |  |  |  |

| +5V         | 1.5 A                               | 58 A               |      |  |  |  |

| +12V        | 1.5 A                               | 34 A               | 35 A |  |  |  |

| -12V        | 0.0 A                               | 1.0 A              |      |  |  |  |

| +5V Standby | 0.0 A                               | 2.0 A              |      |  |  |  |

| Table 3-10: Total S | ystem Load at Line | AC Input (f | or reference only)                     |

|---------------------|--------------------|-------------|----------------------------------------|

|                     |                    |             | ······································ |

## 3.4.2 DC Output Maximum Rating

At requirement AC input, maximum continuous power output shall not exceed 375 W. If the power supply exceeds 385 W, the power supply should not be subjected to this maximum current draw for more than 12 seconds.

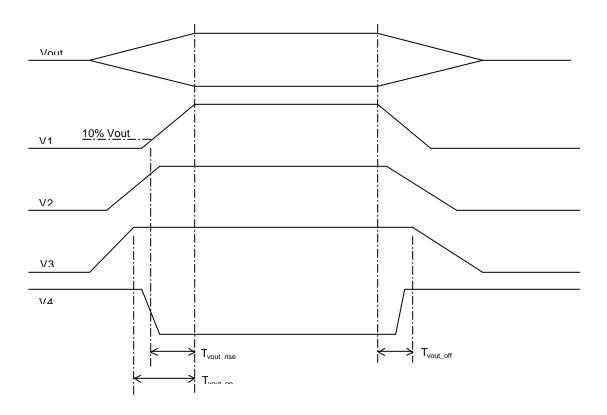

## 3.4.3 Power Timing

This section details the timing requirements for single power supply operation. The output voltages must rise from 10% to within regulation limits ( $T_{vout\_rise}$ ) within 5 to 200 ms. The +3.3 V, +5 V and +12 V output voltages should start to rise approximately at the same time. All outputs must rise monotonically. The +5 V output needs to be greater than the +3.3 V output during any point of the voltage rise, however, never by more than 2.25 V. Each output voltage shall reach regulation within 100ms ( $T_{vout\_on}$ ) of each other and begin to turn off within 100ms ( $T_{vout\_on}$ ) of each other. Refer to

Figure 3-4.

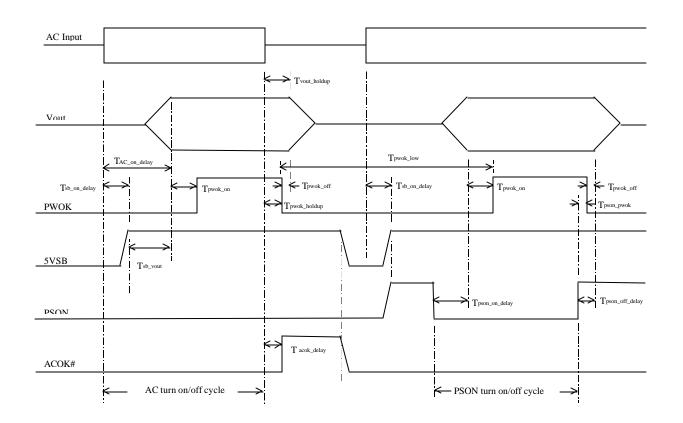

Figure 3-5 shows the timing requirements for a single power supply being turned on and off via the AC input, with PSON held low and the PSON signal, with the AC input applied. The ACOK<sup>#</sup> signal is not being used to enable the turn on timing of the power supply.

| ltem                   | Description                                     | Min. | Max. | Units |

|------------------------|-------------------------------------------------|------|------|-------|

| T <sub>vout_rise</sub> | Output voltage rise time from each main output. | 5    | 200  | msec  |

| T <sub>vout_off</sub>  | All main outputs must be within regulation of   |      | 300  | msec  |

#### Table 3-11: Output Voltage Timing

| Item                 | Description                                                                | Min. | Max. | Units |

|----------------------|----------------------------------------------------------------------------|------|------|-------|

|                      | each other within this time.                                               |      |      |       |

| T <sub>vout_on</sub> | All main outputs must be within regulation of each other within this time. |      | 100  | msec  |

#### Figure 3-4: Output Voltage Timing

#### Table 3-12: Turn On/Off Timing

| Item                     | Description                                                      | Min. | Max. | Units |

|--------------------------|------------------------------------------------------------------|------|------|-------|

| T <sub>sb_on_delay</sub> | Delay from AC being applied to 5 VSB being<br>within regulation. |      | 1500 | msec  |

| Item                       | Description                                                                                                             | Min. | Max. | Units |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------|------|------|-------|

| T <sub>ac_on_delay</sub>   | Delay from AC being applied to all output voltages being within regulation.                                             |      | 2500 | msec  |

| T <sub>vout_holdup</sub>   | Time all output voltages, including 5 VSB, stay within regulation after loss of AC.                                     | 21   |      | msec  |

| T <sub>pwok_holdup</sub>   | Delay from loss of AC to deassertion of PWOK.                                                                           | 20   |      | msec  |

| T <sub>pson_on_delay</sub> | Delay from PSON <sup>#</sup> active to output voltages within regulation limits.                                        | 5    | 400  | msec  |

| T <sub>pson_pwok</sub>     | Delay from PSON <sup>#</sup> deactive to PWOK being deasserted.                                                         |      | 50   | msec  |

| T <sub>acok_delay</sub>    | Delay from loss of AC input to deassertion of ACOK <sup>#</sup> .                                                       | 20   |      | msec  |

| T <sub>pwok_on</sub>       | Delay from output voltages within regulation limits to PWOK asserted at turn on.                                        | 100  | 1000 | msec  |

| T pwok_off                 | Delay from PWOK deasserted to output voltages<br>(3.3 V, 5 V, 12 V, -12 V, 5 VSB) dropping out of<br>regulation limits. | 1    |      | msec  |

| T <sub>pwok_low</sub>      | Duration of PWOK being in the deasserted state during an off/on cycle using AC or the PSON signal.                      | 100  |      | msec  |

| T <sub>sb_vout</sub>       | Delay from 48 VSB being in regulation to 48 VDC being in regulation at AC turn on.                                      | 50   | 1000 | msec  |

#### Figure 3-5: Turn On/Off Timing

# 3.5 **Protection Circuits**

A protection circuit inside the power supply shall cause only the power supply's main outputs to shut down. The 5 VSB output shall remain powered on if the failure does not involve this output. When a protection circuit shuts down the power supply, both the FAIL LED and the FAIL signal will be activated. If the power supply latches off due to a protection circuit tripping, an AC cycle OFF for 15 seconds and a PSON<sup>#</sup> cycle HIGH for 1 second will reset the power supply.

## 3.5.1 Over-voltage Protection

The power supply over-voltage protection shall be locally sensed. The power supply shall shut down in a latch off mode after an over-voltage condition. This latch can be cleared by toggling the power supply off and then on or by an AC power interruption of greater than 1 second. This over-voltage limit applies to all specified AC input voltages and output load conditions. The following table contains the over-voltage limits. The values are measured at the output of the power supply DC connector.

#### Table 3-13: Over-voltage Limits

| Output Voltage | Protection Point [V] |

|----------------|----------------------|

| +3.3 V         | 3.8 4.5              |

| +5 V           | 5.6 6.5              |

| +12 V          | 13 14.5              |

## 3.5.2 Over-current Limit

The power supply has current limits to prevent the +3.3 V, +5 V, and +12 V outputs from exceeding the values shown. The current limiting is the voltage fold-back type. The over-current limit level shall be maintained for a period of 2.6 seconds minimum and the power supply will latch off after 3.6 seconds.

| Voltage | Over Current Limit<br>(lout limit) |  |

|---------|------------------------------------|--|

| +3.3 V  | 110% minimum; 150% maximum         |  |

| +5 V    | 110% minimum; 150% maximum         |  |

| +12 V   | 110% minimum; 150% maximum         |  |

#### Table 3-14: Over-current Protection

## 3.5.3 Over-temperature Protection (OTP)

The power supply is protected against over-temperature conditions caused by a loss of fan cooling or excessive ambient temperature. In an OTP condition, the PSU will shut down. Once the power supply temperature drops within specified limits, the power supply shall restore power automatically. The OTP circuit has built in hysteresis such that the power supply will not oscillate on and off when the temperature drops within specified limits. The power supply shall alert the system under either primary or secondary OTP condition via the power supply FAIL signal and

the FAIL LED. The failed LED will illuminate to indicate such OTP condition in 1+n power supply configurations.

## 3.5.4 Short Circuit Protection

The protection circuit inside the power supply shall cause only the power supply's main outputs to shut down. The 5 VSB output shall remain powered on if the failure does not involve this output. When a protection circuit shuts down the power supply, the LEDs shall indicate an OCP condition (per Table 3-22) and the FAIL signal shall be activated.

## 3.5.5 Hot Swap

Hot-swapping a power supply is the process of inserting and extracting a power supply from an operating power system. The power supply can be hot-swapped by the following methods:

- ?? Extraction: The AC power is disconnected from the power supply, then the power supply is removed from the system. Insertion: The power supply is inserted into the system without the AC power applied, then the AC power is applied.

- ?? Server management turning on the hot-swapped power supply. Extraction: Server management turns off only one of the power supplies via the PSON signal, then the power supply is removed from the system. Insertion: Power supply is inserted into the system, server management looks for power supply, depending upon the state of the system (on or off); the system then turns on the power supply via the PSON<sup>#</sup> signal or goes to standby mode operation.

In general, a failed (off by internal latch or external control) supply may be removed, then replaced with a good power supply; however, hot swap needs to work with operational as well as failed power supplies.

# 3.5.6 Forced Load Sharing

The +3.3 V, +5 V, and +12 V outputs will have forced load sharing. The outputs will share within 10% at full load. All current sharing functions are implemented internal to the power supply by making use of the 3.3LS, 5LS, and 12LS signals. The system connects the 3.3LS, 5LS, and 12LS signals between the power supplies. The supplies must be able to load share with up to four power supplies in parallel and operate in a hot swap/redundant n+1 configuration where n=1, 2, or 3.

Example of load share accuracy: Power supply #1 = 10.0 A

Power supply #2 > 9.0 A and < 11.0 A

# 3.5.7 Control Signals

### 3.5.7.1 PSON

The PSON<sup>#</sup> signal is required to remotely turn on/off the power supply. PSON<sup>#</sup> is an active low signal that turns on the 3.3 V, 5 V, 12 V, and -12 V power rails. When this signal is not pulled low by the system, or left open, the outputs (except the 5 VSB) turn off. This signal is pulled to a standby voltage by a pull-up resistor internal to the power supply. Refer to Figure 3-5 for the timing diagram.

| Signal Type                                    | Accepts an open collector/drain input from the system. Pull-up to VSB located in power supply. |          |  |

|------------------------------------------------|------------------------------------------------------------------------------------------------|----------|--|

| PSON <sup>#</sup> = Low, PSKILL = Low          | ON                                                                                             |          |  |

| PSON <sup>#</sup> = Open, PSKILL = Low or Open | OFF                                                                                            |          |  |

| PSON <sup>#</sup> = Low, PSKILL = Open         | OFF                                                                                            |          |  |

|                                                | Min.                                                                                           | Max.     |  |

| Logic level low (power supply ON)              | 0 V                                                                                            | 1.0 V    |  |

| Logic level high (power supply OFF)            | 2.0 V                                                                                          | 5.25 V   |  |

| Source current, Vpson = low                    |                                                                                                | 4 mA     |  |

| Power up delay: T <sub>pson_on_delay</sub>     | 5 msec                                                                                         | 400 msec |  |

| Power down delay: T <sub>pson_off_delay</sub>  | 1.1 msec                                                                                       |          |  |

| PWOK delay: T pson_pwok                        |                                                                                                | 50 msec  |  |

#### Table 3-15: PS-ON Signal Characteristic

#### 3.5.7.2 PWOK

PWOK is a power good signal and will be pulled HIGH by the power supply to indicate that all the outputs are within the regulation limits of the power supply. When any output voltage falls below regulation limits or when AC power has been removed for a time long enough so that power supply operation is no longer guaranteed, PWOK will be de-asserted to a LOW state. See Figure 3-5 for a representation of the timing characteristics of PWOK. The start of the PWOK delay time shall be inhibited as long as any power supply output is in current limit.

| Signal Type                              | Open collector/drain output from power supply. Pull-<br>up to VSB located power supply. |           |  |

|------------------------------------------|-----------------------------------------------------------------------------------------|-----------|--|

| PWOK = High                              | Power Good                                                                              |           |  |

| PWOK = Low                               | Power Not Good                                                                          |           |  |

|                                          | Min. Max.                                                                               |           |  |

| Logic level low voltage, Isink=4mA       | 0 V                                                                                     | 0.4 V     |  |

| Logic level high voltage, Isource=200? A | 2.4 V                                                                                   | 5.25 V    |  |

| Sink current, PWOK = low                 |                                                                                         | 4 mA      |  |

| Source current, PWOK = high              |                                                                                         | 2 mA      |  |

| PWOK delay: T <sub>pwok_on</sub>         | 100 ms                                                                                  | 1000 ms   |  |

| PWOK rise and fall time                  |                                                                                         | 100 ? sec |  |

| Power down delay: T pwok_off             | 1 ms                                                                                    | 200 mSec  |  |

#### Table 3-16: PWOK Signal Characteristics

### 3.5.7.3 PSKILL Signal

The purpose of the PSKILL pin is to allow for hot-swapping of the power supply. The PSKILL pin on the power supply is shorter than the other signal pins. When a power supply is operating in parallel with other power supplies and then extracted from the system, the PSKILL pin will quickly turn off the power supply and prevent arcing of the DC output contacts.  $T_{PSKIII}$  (shown below in Table 3-17) is the minimum time delay from the PSKILL pin unmating to when the power pins unmate. The power supply will discharge its output inductor within this time from the unmating of the PSKILL pin. When the PSKILL signal pin is not pulled down or left opened

(power supply is extracting from the system), the power supply should shut down regardless of the condition of the PSON<sup>#</sup> signal. The mating pin of this signal in the system is tied to ground. Upon receiving a LOW state signal at the PSKILL pin, the power supply will be allowed to turn on via the PSON<sup>#</sup> signal. Logic LOW on this pin by itself should not turn on the power outputs.

| Signal Type (Input Signal to Supply)                                         | Accepts a ground input from the system. Pull-up to VSB located in the power supply. |        |  |

|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--------|--|

| $PSKILL = Low, PSON^{\#} = Low$                                              | ON                                                                                  |        |  |

| PSKILL = Open, PSON <sup>#</sup> = Low or Open                               | OFF                                                                                 |        |  |

| PSKILL = Low, PSON <sup>#</sup> = Open                                       | OFF                                                                                 |        |  |

|                                                                              | Min.                                                                                | Max.   |  |

| Logic level low (power supply ON)                                            | 0 V                                                                                 | 1.0 V  |  |

| Logic level high (power supply OFF)                                          | 2.0 V                                                                               | 5.25 V |  |

| Source current, Vpskill = low                                                |                                                                                     | 4 mA   |  |

| Delay from PSKILL=High to power supply<br>turned off (T <sub>PSKill</sub> )† | 100 ?sec                                                                            |        |  |

#### Table 3-17: PSKILL Signal Characteristics

#### Notes:

† T<sub>PSKill</sub> is the time from the PSKILL signal deasserting HIGH to the power supply's output inductor.

#### 3.5.7.4 Power Supply Failure (FAIL)

In the event of a power supply failure (OVP at any output, UV at any output, fan failure, or other failure), this signal is allowed to go HIGH by the power supply.

| Table 3 | 3-18: | FAIL | Signal | Characteristics |

|---------|-------|------|--------|-----------------|

|---------|-------|------|--------|-----------------|

| Signal Type                           | Open collector/drain output from power supply. Pull-up to VSB located system. |          |  |

|---------------------------------------|-------------------------------------------------------------------------------|----------|--|

| FAIL = High                           | Failed                                                                        |          |  |

| FAIL = Low                            | ОК                                                                            |          |  |

|                                       | Min.                                                                          | Max.     |  |

| Logic level low voltage, Isink=4mA    | 0 V                                                                           | 0.4 V    |  |

| Logic level high voltage, Isink=50? A |                                                                               | 5.25 V   |  |

| Sink current, FAIL = low              |                                                                               | 4 mA     |  |

| Sink current, FAIL = high             | 50 ? A                                                                        |          |  |

| FAIL rise and fall time               |                                                                               | 100 ?sec |  |

### 3.5.7.5 Predictive Failure Signal (PRFL)

This signal indicates that the power supply (or power supply fan) is reaching its end of life. The signal indicates a predictive failure when HIGH.

#### Table 3-19: PRFL Signal Characteristics

| Signal Type (Active Low)              | Open collector/drain output from power supply. Pull-up to VSB located in system. |          |  |  |

|---------------------------------------|----------------------------------------------------------------------------------|----------|--|--|

| PRFL = High                           | Failing                                                                          | Failing  |  |  |

| PRFL = Low                            | ОК                                                                               |          |  |  |

|                                       | Min.                                                                             | Max.     |  |  |

| Logic level low voltage, lsink=4mA    | 0 V                                                                              | 0.4 V    |  |  |

| Logic level high voltage, lsink=50? A |                                                                                  | 5.25 V   |  |  |

| Sink current, FAIL = low              | 4 mA                                                                             |          |  |  |

| Sink current, FAIL = high             | 50 ? A                                                                           |          |  |  |

| PRFL rise and fall time               |                                                                                  | 100 ?sec |  |  |

#### 3.5.7.6 Power Supply Present Indicator (PRESENT)

The PRESENT<sup>#</sup> signal is used to sense the number of power supplies in the system (operational or not). This signal is connected to the power supply's output ground.

| Signal Type                               | Output from power supply that is connected to ground.<br>Pull-up to VSB located in system. |        |  |  |

|-------------------------------------------|--------------------------------------------------------------------------------------------|--------|--|--|

| PRESENT <sup>#</sup> = Low                | Present                                                                                    |        |  |  |

| PRESENT <sup>#</sup> = High               | Not Present                                                                                |        |  |  |

|                                           | Min.                                                                                       | Max.   |  |  |

| Logic level low voltage, Isink=4mA        | 0 V                                                                                        | 0.4 V  |  |  |

| Logic level high voltage, Isink=50? A     |                                                                                            | 5.25 V |  |  |

| Sink current, PRESENT <sup>#</sup> = low  |                                                                                            | 4 mA   |  |  |

| Sink current, PRESENT <sup>#</sup> = high |                                                                                            | 50 ? A |  |  |

#### 3.5.7.7 Power Supply FANC

The requirements for the FANC signal are similar to that of the ATX specification.

The FANC signal is a fan speed and sleep mode control signal. The fan speed and sleep mode are controlled by a variable voltage on this pin. This signal allows the system to request control of the power supply fan. The control circuit in the system supplies voltage to this pin from 12 VDC to 0 VDC for the fan control request. If the FANC signal is left open, the fan control defaults to power supply control.

| Signal Type       | Accepts an input voltage from the system. Pull-up to 12 V located in power supply. |      |  |

|-------------------|------------------------------------------------------------------------------------|------|--|

| FANC < 1V         | Fan in SLEEP mode (see note 1)                                                     |      |  |

| 2V < FANC < 3V    | Fan in LOW speed (see note 1)                                                      |      |  |

| 3V < FANC < 10.5V | Fan ramps from LOW to HIGH speed (see note 1)                                      |      |  |

| FANC > 10.5V      | Fan in HIGH speed (see note 1)                                                     |      |  |

|                   | Min.                                                                               | Max. |  |

| Source current                           | 2 mA |

|------------------------------------------|------|

| Fan SLEEP mode output power (see note 2) | 50 W |

| Fan LOW speed ambient temperature        | 35?C |

Notes:

1. This is a request from the system to the power supply to operate the fan at this condition. The power supply can override this request and increase the fan speed if the power supply requires more cooling. 2. When the power supply fan is in SLEEP mode the fan must be operating at its minimum RPM, which is slow enough to not output any noticeable audible levels. The power supply must be able to supply 0 W to 50 W of output power at 50?C ambient (any combinations of 3.3 V, 5 V, and 12 V output currents) in the power supply fan SLEEP mode condition without the power supply overriding and turning the fan to LOW or HIGH speed.

#### 3.5.7.8 Power Supply Field Replaceable Unit (FRU) Signals

The FRU data format is compliant with the IPMI specifications. Four pins will be allocated for the FRU information on the power supply connector. One pin is the Serial Clock (SCL). The second pin is used for Serial Data (SDA). Both pins are bi-directional and are used to form a serial bus. Pins three and four are address lines A0 and A1 and indicate to the power supply's EEPROM which position the power supply is located in, in the system.

| A0   | A1   | Address |  |  |

|------|------|---------|--|--|

| Low  | Low  | 0xA0    |  |  |

| Low  | High | 0xA2    |  |  |

| High | Low  | 0xA5    |  |  |

| High | High | 0xA6    |  |  |

The FRU circuits inside the power supply are powered off of 5 VSB on the system side of the OR'ing device and grounded to ReturnS (remote sense return). The write control (or write protect) pin should be tied to ReturnS inside the power supply so that information can be written to the EEPROM.

## 3.5.8 LED Indicators

The green power LED (PWR) blinks to indicate that AC is applied to the PSU and standby voltages are available. This same LED should go solid to indicate that all the power outputs are available. There is an amber Power Supply Fail LED to indicate that the power supply has failed and replacement of the unit is necessary. There is an amber Predictive Fail LED to indicate that the power supply is about to fail in the near future due to a poorly performing fan. This LED should be blinking to indicate the predictive failure condition and should be latched into a blinking state once the condition has occurred. This latch can be cleared by toggling the PSON<sup>#</sup> signal or by an AC power interruption of greater than 15 seconds. Refer to Table 3-22 for conditions of the LEDs.

|                        | Power Supply LEDs                      |         |          |  |

|------------------------|----------------------------------------|---------|----------|--|

| Power Supply Condition | Power LED Predictive Fail LED Fail LED |         | Fail LED |  |

|                        | (Green)                                | (Amber) | (Amber)  |  |

| No AC power to all PSU | OFF                                    | OFF     | OFF      |  |

#### Table 3-22: LED Indicators

|                                   | Power Supply LEDs    |                                |                     |  |

|-----------------------------------|----------------------|--------------------------------|---------------------|--|

| Power Supply Condition            | Power LED<br>(Green) | Predictive Fail LED<br>(Amber) | Fail LED<br>(Amber) |  |

| No AC power to this PSU only      | OFF                  | OFF                            | ON                  |  |

| AC present/standby outputs on     | Blinking             | OFF                            | OFF                 |  |

| Power supply DC outputs ON and OK | ON                   | OFF                            | OFF                 |  |

| Power supply failure              | OFF                  | OFF                            | ON                  |  |

| Current limit                     | ON                   | OFF                            | Blinking            |  |

| Predictive failure                | ON                   | Blinking/Latched               | OFF                 |  |

The LEDs are visible on the power supply's exterior face. The appearance of three LEDs is in the following order from left to right as viewed in Figure 3-2: Power, Predictive Fail, Fail.

|                                                    | Power Supply LEDs |                      | Power Supply Output Signal States |                           |                                       | Input to P.S.                 |                               |

|----------------------------------------------------|-------------------|----------------------|-----------------------------------|---------------------------|---------------------------------------|-------------------------------|-------------------------------|

| Conditions                                         | PWR<br>(Green)    | PRFL<br>(Amber)      | FAIL<br>(Amber)                   | P_Good<br>H = Pwr<br>good | Pred. Failure<br>H = Pred.<br>failure | P.S. Failure<br>H = P.S. Fail | P.S. On<br>L = P.S.<br>Enable |

| No AC power                                        | OFF               | OFF                  | OFF                               | L                         | L                                     | Н                             | L                             |

| No AC power to this PSU only                       | OFF               | OFF                  | ON                                |                           |                                       | Н                             | L                             |

| AC in/standby<br>on/PS off                         | Blinking          | OFF                  | OFF                               | L                         | L                                     | L                             | L                             |

| DC outputs OK                                      | ON                | OFF                  | OFF                               | Н                         | L                                     | L                             | L                             |

| Power supply<br>failure (including<br>OVP and OTP) | OFF               | OFF                  | ON                                | L                         | L                                     | Н                             | Н                             |

| Current limit<br>(Including OCP<br>and Short)      | ON                | OFF                  | Blinking                          | L                         | L                                     | Н                             | L                             |

| Predictive failure                                 | ON                | Blinking<br>/Latched | OFF                               | Н                         | Н                                     | L                             | L                             |

The Power LED (green), the Predictive Failure LED (amber), and the Power Supply Failure LED (amber) are marked or labeled near the LEDs with the following markings.

The Power LED is labeled as **PWR**.

The Predictive Failure LED is labeled as PRFL.

The Power Supply Failure LED is labeled as FAIL.

< This page intentionally left blank. >

# 4. Power Distribution Board

The SPKA4 MP server system power supplies plug into a power distribution board. This board provides the interconnections between the supplies, the server management interface, and a power converter to provide a controlled voltage for the system fans.

## 4.1 Introduction

This section describes the feature set of the SPKA4 MP server system power distribution board (PDB). The PDB is used in the chassis to provide connectivity, system fan voltage, and server management features for one, two and three power supply configurations. The two and three supply configurations allow for "one plus one" and "two plus one" redundant power systems respectively.

### 4.1.1 Feature Overview

- ?? Supports single, dual and triple power supply solutions for powering the chassis.

- ?? Supports server management:

- Power supply Field Replaceable Unit (FRU) information access.

- Predictive failure monitoring.

- Power supply presence.

- Peripheral voltage monitoring.

- Chassis fan speed control.

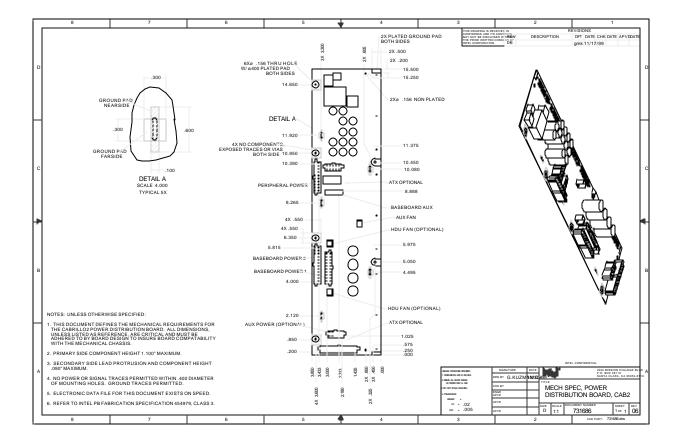

## 4.2 Physical Description

The printed circuit board has the dimensions, mounting hole placements, and connector placements as shown in the mechanical specification. The board has external dimensions of 15.5" X 3.85".

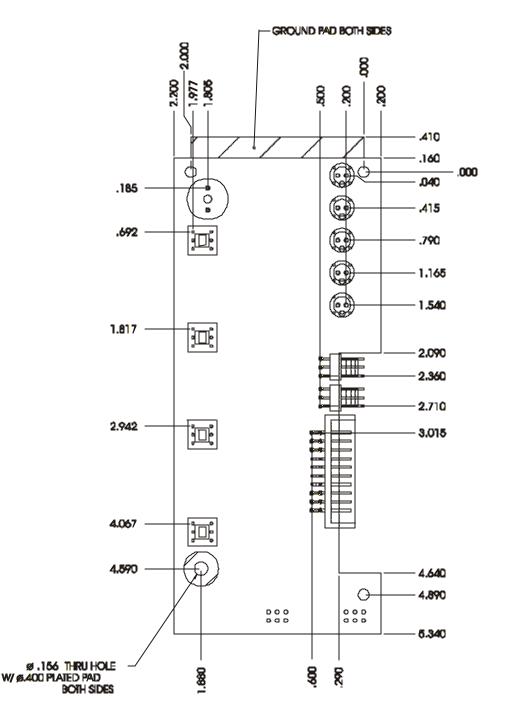

Figure 4-1: Power Distribution Board Diagram

### 4.2.1 Location

The power distribution board is located in the base of the chassis. Right angle connectors on the PDB allow for blind mating of three power supply connectors. Outputs are provided for power delivery to high performance mid-range server boards, and chassis components.

## 4.3 Electrical Connections

Connectors on the Power Distribution Board include the following:

- ?? Power supply connectors.

- ?? Baseboard power connectors.

- ?? Baseboard auxiliary connector.

- ?? Peripherals.

## 4.4 Power Supply Connectors

| Signal Pins |               |     |                                                                                                                                                    |        |          |       |         |          |         |        |      |          |          |

|-------------|---------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------|-------|---------|----------|---------|--------|------|----------|----------|

|             |               |     | 1                                                                                                                                                  | 2      |          |       | 3       |          | 4       | Ę      | 5    |          | 6        |

| D           | D -12V        |     | RS GN                                                                                                                                              | D      | Reserved |       | Resei   | Reserved |         | PWR OK |      | +12V LSS |          |

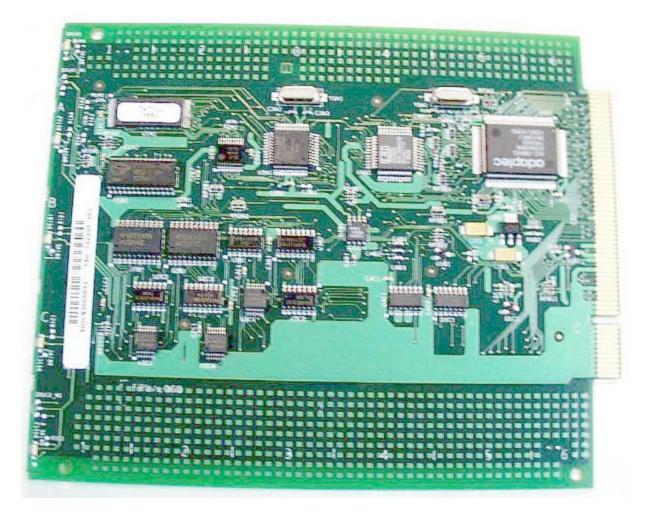

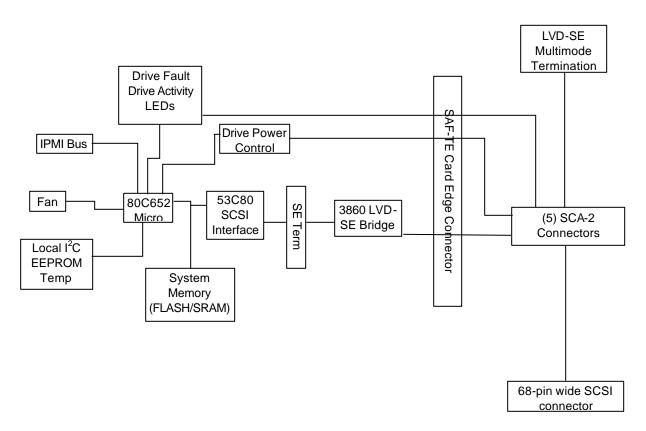

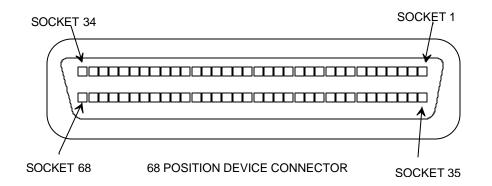

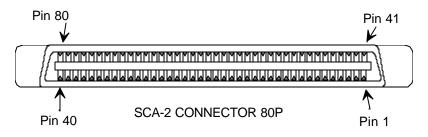

| С           |               | Res | served                                                                                                                                             | RS +12 | V        | PRDC  | CT FAIL | FAIL     |         | I2C SC | CL   | A1       |          |