# **OPRF100 MP Board Set**

Supporting Up To Eight Intel<sup>®</sup>

Pentium<sup>®</sup> III Xeon<sup>™</sup> Processors

# **Technical Product Specification**

Intel Order #753673-001 Revision 1.0

### Revision History

| Date         | Rev. | Modifications    |

|--------------|------|------------------|

| August, 1999 | 1.0  | Initial release. |

|              |      |                  |

### **Disclaimers**

Except as provided in Intel's Terms and Conditions of Sale for such products, INTEL DISCLAIMS ALL LIABILITIES AND WARRANTIES (EXPRESS, IMPLIED OR OTHERWISE) ASSOCIATED WITH THE INFORMATION CONTAINED WITHIN THIS DOCUMENT, OR FOR ANY PRODUCTS OR DEVICES REFERRED TO HEREIN, INCLUDING, WITHOUT LIMITATION, LIABILITY FOR INFRINGEMENT OF ANY PROPRIETARY RIGHTS RELATING TO THIS DOCUMENT, OR ANY PRODUCTS OR DEVICES REFERENCED HEREIN, OR FOR THE IMPLEMENTATION OF INFORMATION IN THIS DOCUMENT INTEL IS NOT OBLIGATED TO PROVIDE ANY SUPPORT, INSTALLATION, OR OTHER ASSISTANCE WITH REGARD TO THESE DEVICES, NOR ANY UPDATES, CORRECTIONS OR MODIFICATIONS TO THIS DOCUMENT OR THE INFORMATION CONTAINED HEREIN.

THE INTEL® PRODUCT REFERRED TO IN THIS DOCUMENT IS INTENDED FOR STANDARD COMMERCIAL USE ONLY. CUSTOMERS ARE SOLELY RESPONSIBLE FOR ASSESSING THE SUITABILITY OF THE PRODUCT AND/OR DEVICES FOR USE IN PARTICULAR APPLICATIONS. THE REFERENCED INTEL PRODUCT IS NOT INTENDED FOR USE IN CRITICAL CONTROL OR SAFETY SYSTEMS OR IN NUCLEAR FACILITY APPLICATIONS. INTEL PRODUCTS ARE NOT INTENDED FOR USE IN MEDICAL, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS.

Information in this document is provided in connection with Intel products. This document is provided "as is" with no warranties whatsoever. Intel specifically disclaims any implied or express warranties of any kind whatsovever, associated with this document, including without limitation: (i) liability for infrinement of any proprietary rights (including without limitation, any intellectual property right), merchantability, fitness for any particular purpose, or any warranty otherwise arising out of any product or testing proposal, specification or sample; (ii) sufficiency, reliability, accuracy, completeness or usefulness of same, and (iii) ability or sufficiency of same to function accurately as a representation of any standard. No license, express, implied, or otherwise, to any intellectual property rights is granted by this document or by the sale of Intel products. Furthermore, Intel makes no commitment to update the information contained in this document or any test report, provided that Intel may make changes to this document, the test reports, specifications and product descriptions at any time, without notice.

Third parties may have intellectual property rights which may be relevant to this document and the technologies discussed herein, accordingly the reader is advised to seek the advice of competent counsel, as required withhout obligation to Intel.

Only approved software drivers and accessories that are recommended for the revision number of the boards and system being operated should be used with Intel products. Please note that, as a result of warranty repairs or replacements, alternate software and firmware versions may be required for proper operation of the equipment.

The hardware vendor remains solely responsible for the design, sale and functionality of its product, including any liability arising from product infringement or product warranty.

The **OPRF100 MP Board Set** and the **OCPRF100 MP Server System** product may contain design defects or errors known as errata that may cause the product to deviate from published specifications. Current characterized errata are available on request.

I<sup>2</sup>C is a two-wire communications bus/protocol developed by Philips. SMBus is a subset of the I<sup>2</sup>C bus/protocol and was developed by Intel. Implementations of the I<sup>2</sup>C bus/protocol or the SMBus bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

Copyright © 1999 Intel Corporation.

\*Other brands and names are the property of their respective owners.

## Conventions and Terminology

This document uses the following terms and abbreviations:

| Term                  | Definition                                                                |

|-----------------------|---------------------------------------------------------------------------|

| ACPI                  | Advanced Configuration and Power Interface.                               |

| ASIC                  | Application Specific Integrated Circuit.                                  |

| Asserted              | Logic "Truth." The "1" or active state. Active LOW signals end with "_L". |

| ATE                   | Automated Test Equipment.                                                 |

| BIOS                  | Basic Input-Output System.                                                |

| BitBLT                | Bit Boundary Block Transfer.                                              |

| ВМС                   | Bus Management Controller, interfaces to SMIC and IPMB.                   |

| De-asserted           | Logic "False." The "0" or non-active state.                               |

| DFM                   | Design For Manufacturability.                                             |

| DFT                   | Design For Testability.                                                   |

| DIB                   | Data Interface Buffer.                                                    |

| DIMM                  | Dual Inline Memory Module.                                                |

| DWORD                 | Double Word. A 32-bit quantity.                                           |

| ECC                   | Error Checking and Correcting.                                            |

| EEPROM                | Electrically Erasable Programmable Read-Only Memory.                      |

| EMP                   | Emergency Management Port.                                                |

| FPC                   | Front Panel Controller.                                                   |

| FRU                   | Field Replaceable Unit.                                                   |

| FSB                   | Front Side Bus.                                                           |

| GTL+                  | Gunther Transceiver Logic.                                                |

| HDM                   | High Density Metric.                                                      |

| I <sup>2</sup> C* Bus | Two wire bi-directional serial bus, used as the carrier for IPMB.         |

| ICMB                  | Intelligent Chassis Management Bus.                                       |

| IDE                   | Integrated Drive Electronics, an interface to drives and storage devices. |

| IPMB                  | Intelligent Platform Management Bus.                                      |

| IPMI                  | Intelligent Platform Management Interface.                                |

| IRQ                   | Interrupt Request.                                                        |

| ISA                   | Industry Standard Architecture.                                           |

| ISP   | In-System Programming.                                                                                               |  |

|-------|----------------------------------------------------------------------------------------------------------------------|--|

| ITP   | In Target Probe.                                                                                                     |  |

| JTAG  | Joint Test Action Group. Defined the IEEE standard test access port and boundary scan architecture: IEEE Std 1149.1. |  |

| KB    | Kilobyte. 1024 bytes.                                                                                                |  |

| LFM   | Linear Feet per Minute.                                                                                              |  |

| LSB   | Least Significant Bit.                                                                                               |  |

| LVDS  | Low Voltage Differential SCSI.                                                                                       |  |

| MAC   | Memory Access Controller.                                                                                            |  |

| MB    | Megabyte.                                                                                                            |  |

| MB/s  | Megabytes per second.                                                                                                |  |

| MTBF  | Mean Time Between Failures.                                                                                          |  |

| NIC   | Network Interface Card.                                                                                              |  |

| NMI   | Non-Maskable Interrupt.                                                                                              |  |

| ОС    | Open Collector.                                                                                                      |  |

| OCP   | Over Current Protection.                                                                                             |  |

| OEM   | Original Equipment Manufacturer.                                                                                     |  |

| OVP   | Over Voltage Protection.                                                                                             |  |

| PAL   | Programmable Array Logic.                                                                                            |  |

| PCC   | Power Control Circuitry.                                                                                             |  |

| PCI   | Peripheral Component Interconnect. The I/O expansion bus.                                                            |  |

| PID   | Programmable Interrupt Device.                                                                                       |  |

| PLD   | Programmable Logic Device.                                                                                           |  |

| PMM   | Processor Memory Module.                                                                                             |  |

| PS    | Power Supply.                                                                                                        |  |

| RAS   | Reliability, Availability, Serviceability.                                                                           |  |

| RTC   | Real Time Clock.                                                                                                     |  |

| RXD   | Received.                                                                                                            |  |

| SCI   | System Control Interrupt.                                                                                            |  |

| SCSI  | Small Computer Systems Interface, typically used for storage devices.                                                |  |

| SECC  | Single Edge Connector Cartridge.                                                                                     |  |

| SEL   | System Event Log.                                                                                                    |  |

| SMBus | System Management Bus.                                                                                               |  |

| SMI   | Server Management Interrupt.                                                                                         |  |

| SMIC | Server Management Interface Controller.             |

|------|-----------------------------------------------------|

| SMM  | Server Management Module or System Management Mode. |

| SMUX | SDRAM Multiplexer.                                  |

| SPD  | Serial Presence Detect.                             |

| SPI  | Serial Parallel Interface.                          |

| TTL  | Transistor-Transistor Logic.                        |

| TXD  | Transmitted.                                        |

| USB  | Universal Serial Bus.                               |

| VID  | Voltage ID.                                         |

| VMC  | Voltage Management Controller.                      |

| WOL  | Wake-On-LAN*.                                       |

### References

Refer to the following documents for additional information:

- Advanced Configuration And Power Interface Specification, Revision 1.0, 22 December 1996, http://www.teleport.com/~acpi.

- Errata to the Advanced Configuration and Power Interface Specification, Revision 1.0, http://www.teleport.com/~acpi.

- ACPI Implementor's Guide, v. 0.50, http://www.teleport.com/~acpi.

- *PC Registered DIMM Specification*, Revision 1.0, <a href="http://developer.intel.com/design/pcisets/memory/index.htm">http://developer.intel.com/design/pcisets/memory/index.htm</a>.

- Pentium® Pro Family Developer's Manual, Volume 1: Specifications. http://developer.intel.com/design/pro/manuals/index.htm.

- 82371AB PCI-TO-ISA/IDE Xcelerator (PIIX4) Data Sheet, April, 1997, Intel Corporation, number 290562-001, ftp://download.intel.com/design/pcisets/datashts/29056201.pdf.

- PC Serial Presence Detect Specification, http://developer.intel.com/design/pcisets/memory/index.htm.

# **Table of Contents**

| Introduction                                  | 1-1   |

|-----------------------------------------------|-------|

| Architecture Overview                         | . 1-2 |

| Board Set Overview                            | . 1-3 |

| I/O Bus Support                               | . 1-7 |

| Component Details                             | . 1-7 |

| Microprocessor                                | . 1-7 |

| Profusion* PCIset                             | . 1-8 |

| Programmable Interrupt Device (PID)           | . 1-9 |

| Performance                                   | . 1-9 |

| OPRF100 I/O Carrier                           | 2-1   |

| Architectural Overview                        | . 2-1 |

| I/O Bus Interface                             | . 2-2 |

| PCI Bus A                                     | . 2-2 |

| PCI Bus B                                     | . 2-3 |

| PCI Bus C                                     | . 2-3 |

| PCI Bus D                                     | . 2-3 |

| Server Management Logic                       | . 2-4 |

| A450NX I/O Riser Board                        | . 2-4 |

| Major Component Reference Tables              | . 2-4 |

| Connector Signal Descriptions                 | . 2-5 |

| I/O Connector Signals                         | . 2-6 |

| PCI Signal Descriptions                       | 2-13  |

| SCSI Signal Descriptions                      | 2-15  |

| ISA Signal Descriptions                       | 2-16  |

| IDE Signal Descriptions                       |       |

| Server Monitor Module Feature Connector (SFC) | 2-18  |

| Auxiliary I2C* Connectors                     |       |

| Wake-On-LAN* Connector                        |       |

| Functional Architecture                       | 2-21  |

| I/O Connector                                 | 2-21  |

| GTL+ I/O Bus Interface                        |       |

| PCI Bridge (PB64)                             | 2-22  |

| PCI Bus A                                     | 2-22  |

| PCI Bus B                                     | 2-25  |

| PCI Bus C                                     |       |

| PCI Bus D                                     | 2-30  |

| ISA Bus                                       |       |

| Wake-On-LAN*                                  |       |

| Server Management                             |       |

| Programmable Logic Devices                    |       |

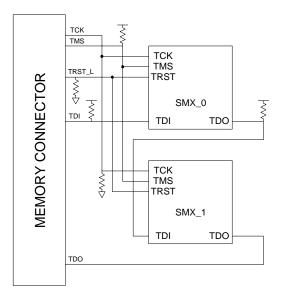

| Boundary Scan                                 |       |

| Board Configuration Switches                  |       |

| Clock Distribution                            |       |

| Reset Sequence                                |       |

| Boot Order                                    | 2-69  |

| Mechanical Specifications                 | 2-70 |

|-------------------------------------------|------|

| I/O Bus Connector                         |      |

| PCI Connectors (64-bit)                   |      |

| SCSI Connector                            |      |

| IDE Connector                             |      |

| Floppy Disk Port Connection               |      |

| USB Connector                             |      |

| I2C* Feature Connector Pin Assignments    |      |

| I2C* Connector                            |      |

| Legacy Connections                        |      |

| PHP LED/Switch Connector                  |      |

| Voltage Tolerances                        |      |

| OPRF100 Profusion* Carrier                |      |

| Introduction                              |      |

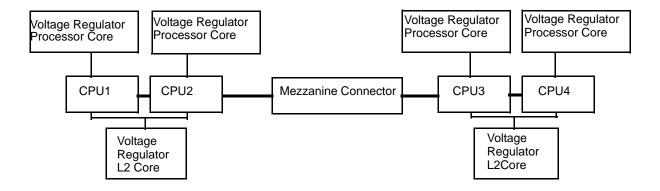

| Block Diagram                             |      |

| Architectural Overview                    |      |

|                                           |      |

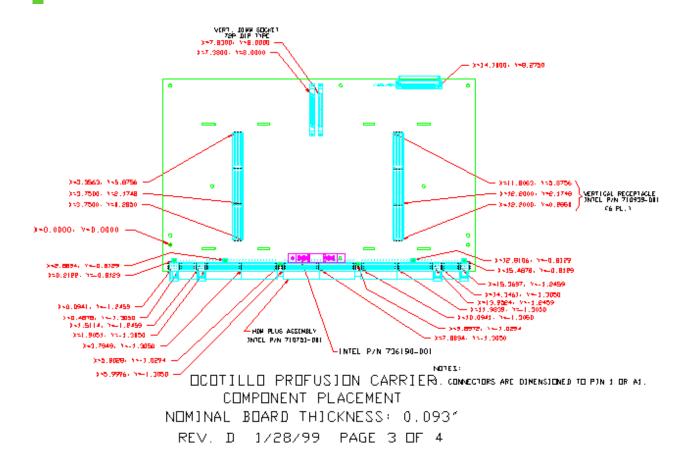

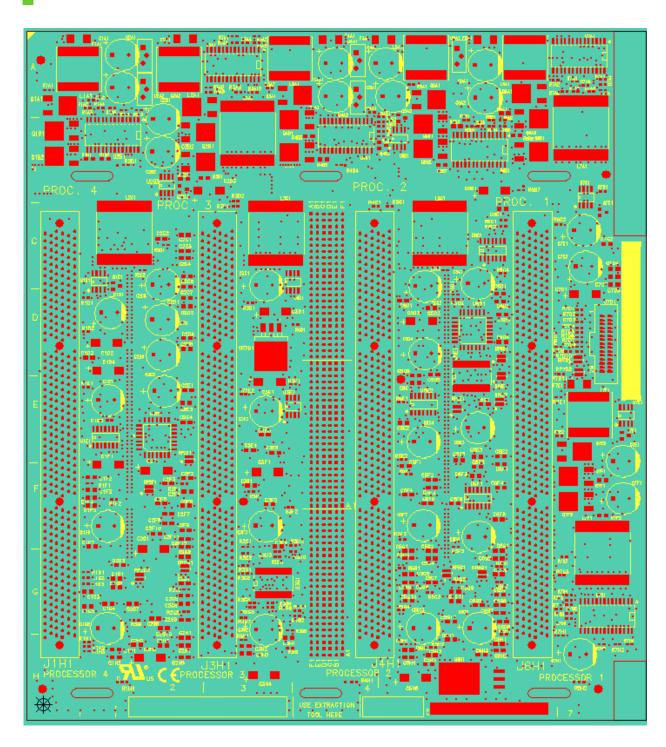

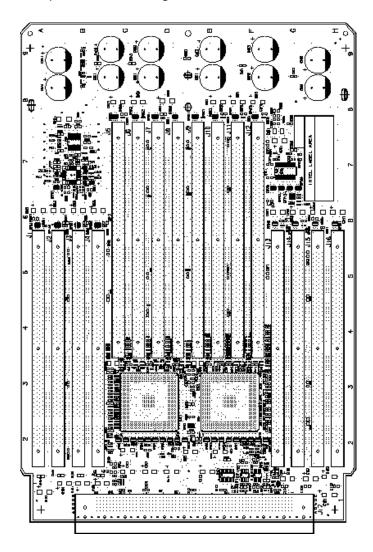

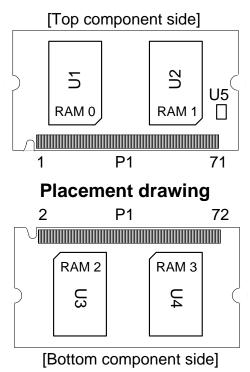

| Placement Diagram                         |      |

| Functional Architecture                   |      |

| Front-side Bus (FSB)                      |      |

| Memory Interface                          |      |

| I/O Bus Interface                         |      |

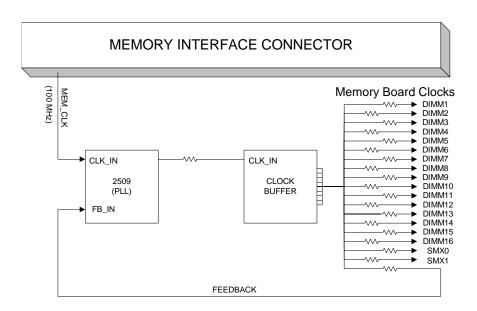

| Clock Generation                          |      |

| System Management Interface               |      |

| Voltage Regulators                        |      |

| Board Configuration Jumpers               |      |

| Signal Descriptions                       |      |

| Memory Interface Signals                  |      |

| I/O Connector Signals                     |      |

| Front Panel Interface Signals             |      |

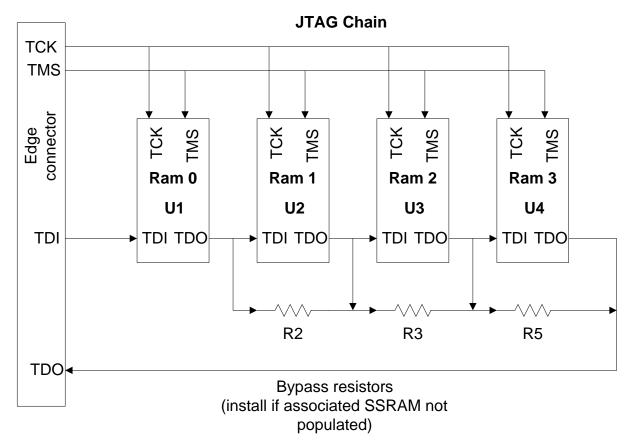

| JTAG Scan Interface Signals               |      |

| Coherency DIMM Interface Signals          |      |

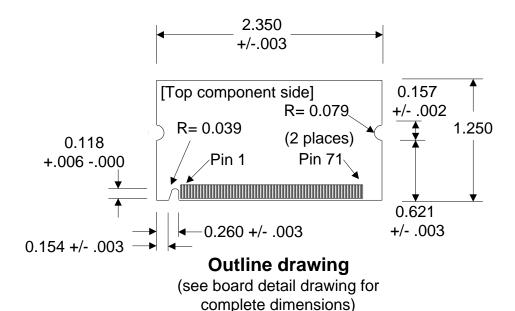

| Mechanical Specifications                 |      |

| Connector Specifications                  |      |

| Mechanical Specifications                 |      |

| OPRF100 Processor Mezzanine Board         |      |

| Introduction                              |      |

| Architectural Overview                    |      |

| Placement Diagram                         |      |

| Signal Descriptions                       |      |

| Mezzanine Connector Interface Bus Signals |      |

| Specifications                            |      |

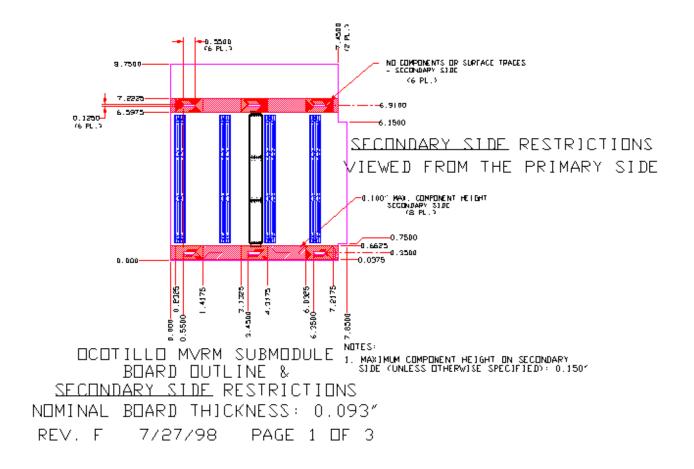

| Mechanical Specifications                 |      |

| OPRF100 Memory Carrier                    |      |

| Introduction                              |      |

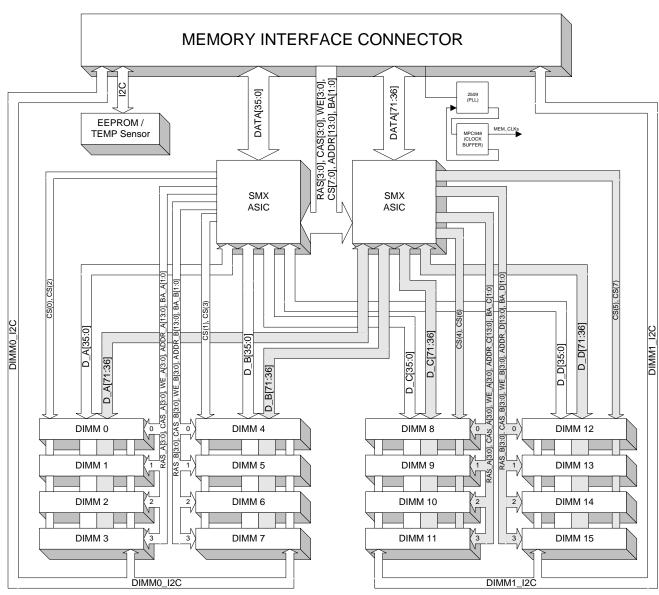

| Block Diagram                             |      |

| Memory Carrier Clock Distribution Diagram |      |

| Architectural Overview                    | 5-3  |

| Placement Diagram                         |      |

| Functional Description                    | 5-5  |

| SDRAM Array                               | 5-5  |

| Mechanical Specifications                  | . 7-9 |

|--------------------------------------------|-------|

| Electrical Specifications                  | 7-10  |

| Voltage Tolerances                         | 7-12  |

| Board Set Specifications                   |       |

| Power Requirements                         | . 8-1 |

| Min/Max Current Ratings                    |       |

| Absolute Maximum Ratings                   | . 8-7 |

| Voltage Timing and Sequencing              | . 8-7 |

| Interfacing Requirements                   |       |

| Power Sub-System Timing Specifications     |       |

| Thermal Requirements                       |       |

| Board Level Environmental Specifications   |       |

| Regulatory Compliance                      |       |

| OPRF100 BIOS Specifications                | 9-1   |

| System Hardware                            |       |

| Processors                                 |       |

| Profusion* Chip Set                        | . 9-3 |

| I/O Subsystem                              |       |

| Intelligent Platform Management Bus (IPMB) | . 9-4 |

| Industry Standards                         |       |

| ACPI                                       | . 9-4 |

| Boot Devices and Peripherals               | . 9-5 |

| Management                                 | . 9-6 |

| Configuration                              |       |

| System BIOS                                | . 9-7 |

| Ease of Use                                | . 9-8 |

| Reliability, Availability, Serviceability  | 9-21  |

| Manageability                              | 9-30  |

| Security                                   | 9-35  |

| Customization                              | 9-38  |

| BIOS Setup Utility                         | 9-45  |

| Main Menu                                  | 9-46  |

| Advanced Menu                              | 9-50  |

| Security Menu                              | 9-53  |

| Server Menu                                | 9-54  |

| Boot Menu                                  | 9-57  |

| Exit Menu                                  | 9-58  |

| Flash Utility                              | 9-59  |

| Interactive Mode                           | 9-59  |

| Command Line Mode                          | 9-60  |

| Recovery Mode                              | 9-60  |

### Introduction 1.

This document describes the architecture, functionality, and interfaces of the OPRF100 MP board set. This board set consists of several boards including the OPRF100 Profusion\* carrier. processor mezzanine board, memory carrier, and midplane board. This board set is designed to be used in a high density rack mountable chassis and as such is designed to minimize the overall mechanical dimensions of the board set.

The OPRF100 MP board set is based on the Intel® Pentium® III Xeon™ processor and the Profusion PCIset. Both the processor and the chip set have been optimized for eight-way server applications.

### Features:

- One to eight Pentium<sup>®</sup> III Xeon<sup>™</sup> processors.

- Profusion\* PCIset.

- Support for up to 32 GB of 3.3 V SDRAM (PC-100 registered DIMMs).

- Four peer 64-bit PCI buses (two 66-MHz and two 33-MHz buses, PCI Local Bus Specification, Rev. 2.1 [PCI, Rev. 2.1] compliant).

- Ten full-length, hot-plug PCI slots—four 66 MHz and six 33 MHz.

- Onboard dual channel Symbios\* LVD SCSI controller for high performance mass storage devices.

- Onboard PCI video controller with 2-MB memory for standard server video requirements.

- IDE controller (integrated in PIIX4E).

- PIIX4E PCI to ISA bridge.

- Universal Serial Bus (USB) (integrated in PIIX4E).

- SMC\* Super I/O component to handle all PC legacy functions (keyboard, mouse, serial, parallel).

- Programmable Interrupt Device (PID), a custom Intel ASIC which provides interrupt steering and I/O APIC facilities.

- Complete built-in server management capabilities.

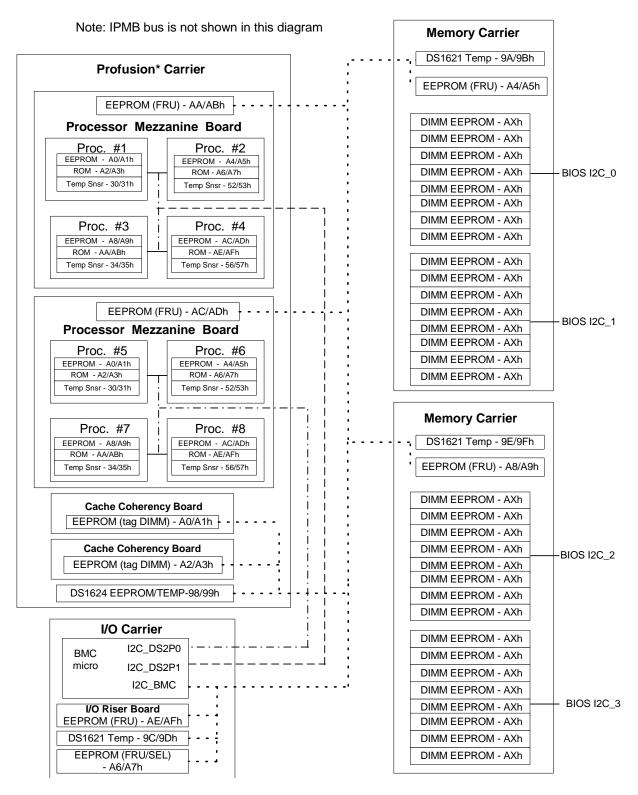

- Intelligent Platform Management Interface (IPMI) compliant for communicating information between all boards in the chassis and between chassis.

- Field replaceable unit (FRU) information and temperature sensors stored on all boards (part number, serial number, board name).

### **Document Structure and Outline**

The information contained in this document is organized into eight chapters. Each board in the OPRF100 MP board set is described in detail within its own chapter.

### Chapter 1:Introduction

Provides an architectural overview of the OPRF100 MP board set.

### Chapter 2:OPRF100 I/O Carrier

Details the I/O section of the OPRF100 MP board set.

### Chapter 3:OPRF100 Profusion\* Carrier

Details the processor section of the OPRF100 MP board set and the interface to the memory carrier and front panel.

### • Chapter 4:OPRF100 Processor Mezzanine Board

Details the processor mezzanine boards that hold up to four Pentium III<sup>®</sup> Xeon™ processors each.

### • Chapter 5:OPRF100 Memory Carrier

Details the memory section of the OPRF100 MP board set.

### • Chapter 6:OPRF100 Midplane

Details the interface between the Profusion\* carrier and the I/O carriers.

### Chapter 7:OPRF100 Cache Coherency Board

Provides information about the cache coherency board for the OPRF100 MP board set.

### • Chapter 8:OPRF100 Board Set Specifications

Provides information about board set power, thermal, and environmental specifications.

### Chapter 9:OPRF100 BIOS Specifications

Provides information about the features and functionality of the BIOS.

### 1.1 Architecture Overview

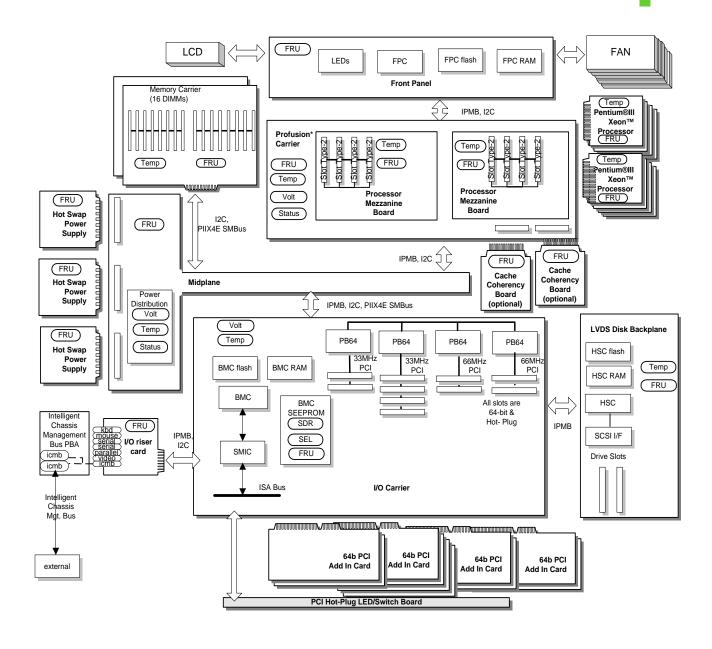

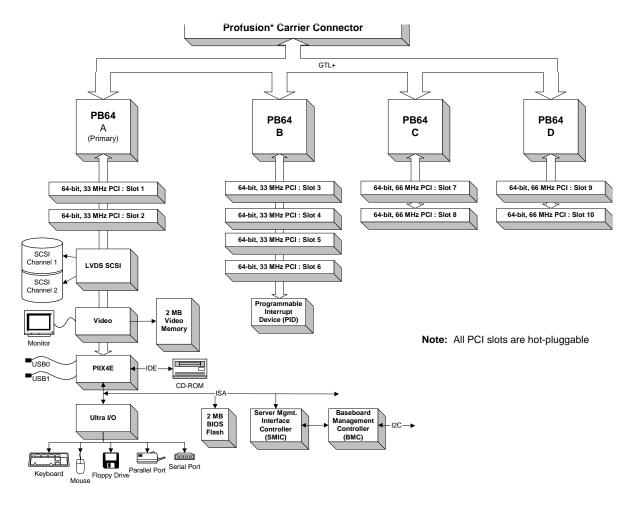

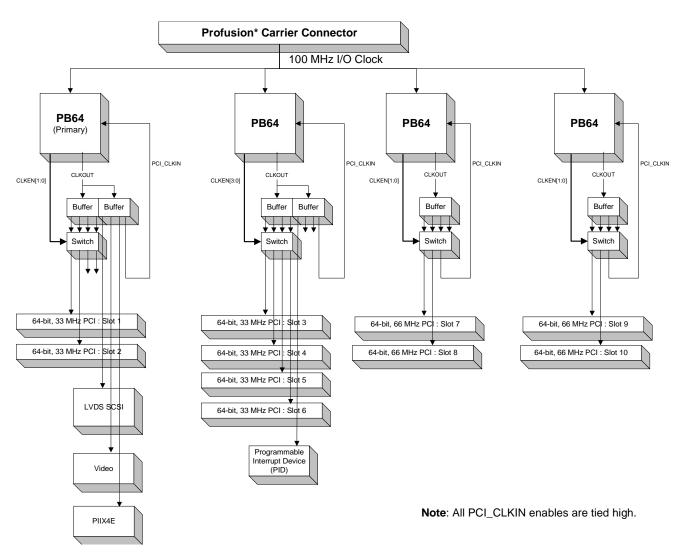

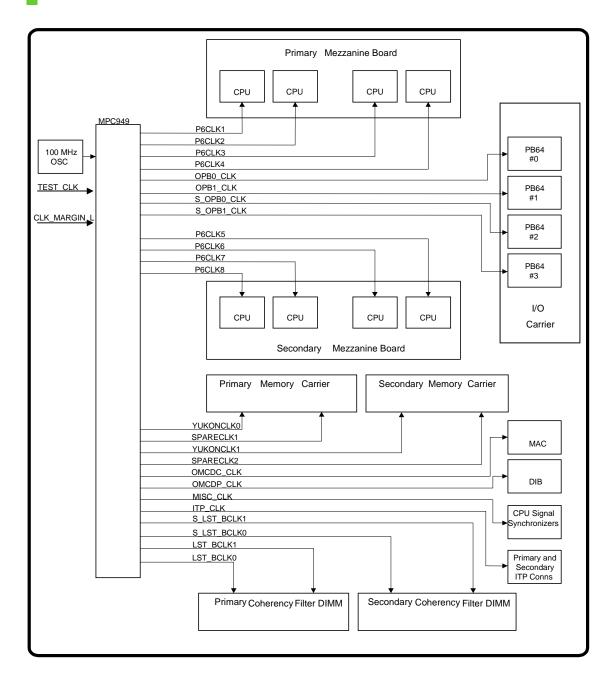

A block diagram of the OPRF100 MP board set is shown below. The following sections describe aspects of the architecture in more detail.

Figure 1-1: Block Diagram

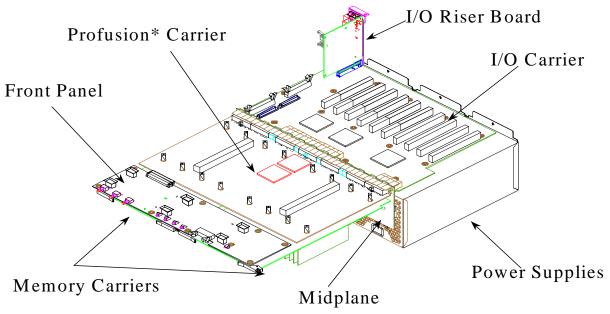

### 1.1.1 Board Set Overview

The OPRF100 MP board set is a dual baseboard design that contains a total of seven individual board designs.

- Profusion\* carrier (contains the Profusion chip set components).

- Processor mezzanine board (contains four Pentium<sup>®</sup> III Xeon<sup>™</sup> processor slots and voltage regulators). There are up to two processor mezzanine boards per system.

- I/O carrier (contains all I/O functions including PCI slots).

- I/O riser card (plugs into the I/O carrier and contains all legacy connectors: video connector, parallel port, two serial ports, keyboard and mouse connectors, and USB connectors).

- Memory carrier (16-DIMM connectors; two carriers are supported for a total of 32 GB).

- Midplane (provides connection between the I/O carrier, memory carrier, and Profusion carrier and also provides the power interface for the board set).

- Cache coherency board (maintains coherency information used by the Profusion PCIset).

The baseboards, when installed into a chassis, are connected to each other by the midplane. A 100-MHz Pentium<sup>®</sup> Pro type I/O bus of the Profusion PCIset electrically connects the two baseboards together. Power to the board set is supplied through the midplane.

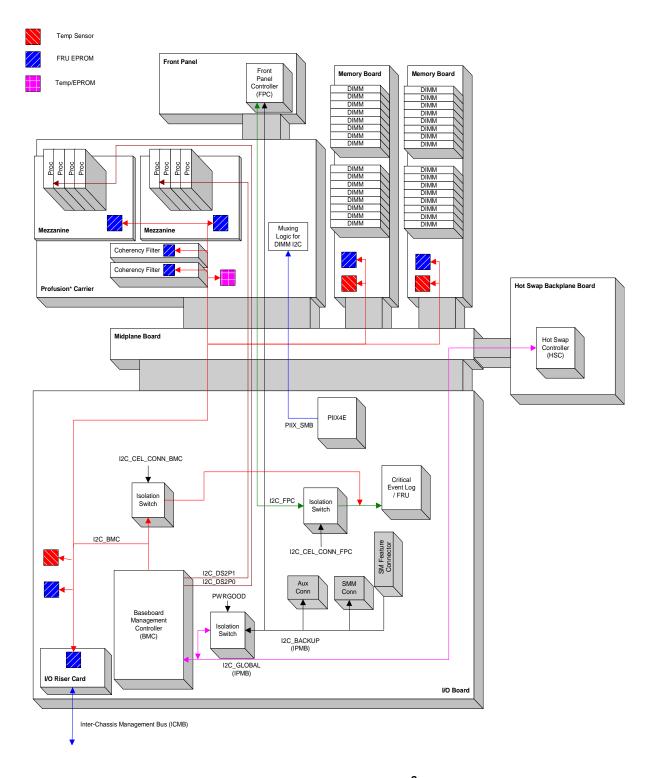

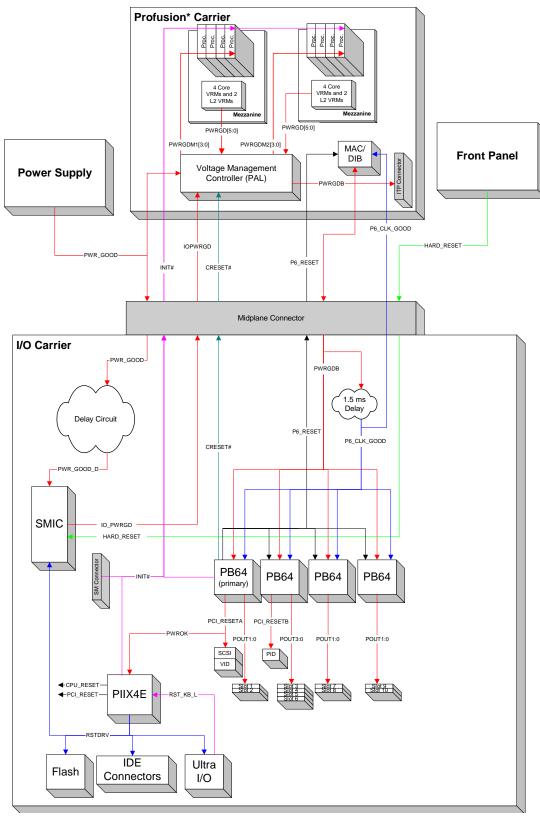

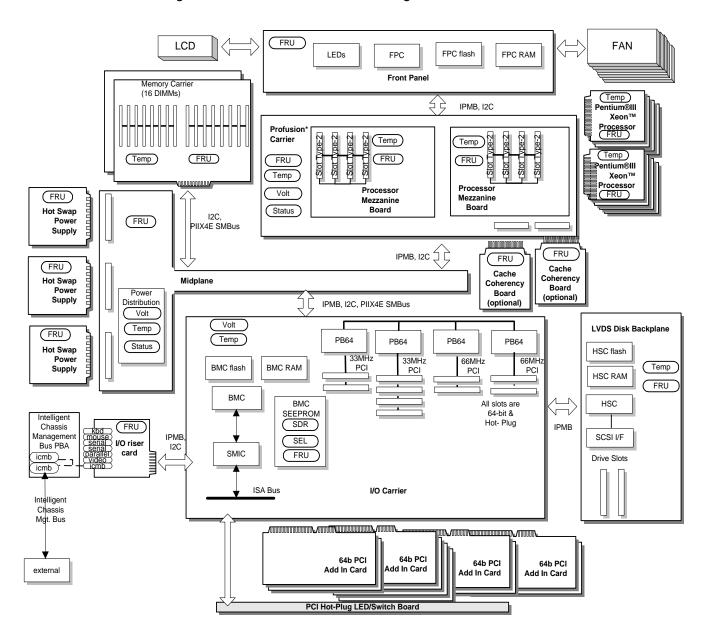

Figure 1-2: OPRF100 Board Set

### 1.1.1.1 OPRF100 Profusion\* Carrier

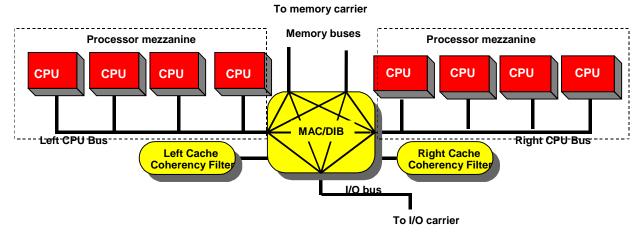

The OPRF100 Profusion carrier supports one to two OPRF100 processor mezzanine boards. Each processor mezzanine board accepts one to four processors. Each processor is packaged in a single-edge connector cartridge (SECC), which includes a 100-MHz front-side bus (FSB) interface, a processor core, and a back-side bus which operates at the frequency of the processor core and supports 512KB, 1 MB, or 2 MB of L2 cache. See the appendices of this document for more information on mixed processor steppings. Hardware support for processor fault resilient boot (FRB) is provided. A450NX processor termination modules are required for any unoccupied processor slot. The only time A450NX processor termination modules are not required is when the mezzanine is not populated with processors. Whenever a processor is installed on either mezzanine, A450NX processor termination modules are required for the unpopulated slots.

The final load on each of the two front-side buses (one from each processor mezzanine board) is the Memory Access Controller (MAC) and Data Interface Buffer (DIB) components of the Profusion PCIset. This pair of chips interfaces to the memory subsystem and I/O bus, in addition to the

front-side bus. The memory subsystem interface is equipped with connectors for two OPRF100 memory carriers. Note that the I/O bus of the Profusion PCIset is intended for connection to PB64 (PCI bus 64-bit expander bridge component of the Profusion chip set) devices. It is not designed for other uses such as connection for other processor buses or cluster connections.

Power is supplied to the processors via integrated voltage regulators. There are a total of six voltage regulators on each processor mezzanine board. Four are used to supply the processor core voltages, and two supply the L2 cache voltages.

In addition to the facilities described above, the Profusion carrier also supports the OPRF100 server management architecture by providing nonvolatile storage of baseboard and server management data, digital and analog data monitoring hardware, defective processor monitoring and disabling controls, and access to memory carrier management data. See Chapter 3 for more details on the Profusion carrier and Chapter 4 for more details on the processor mezzanine board.

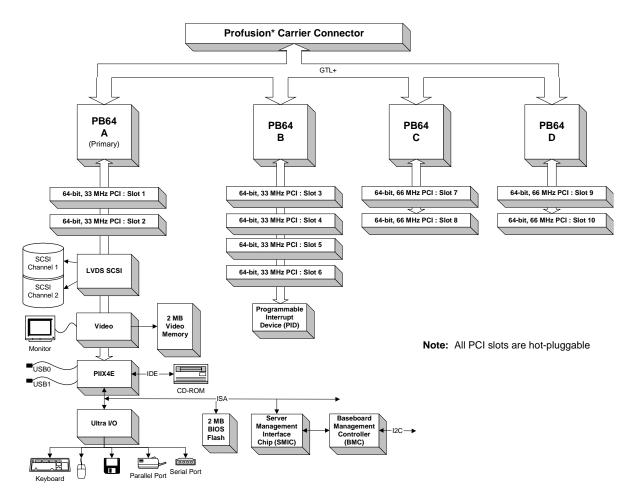

### 1.1.1.2 **OPRF100 I/O Carrier**

The OPRF100 I/O carrier provides the basis for a scaleable, high performance, high slot count I/O subsystem. Four 64-bit PCI bus segments are supported (all are peer buses) via four PB64s. Two 33-MHz (33-MHz/64-bit) segments host six PCI slots while the other two 66-MHz segments (66-MHz/64-bit) host four PCI slots for a total of 10 PCI slots in the system. All slots have hot-plug capability. Note that there is no ISA slot available.

The compatibility bus is the primary 33-MHz PCI segment that hosts the PIIX4E ISA south bridge (with one IDE interface and two USB ports), the Cirrus Logic\* 5446 VGA controller (with 2 MB of onboard video memory), the Symbios 53C896\* dual channel LVDS SCSI controller for storage device support (i.e., disks, CD-ROM, tape drive, etc.), and two 33-MHz/64-bit PCI slots. Also behind the PIIX4E is the SMC FDC37C937APM\* Super I/O component, which provides two serial ports, a parallel port, a keyboard controller and PS/2 keyboard and mouse ports, a floppy disk interface, a real time clock, and GPIOs. Note that the connectors for the serial ports, the parallel port, the video, and the PS/2 keyboard and mouse ports are provided on a separate I/O riser card (which is part of the OPRF100 MP board set). The I/O riser card plugs vertically into the I/O carrier via a card edge connector.

The secondary 33-MHz PCI segment hosts four 33-MHz/64-bit PCI slots and the PID ASIC. The PID is a custom designed ASIC that provides interrupt steering functions (including support logic for use with the 8259A\* interrupt controllers in the PIIX4E) and I/O APIC facilities. In addition to the standard IRQs, the PID supports a large number of PCI and onboard interrupt sources; a total of 64 interrupt routing table entries are available. Separate interrupt inputs will be provided for the four PCI interrupts of each PCI slot.

Each of the two 66-MHz PCI segments hosts two 66-MHz/64-bit PCI expansion slots.

In addition to the facilities described above, the I/O baseboard also implements the core of the OCPRF100 MP server system's server management architecture.

The intelligent I/O node hardware will be provided only via add-in cards with embedded I/O processors; this provides a flexible and scaleable intelligent I/O solution appropriate for a high-end server product. See Chapter 2 for more details on the I/O carrier.

### 1.1.1.3 A450NX I/O Riser Board

The A450NX I/O riser board plugs vertically into the I/O carrier and provides all of the necessary legacy connectors for video, parallel, serial, keyboard, and mouse. The Intelligent Chassis Management Bus (ICMB) connects through the I/O riser card as well. All of the connectors are located on the riser card instead of the I/O carrier because of space constraints on the I/O carrier.

### 1.1.1.4 OPRF100 Memory Carrier

The OPRF100 MP board set supports up to two memory carriers. Each carrier provides 16 sites for PC-100 registered DIMMs, supporting up to a total of 32 GB of 100-MHz 3.3 V registered SDRAM; 64-Mbit, 128-Mbit and 256-Mbit SDRAMs may be used. The minimum configuration is 128 MB of memory as implemented through installation of a single 128-MB PC-100 DIMM. The supported memory sizes range from 128 MB to 32 GB. Supported memory configurations are:

- 128, 256, 512, and 1024-MB PC-100 Registered DIMMs.

- 100 MHz SDRAM.

- Up to 32 DIMMs supported (using a total of 32 1024-MB DIMMs on both memory carriers).

- DIMMs may differ in size on a carrier but should be populated in pairs across carriers for interleaving.

The memory carrier contains a high speed SMX component to buffer and synchronize data between the SDRAMs and the Profusion PCIset. Each memory carrier can provide peak bandwidth of 800 MB/s. In order to achieve the maximum system memory bandwidth (1.6 GB/s peak), both memory carriers must be installed, and contain matched DIMMs.

The memory carrier also supports the IPMI server management architecture by providing FRU information via nonvolatile storage on the carrier. The DIMM Serial Presence Detect (SPD) EEPROM is read by BIOS via the SMBus in the PIIX4E for determination of the installed DIMM types and sizes. See Chapter 5 for more details about the memory carrier.

### 1.1.1.5 A450NX Processor Termination Module

The A450NX processor termination module provides the necessary electrical termination for the processor's front-side gunning transceiver logic+ (GTL+) bus. A450NX processor termination modules are required for any unoccupied processor slot. The only time A450NX processor termination modules are not required is when the mezzanine is not populated with processors. Whenever a processor is installed on either mezzanine, A450NX processor termination modules are required for the unpopulated slots.

### **1.1.1.6 OPRF100 Midplane**

The OPRF100 midplane provides bus interconnection between the Profusion, memory, and I/O carriers. This board also provides power distribution to the Profusion, memory, and I/O carriers

<sup>1.</sup> Contact your Intel sales representative for a listing of supported memory part numbers.

and to the peripheral bay from the three system power supply connectors. See Chapter 6 for more information on the midplane.

### 1.1.1.7 OPRF100 Cache Coherency Board

The OPRF100 cache coherency board is a high-capacity SSRAM memory board based on the Profusion PCIset. It maintains coherency information used by the chip set. The cache coherency board has been designed for use with the Profusion carrier, which has two cache coherency board connectors.

### 1.1.2 I/O Bus Support

### 1.1.2.1 **PCI Bus**

The OPRF100 MP board set provides four 64-bit PCI peer buses; two are 66 MHz and two are 33 MHz. There are a total of 10 PCI slots: four 66-MHz slots and six 33-MHz slots. All four PCI buses are compliant to the *PCI Local Bus Specification, Rev. 2.1*. The PCI buses are operated synchronously with the processor bus, using the processor bus clock as a master clock. The input clock, received over the midplane interface, is multiplied by two-thirds to support the 66-MHz PCI bus. The board set will support PCI adapters which draw power from both 3.3 V and 5 V, although the power allocation from 3.3 V may be limited. Note, the 64-bit slots will accept both 32 and 64-bit adapters. *PCI 2.1* peer to peer transfers are also supported.

### 1.1.2.2 ISA Bus

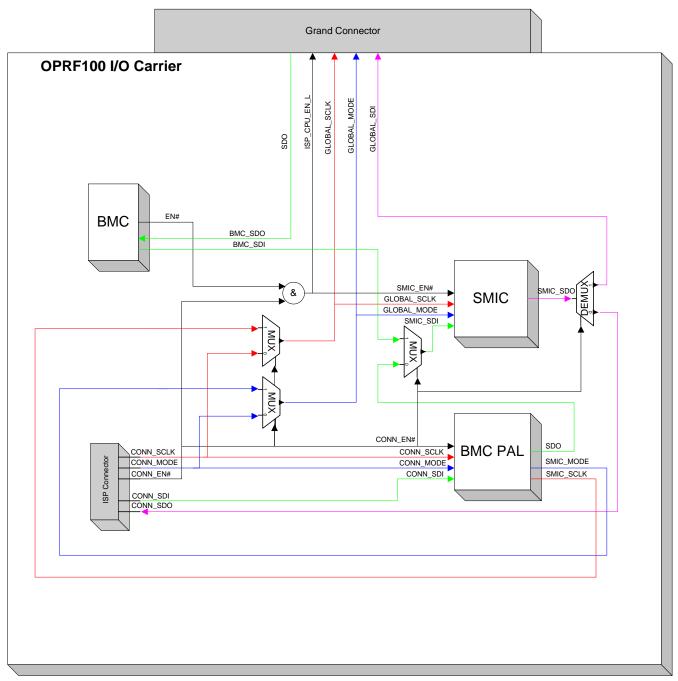

The Intel® 82371AB PCI to ISA/IDE Accelerator (PIIX4E) component provides the bridge interconnect from the primary PCI bus to an ISA bus. As implemented, the PIIX4E also provides one IDE channel as well as two USB interfaces. The ISA bus contains no slots, it is only used for communication to integrated devices such as the BIOS flash component, the SMC Super I/O component and the main OPRF100 MP board set's server management controller. The SMC Super I/O component provides all legacy connections including keyboard, mouse, floppy disk controller, one parallel port, and two serial ports. The server management interface chip (SMIC) and baseboard management controller (BMC) are the heart of the OPRF100 MP board set's server management functionality. The SMIC is implemented with a programmable logic device (PLD), while the BMC is implemented with an 80C652\* microcontroller. The SMIC actually resides on the ISA bus, while the BMC is located behind the SMIC.

### 1.2 Component Details

### 1.2.1 Microprocessor

The OPRF100 MP board set supports the Pentium III Xeon processor. It is packaged in a 330-pin SECC, and contains a processor core, L2 cache components, and miscellaneous other components mounted to a fiberglass substrate. The substrate is then mounted to a cartridge, which includes a heat plate to which a heat sink is attached for heat dissipation.

The Profusion carrier has jumpers to support the ratio of processor core frequency to system bus frequency ranging from 2 to 7 in 1/2-step increments. This allows for selection of future proces-

sors up to 750 MHz. See Chapter 3 for more details on how to select the ratio. All processors in the system must be running at the same frequency. Also, mixed processor steppings will be supported on a limited basis. Refer to the appendices in this document for information on supported mixed stepping configurations. Refer to the 100-MHz Slot 2 Processor EMTS, Version 1.5, for more information on the Pentium III Xeon processor.

### 1.2.2 Profusion\* PCIset

The OPRF100 MP board set is based on the Profusion PCIset. The Profusion PCIset is optimized for server platforms and offers the following features not found on previous Intel<sup>®</sup> chip sets.

- Support for greater than 8 GB of memory addressing.

- Support for up to eight processors.

- 64-bit 66-MHz PCI bus support.

In addition, the I/O performance of the Profusion PCIset has been increased from previous chip sets.

- Dual 100-MHz front-side processor buses with a combined peak bandwidth of 1.6 GB/s.

- Dual dedicated 100-MHz memory buses with a combined peak bandwidth of 1.6 GB/s.

- Dedicated I/O bus with a peak bandwidth of 800 MB/s.

The Profusion PCIset is comprised of six components, consisting of three unique components:

- One MAC located on the Profusion carrier.

- One DIB located on the Profusion carrier.

- Four PB64s located on the I/O carrier.

### 1.2.2.1 Memory Access Controller (MAC)

The Memory Access Controller (MAC) is packaged in a ceramic ball grid array (CBGA) package. It provides the interface between both processor buses, both memory buses, and the I/O bus. The MAC dissipates 5-6 W and will be shipped without a heat sink.

### 1.2.2.2 Data Interface Buffer (DIB)

The Data Interface Buffer (DIB) is packaged in a 655-pin ball grid array (BGA) package. It provides the interface between both processor buses, both memory buses, and the I/O bus. The DIB dissipates 5-6 W and will be shipped without a heat sink.

### 1.2.2.3 PB64 (PCI bus 64-bit expander bridge component of the Profusion chip set)

The PB64 is packaged in a 456-pin BGA package. It provides the interface between the I/O bus and the PCI buses. Four PB64s are located on the I/O carrier. Each PB64 dissipates 7-8 W and the I/O carrier is planned to be shipped with a heat sink on each PB64.

#### 1.2.3 **Programmable Interrupt Device (PID)**

The Programmable Interrupt Device (PID) is an ESG/Intel developed ASIC, which provides interrupt steering functions (including support logic for use with the 8259A interrupt controllers in the PIIX4E) and I/O APIC facilities. In addition to the standard IRQs, the PID supports a large number of PCI and onboard interrupt sources; a total of 64 interrupt routing table entries are available. A separate interrupt input will be provided for each of the four interrupts from every 64-bit PCI slot on the I/O carrier.

The PID is packaged in a 256-pin BGA package.

#### 1.3 **Performance**

The core of the OPRF100 MP board set is the Pentium III Xeon processor and the Profusion PCIset. Below are the capabilities of each of the major buses on the OPRF100 MP board set. The values shown are peak bandwidth capable on the bus. Actual sustained bandwidth will be lower and will vary with the configuration of the server (i.e., adapter cards, O/S, etc.) and the application(s) being run.

Table 1-1: Peak Bus Bandwidth

| Bus       | Frequency | Bus Width                    | Peak Band Width | Signaling<br>Technology |

|-----------|-----------|------------------------------|-----------------|-------------------------|

| Processor | 100 MHz   | 72-bits (64-data + 8 ECC)    | 800 MB/s        | GTL+                    |

| Memory    | 100 MHz   | 72-bits (64-data + 8 ECC)    | 800 MB/s        | GTL+                    |

| IO bus    | 100 MHz   | 72-bits (64-data + 8 ECC)    | 800 MB/s        | GTL+                    |

| PCI-64    | 66 MHz    | 64-bits (64-data + 2 parity) | 532 MB/s        | TTL/LV-TTL              |

This page intentionally left blank.

### **OPRF100 I/O Carrier**

This chapter describes the architecture of the OPRF100 I/O carrier. The I/O carrier mates with the Profusion\* carrier and other boards of the OPRF100 MP board set through the midplane board. The I/O carrier contains all I/O interfaces for the server board set.

### **Features**

The I/O carrier has the following features:

- Four functionally independent PCI buses.

- Integrated dual channel LVDS controller.

- Integrated Disk Electronics (IDE) controller supporting one IDE bus.

- Onboard video, serial, parallel, Universal Serial Bus (USB).

- Six hot-plug 33-MHz, 64-bit PCI slots.

- Four hot-plug 66-MHz, 64-bit PCI slots.

- Wake On LAN\* hardware interface.

- I<sup>2</sup>C\* server management interface.

### **Architectural Overview** 2.1

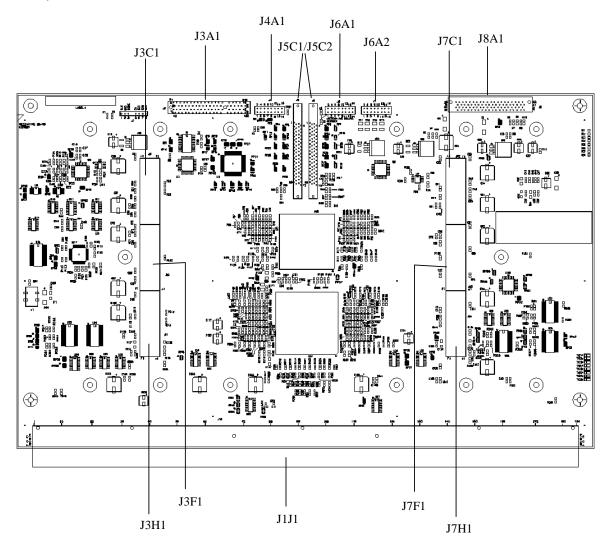

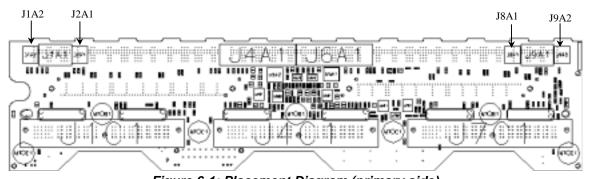

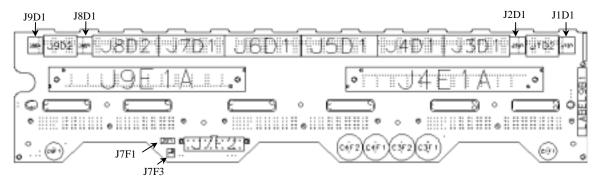

This section provides an overview of the I/O carrier, showing functional blocks and the component placement diagrams of the I/O carrier and I/O riser board.

The following figure illustrates the general architecture of the I/O carrier.

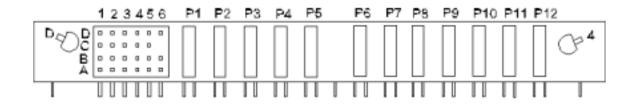

Figure 2-1: I/O Carrier Placement Plot

The I/O carrier provides the primary input/output interface of the OPRF100 MP board set. The carrier interfaces with the OPRF100 Profusion carrier through the midplane board.

### 2.1.1 I/O Bus Interface

The four PB64 components interface the MAC and DIB components through the midplane board with an I/O bus operating at 100 MHz. This I/O bus is a 64-bit wide bus and provides a peak bandwidth of 800 MB/s. For reliability, the address bus is parity protected and the data bus is ECC protected.

### 2.1.2 PCI Bus A

PCI Bus A operates at 64 bits, 33 MHz and fully adheres to the *PCI Specification, Revision 2.1*. PCI Bus A provides a peak bandwidth of 264 MB/s. This PCI bus is configured on the I/O carrier with the necessary devices to boot the operating system. The Intel<sup>®</sup> 82371AB PCI to ISA/IDE Accelerator (PIIX4E) component provides the bridge to Industry Standard Architecture (ISA) devices, IDE devices, and the USB interface. The boot flash ROM is directly connected to the ISA bus and under control of the PIIX4E. The arbiter for PCI Bus A resides in the PB64 component controlling this bus.

A Symbios\* 53C896 Ultra2 SCSI chip provides two 16-bit high speed SCSI channels. This high performance SCSI chip is capable of providing data rates up to 80 MB/s per channel in 16-bit operations to insure maximum data throughput while minimizing PCI bus overhead.

Onboard video is supplied by a Cirrus Logic\* GD5446 PCI video controller with 2 MB of onboard video EDO DRAM. The CL-GD5446 VisualMedia\* accelerator is a 64-bit DRAM-based SVGA controller with hardware-accelerated BitBLT (bit boundary block transfer), video playback, and video capture to the frame buffer. It combines the Cirrus Logic V-Port\* with a multiformat frame buffer for cost effective video playback. The onboard video also features a 64-bit GUI BitBLT engine with double-buffered, memory-mapped control registers.

Two 64-bit user accessible expansion slots are provided on this bus. Both PCI slots are hot-pluggable, adhering to the *PCI Hot Plug Specification*, *Revision 1.0*.

PCI Bus A is *PCI Specification*, *Revision 2.1* compliant and provides the user with two expansion slots for high bandwidth applications. Both PCI slots are hot-pluggable, adhering to the *PCI Hot Plug Specification*, *Revision 1.0*. PCI Bus A provides a peak bandwidth of 264 MB/s. Additional information is available in Section PCI Bus A.

Server management logic is also connected to this bus indirectly through the ISA bus. Additional information on the server management logic is available in Section Server Management Logic.

### 2.1.3 **PCI Bus B**

The 64-bit, 33-MHz PCI Bus B is also *PCI Specification, Revision 2.1* compliant. PCI Bus B provides a peak bandwidth of 264 MB/s. The Programmable Interrupt Device (PID), an Intel<sup>®</sup> designed Application Specific Integrated Circuit (ASIC), resides on the PCI bus for system interrupt steering. The PID contains the logic required to provide 8259A mode, APIC mode and Advanced Configuration and Power Interface (ACPI) functionality. The PID includes PCI, APIC, and PIIX4E interfaces. Refer to Section Programmable Interrupt Device for more information on the PID. The arbiter for PCI Bus B resides in the PB64 component controlling this bus.

Four 64-bit PCI expansion slots are provided on this bus. All four PCI slots are hot-pluggable, adhering to the *PCI Hot Plug Specification, Revision 1.0*. Additional information is available in Section PCI Bus B.

### 2.1.4 **PCI Bus C**

The 64-bit, 66-MHz PCI Bus C is *PCI Specification, Revision 2.1* compliant and provides the user with two expansion slots for high bandwidth adapters. Both PCI slots are hot-pluggable, adhering to the *PCI Hot Plug Specification, Revision 1.0*. PCI Bus C provides a peak bandwidth of 528 MB/s. Additional information is available in Section PCI Bus C.

### 2.1.5 PCI Bus D

The 64-bit, 66-MHz PCI Bus D is *PCI Specification, Revision 2.1* compliant and provides the user with two expansion slots for high bandwidth applications. Both PCI slots are hot-pluggable, adhering to the *PCI Hot Plug Specification, Revision 1.0*. PCI Bus D provides a peak bandwidth of 528 MB/s. Additional information is available in Section PCI Bus D.

### 2.1.6 Server Management Logic

The heart of server management is the Baseboard Management Controller (BMC). External communication can be established with the BMC through the Server Management Interface Controller (SMIC). For detailed information on the SMIC, see the Server Management Interface Controller (SMIC) section. The server management logic maintains a system event log (SEL) to store important system information. System voltage levels are monitored by the server management logic.

OPRF100 server management includes hardware to perform in-system programming (ISP) of the system programmable logic.

The server management logic also provides monitoring and control of other system devices including: video, floppy disk, chassis fans, and BIOS flash. See the Server Management section for details on server management logic.

### 2.1.7 A450NX I/O Riser Board

To conserve space on the I/O carrier, many legacy connections have been placed on a riser board attached to the I/O carrier. Connections to video, keyboard, mouse, two COM ports, one parallel port, and the Intelligent Chassis Management Bus (ICMB) interface are all provided through the A450NX I/O riser board.

### 2.1.8 Major Component Reference Tables

The following tables identify the major components and their reference designators.

Table 2-1: I/O Carrier Component Reference

| Reference<br>Designator                  | Name and Description                                          | Reference<br>Designator | Name and Description                           |

|------------------------------------------|---------------------------------------------------------------|-------------------------|------------------------------------------------|

| J1A1                                     | USB Connector.                                                | U1C1                    | Cirrus Logic* GD5446 VGA Controller.           |

| J1B1                                     | A450NX I/O Riser Board Connector.                             | U2G1                    | Symbios* 53C896 LVDS.                          |

| J3B1, J3B2,<br>J4B1, J5B1,<br>J5B2, J6B1 | 33 MHz PCI Slots.                                             | U1D1                    | SMC* Ultra I/O Component.                      |

| J7B1, J8B1,<br>J8B2, J9B1                | 66 MHz PCI Slots.                                             | U2D3                    | PIIX4E, PCI to ISA Bridge Device.              |

| J2F1                                     | In System Programming. (Used to program the SIMC and BMC PAL) | U2F2                    | SMIC (Server Management Interface Controller). |

| J1G1                                     | IDE Connector: Primary Channel.                               | U4F2                    | BMC PAL                                        |

Table 2-1: I/O Carrier Component Reference (Continued)

| J1E3                      | Floppy Disk Drive Connector.                      | U3H1 | BMC (Baseboard Management Controller).                         |

|---------------------------|---------------------------------------------------|------|----------------------------------------------------------------|

| J3H1                      | Server Management Feature<br>Connector.           | U4H1 | Flash to hold the BMC code. 32Kx8 (or 64Kx8), socketed device. |

| J1G2, J1E4                | SCSI Connector (for peripheral devices).          | U3G3 | 32Kx8 RAM for BMC.                                             |

| J1F1, J1E2                | Auxiliary I <sup>2</sup> C* Connectors.           | U5F2 | PID.                                                           |

| J1E1                      | Wake On Lan*                                      | U5H1 | PB64-0 (PCI Bus Expander 0).                                   |

| J2D1                      | Manufacturing Mode                                | U6H1 | PB64-1 (PCI Bus Expander 1).                                   |

| J2C1                      | PHP Header( Interface to Slot LED's and Switches) | U7H1 | PB64-2 (PCI Bus Expander 2).                                   |

| SW4G1                     | Configuration Switches.                           | U9H1 | PB64-3 (PCI Bus Expander 3).                                   |

| U2C3                      | 2 MB BIOS Flash Device.                           | B6G1 | Battery.                                                       |

| U2A2, U2A3,<br>U2B1, U2B2 | 2 MB Video DRAM.                                  |      |                                                                |

Table 2-2: A450NX I/O Riser Board Component References

| Reference<br>Designator | Name and Description                                        |

|-------------------------|-------------------------------------------------------------|

| J1                      | ICMB Connector.                                             |

| J4                      | Combined Mouse and Serial Connector.                        |

| J5                      | COM 1 and COM 2 Serial Port Connectors.                     |

| J6                      | Combined Parallel and Video Connector.                      |

| J7                      | Edge Connector. Plugs into connector J3 on the I/O carrier. |

### 2.2 **Connector Signal Descriptions**

This section defines the function of signal pins on all user accessible I/O carrier connector interfaces. The signal mnemonics defined here may appear in descriptive text throughout this document. An "\_L" following a signal name indicates that the signal is active-low. (Note: this is the same convention used on schematics for active-low signals). One colon between numbers in square brackets indicates a range of signals (e.g., the notation [13:0] is a range of 14 unique signals). Refer to the Mechanical Specifications section for the connector pinout and mechanical information.

### 2.2.1 I/O Connector Signals

Most signals appearing on the I/O connector interfacing with the Profusion carrier are driven by the Profusion MAC and DIB components. These signals follow the GTL+ specification and use a Pentium<sup>®</sup> Pro bus protocol.

The following tables define the signals according to functional groups: I/O, Clock and Reset, Server Management, Legacy, JTAG, ISP, Front Panel, and Power Signals. Each PB64 on the I/O carrier is connected to the I/O bus on the Profusion carrier.

Table 2-3: I/O Bus Interface Signals

| Signal(s)     | Name and Description                                                                                                                                                                                                            |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IO_A[35:3]    | I/O Bus Address. Address signals are the upper address bits issued with the current request.                                                                                                                                    |

| IO_ADS_L      | I/O Bus Address Strobe. Address Strobe indicates that the current cycle is the first of two cycles of a request.                                                                                                                |

| IO_AERR_L     | I/O Bus Address Parity Error. Address Parity Check is asserted when either an address or request parity error occurs.                                                                                                           |

| IO_AP[1:0]_L  | I/O Bus Address Parity. Address Parity is the parity computed over the address; IO_AP[1] covers IO_A[35:24], and IO_AP[0] covers IO_A[23:3].                                                                                    |

| IO_BERR_L     | I/O Bus Data Error. Bus Error indicates an unrecoverable data error.                                                                                                                                                            |

| IO_BINIT_L    | I/O Bus Initialization.                                                                                                                                                                                                         |

| IO_BNR_L      | I/O Bus Block Next Request. Block Next Request blocks the current request bus owner from issuing new requests.                                                                                                                  |

| IO_BPRI_L     | I/O Bus Priority Request. Priority Agent Bus Request is issued by the high-priority bus agent to acquire the request bus. The high-priority agent is always the next bus owner. (This is an input on the Pentium® Pro I/O bus.) |

| IO_D[63:0]    | I/O Bus Data. Each set of 72 data signals moves data to/from an SDRAM array. Sixty-four signals are used for the actual data and the other eight signals carry ECC information.                                                 |

| IO_DBSY_L     | I/O Bus Data Busy. Data Bus Busy is used by the data bus owner to hold the data bus for transfers requiring more than one cycle.                                                                                                |

| IO_DEFER_L    | I/O Bus Defer. IO_DEFER is driven by the addressed agent to indicate that bus completion cannot be guaranteed for the transaction.                                                                                              |

| IO_DEP_L[7:0] | I/O Bus ECC. Each set of 72 data signals moves data to/from an SDRAM array. Sixty-four signals are used for the actual data and the other eight signals carry ECC information.                                                  |

### Table 2-3: I/O Bus Interface Signals

| IO_DRDY_L     | I/O Bus Data Ready. Data Ready is asserted for each cycle in which data is transferred.                                                                                                                                                                                |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IO_HIT_L      | <b>I/O Bus Hit</b> . Hit indicates that a caching agent holds an unmodified version of the requested line. Hit is also driven in conjunction with IO_HITM to extend the snoop window.                                                                                  |

| IO_HITM_L     | I/O Bus Hit Modified. Hit Modified indicates that a caching agent holds a modified version of the requested line and that this agent assumes responsibility for providing the line. Hit Modified is also driven in conjunction with IO_HIT to extend the snoop window. |

| IO_LOCK_L     | I/O Bus Lock. Lock is asserted for an indivisible sequence of transactions.                                                                                                                                                                                            |

| IO_REQ[4:0]_L | I/O Bus Request. In the first cycle of a request, these signals carry the request type. In the second cycle, they carry the data size and transfer length.                                                                                                             |

| IO_RESET_L    | I/O Bus Reset. (This signal is an input on the Pentium Pro I/O bus.)                                                                                                                                                                                                   |

| IO_RP_L       | I/O Bus Request Parity. Request Parity is the parity computed over IO_ADS and IO_REQ[3:0].                                                                                                                                                                             |

| IO_RS[2:0]_L  | I/O Bus Response. Response indicates the type of response.                                                                                                                                                                                                             |

| IO_RSP_L      | I/O Bus Response Parity. Response Parity is parity computed over IO_RS[2:0].                                                                                                                                                                                           |

| IO_TRDY_L     | I/O Bus Target Ready. Target Ready indicates a valid response cycle.                                                                                                                                                                                                   |

The I/O Connector Clock and Reset Signals table is a summary of I/O connector clock and reset signal pins, including the signal mnemonic, name, and brief description.

Table 2-4: I/O Connector Clock and Reset Signals

| Signal(s)       | Name and Description                                                                                                                                       |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IO_PWRGD        | I/O Power Good. Inactive state resets the Profusion* carrier. Note that this power good signal transitions when the front panel resets the system.         |

| IO_RESET_L      | <b>I/O Bus Reset</b> . This signal is driven from the primary PB64 and is an input on the Pentium <sup>®</sup> Pro I/O bus.                                |

| PB64_A_CRESET_L | <b>Delayed CPU Reset</b> . This reset is asserted eight clocks after IO_RESET_L for devices that use IO_RESET_L for logic.                                 |

| PB64_A_CLK      | <b>Pentium Pro Bus Clock</b> . All Pentium Pro bus timings are referenced to the rising edge of this clock. This clock is driven to the PB64 on PCI Bus A. |

| PB64_B_CLK      | <b>Pentium Pro Bus Clock</b> . All Pentium Pro bus timings are referenced to the rising edge of this clock. This clock is driven to the PB64 on PCI Bus B. |

Table 2-4: I/O Connector Clock and Reset Signals (Continued)

| PB64_C_CLK | <b>Pentium Pro Bus Clock</b> . All Pentium Pro bus timings are referenced to the rising edge of this clock. This clock is driven to the PB64 on PCI Bus C.                                                                                                                                                                                                                                                                                       |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PB64_D_CLK | <b>Pentium Pro Bus Clock</b> . All Pentium Pro bus timings are referenced to the rising edge of this clock. This clock is driven to the PB64 on PCI Bus D.                                                                                                                                                                                                                                                                                       |

| PWR_GOOD   | <b>Power Good</b> . This signal provides a power-on reset to the MAC and DIB. The signal is a 3.3 V tolerant signal and indicates that the clocks and power supplies are within their specifications. The signal remains low (capable of sinking leakage current) without glitches from the time that the power supplies are turned on until they become valid. The signal then transitions monotonically to a high (3.3 V) state within 100 ns. |

| PWRGDB     | <b>Buffered Power Good</b> . Buffered version of Profusion carrier power good input to PB64. This signal indicates when power is good throughout the entire system.                                                                                                                                                                                                                                                                              |

The I/O Connector Server Management Signals table is a summary of server management signal pins, including the signal mnemonic, name, and brief description.

Table 2-5: I/O Connector Server Management Signals

| Signal(s)       | Name and Description                                                                                                                                                     |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU_SPI_RESET_L | CPU SPI Reset. Driven by SMIC to reset CPU SPI chain.                                                                                                                    |

| I2C_BMC_SCL     | <b>BMC I<sup>2</sup>C Clock</b> . Clock reference for the local BMC I <sup>2</sup> C* bus. This bus is controlled by the BMC.                                            |

| I2C_BMC_SDA     | <b>BMC I<sup>2</sup>C Data</b> . Serial data transfer for the local BMC I <sup>2</sup> C bus. This bus is controlled by the BMC.                                         |

| I2C_DS2P0_SCL   | <b>CPU0 I<sup>2</sup>C Clock</b> . Clock reference for the I <sup>2</sup> C bus to the first processor mezzanine board. This bus is controlled by the BMC.               |

| I2C_DS2P0_SDA   | <b>CPU0 I<sup>2</sup>C Data</b> . Serial data transfer for the I <sup>2</sup> C bus to the first processor mezzanine board. This bus is controlled by the BMC.           |

| I2C_DS2P1_SCL   | <b>CPU1 I<sup>2</sup>C Clock</b> . Clock reference for the I <sup>2</sup> C bus to the second processor mezzanine board. This bus is controlled by the BMC.              |

| I2C_DS2P1_SDA   | <b>CPU1</b> I <sup>2</sup> C <b>Data</b> . Serial data transfer for the I <sup>2</sup> C bus to the second processor mezzanine board. This bus is controlled by the BMC. |

| I2C_GLOBAL_SCL  | <b>Global I<sup>2</sup>C Clock.</b> Main I <sup>2</sup> C clock connecting all microcontrollers on all system boards.                                                    |

| I2C_GLOBAL_SDA  | <b>Global I<sup>2</sup>C Data</b> . Main I <sup>2</sup> C data connecting all microcontrollers on all system boards.                                                     |

Table 2-5: I/O Connector Server Management Signals (Continued)

| SPI_CLK       | SPI Clock. Clock used for the Serial-Parallel Interface chains.                                                                                |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| SPI_CPU_SEL_L | <b>SPI CPU Chain Select</b> . Selects one of the CPU SPI chains for reading or writing. The subselects are used to select exactly which chain. |

| SPI_MISO      | SPI Chain Serial Input. This is the data input for the serial SPI chain.                                                                       |

| SPI_MOSI      | SPI Chain Serial Output. This is the data output for the serial SPI chain.                                                                     |

| SPI_SEL0_L    | <b>SPI Chain Subselect 0</b> . Selects the appropriate CPU SPI chain for reading or writing.                                                   |

| SPI_SEL1_L    | SPI Chain Subselect 1. Selects the appropriate CPU SPI chain for reading or writing.                                                           |

| SPI_SEL2_L    | SPI Chain Subselect 2. Selects the appropriate CPU SPI chain for reading or writing.                                                           |

The I/O Connector Legacy Signals table is a summary of legacy signal pins, including the signal mnemonic, name, and brief description.

Table 2-6: I/O Connector Legacy Signals

| Signal(s)     | Name and Description                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A20M_L        | Address 20 Mask. PIIX4E asserts A20M# to the CPU based on combination of port 92 register, bit 1 (FAST_A20), and A20GATE input signal.                                                                                                                                                                                                                                                                                                                                        |

| ADC_OSC_RESET | Initialize A/D clock. This signal initializes the A/D oscillator to a reliable value.                                                                                                                                                                                                                                                                                                                                                                                         |

| CPU_SLP_L     | <b>CPU Sleep</b> . This pin is driven by the PIIX4E to the processor and puts it into the sleep state.                                                                                                                                                                                                                                                                                                                                                                        |

| FERR_L        | <b>Numeric Coprocessor Error</b> . This pin functions as a FERR# signal supporting coprocessor errors. This signal is tied to the coprocessor error signal on the CPU. If FERR# is asserted, PIIX4E generates an internal IRQ13 to its interrupt controller unit. PIIX4E then asserts the INT output to the CPU. FERR# is also used to gate the IGNNE# signal to ensure that IGNNE# is not asserted to the CPU unless FERR# is active.                                        |

| IGNNE_L       | Ignore Numeric Exception. This signal is connected to the ignore numeric exception pin on the CPU. Used only if the PIIX4E coprocessor error reporting function is enabled. If FERR# is active, indicating a coprocessor error, a write to the coprocessor error register (F0h) causes the IGNNE# to be asserted. IGNNE# remains asserted until FERR# is negated. If FERR# is not asserted when the coprocessor error register is written, the IGNNE# signal is not asserted. |

Table 2-6: I/O Connector Legacy Signals (Continued)

| INIT_L        | Initialization. Asserted in response to any one of the following conditions. When the system reset bit in the reset control register is reset to 0 and the reset CPU bit toggles from 0 to 1, PIIX4E initiates a soft reset by asserting INIT. PIIX4E also asserts INIT if a shut down special cycle is decoded on the PCI bus, if the RCIN# signal is asserted, or if a write occurs to port 92h, bit 0. When asserted, INIT remains asserted for approximately 64 PCI clocks before being negated. |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INTR          | <b>CPU Interrupt</b> . INTR is driven by PIIX4E to signal the CPU that an interrupt request is pending and needs to be serviced. It is asynchronous with respect to SYSCLK or PCICLK and is always an output. The interrupt controller must be programmed following PCIRST# to ensure that INTR is at a known state.                                                                                                                                                                                 |

| MEM_SBCERR_L  | Single-Bit Corrected Memory Error and Performance Counter overflow. This is an input to the PID.                                                                                                                                                                                                                                                                                                                                                                                                     |

| PIC_CLK       | APIC Clock. PIC_CLK is used to determine when valid data is being sent over the APIC bus (PICD[1:0]).                                                                                                                                                                                                                                                                                                                                                                                                |

| PICD[1:0]     | APIC data. PICD[1:0] are bidirectional signals used to send and receive data over the APIC bus.                                                                                                                                                                                                                                                                                                                                                                                                      |

| PIIX_SMB_SCL  | SM Bus Clock. System management bus clock used to synchronize transfer of data on SMBus.                                                                                                                                                                                                                                                                                                                                                                                                             |

| PIIX_SMB_SDA  | SM Bus Data. Serial data line used to transfer data on SMBus.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PIIX_SMB_SEL0 | <b>SM Bus Select 0</b> . The SM Bus was split into four separate SM buses in order the support the large number of DIMMs in main memory. This pin is select 0 for the multiplexer on the Profusion* carrier.                                                                                                                                                                                                                                                                                         |

| PIIX_SMB_SEL1 | <b>SM Bus Select 1</b> . The SM Bus was split into four separate SM buses in order the support the large number of DIMMs in main memory. This pin is select 1 for the multiplexer on the Profusion carrier.                                                                                                                                                                                                                                                                                          |

| STOP_CLK_L    | Stop Clock. This signal is output from the PIIX4E and connects directly to the CPU. STOP_CLK_L is synchronous to the PCI clock on PCI Bus A.                                                                                                                                                                                                                                                                                                                                                         |

The I/O connector JTAG Signals table is a summary of JTAG signal pins, including the signal mnemonic, name, and brief description. The I/O carrier boundary scan chain is connected to the chain on the Profusion carrier. The chain is accessible via the ITP connector on the Profusion carrier. See Section Boundary Scan for additional information.

Table 2-7: I/O Connector JTAG Signals

| Signal(s) | Name and Description                                                                                                        |

|-----------|-----------------------------------------------------------------------------------------------------------------------------|

| IO_TCK    | <b>Test Clock</b> . Test clock is used to clock state information and data into and out of the device during boundary scan. |

| IO_TDI    | <b>Test Data Input</b> . Test input is used to serially shift data and instructions into the TAP.                                                    |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| IO_TDO    | Test Data Output. Test output is used to shift data out of the device.                                                                               |

| IO_TMS    | <b>Test Mode Select</b> . Test mode select is used to control the state of the TAP controller.                                                       |

| IO_TRST_L | <b>Test Reset</b> . Test Reset is used to reset the TAP controller logic. For normal operation, TRST_L must be asserted low after PWRGD is asserted. |

The following tables describe the signals used to program various devices inside the chassis.

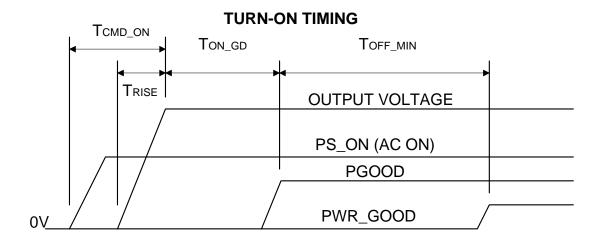

Table 2-8: I/O Connector In-system Programming Signals