# Intel AP450GX MP Server Board Set Technical Product Specification

Order Number 282964-003

September 1997

The AP450GX MP Server Board Set may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Characterized errata that may cause the AP450GX MP Server Board Set's behavior to deviate from published specifications are documented in the AP450GX MP Server Board Set Specification Update.

#### **Revision History**

| Revision | Revision History                                                                                                                | Date |

|----------|---------------------------------------------------------------------------------------------------------------------------------|------|

| -001     | Preliminary release of the AP450GX MP Server Board Set Technical Product Specification                                          | 7/96 |

| -002     | Second release of the AP450GX MP Server Board Set Technical Product Specification with additions and corrections.               | 3/97 |

| -003     | Third release, including an update on errata in Appendix E, and a new section on the 200MHz/1MB processor module in Appendix F. | 9/97 |

This product specification applies only to the standard AP450GX MP Server Board Set with BIOS identifier CD0.

Changes to this specification will be published in the AP450GX MP Server Board Set Specification Update before being incorporated as a revision to this document.

The AP450GX MP Server Board Set may contain design defects or errors known as errata which may cause the product to deviate from published specifications

**NOTE**: If printing this document from an electronic file, use a PostScript printer with the appropriate PostScript print driver to insure the drawings print clearly.

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications. Intel may make changes to specifications and product descriptions at any time, without notice.

Technical updates should be obtained by calling Intel Literature or writing:

Intel Corporation P.O. Box 7641 Mt. Prospect, IL 60056-7641

or call in North America 1-800-879-4683, Europe 44-0-1793-431-155, France 44-0-1793-421-777, Germany 44-0-1793-421-333, Japan (fax only) 81-0-120-478-832, other Countries 708-296-9333

\* Third-party brands and trademarks are the property of their respective owners.

Copyright © 1997, Intel Corporation. All rights reserved

# **Table of Contents**

| 1 | Board Set Description                                 | 7  |

|---|-------------------------------------------------------|----|

|   | 1.1 Overview                                          | 7  |

|   | 1.2 Board Set Options                                 | 9  |

|   | 1.3 Form Factor                                       | 9  |

|   | 1.4 Placement Diagrams                                | 10 |

|   | 1.5 Connector Locations                               | 14 |

|   | 1.6 Microprocessor                                    | 15 |

|   | 1.6.1 Processors and Processor Modules                | 17 |

|   | 1.7 Bus Termination Module                            | 17 |

|   | 1.8 Processor Population Order                        | 18 |

|   | 1.9 Memory                                            | 20 |

|   | 1.9.1 System Memory                                   | 20 |

|   | 1.9.2 Memory Installation Options (1GB Memory Module) | 21 |

|   | 1.9.3 Memory Performance Hints                        | 22 |

|   | 1.9.4 4GB Memory Module                               |    |

|   | 1.9.5 Memory Configuration Options                    |    |

|   | 1.10 Intel 450GX PCIset                               |    |

|   | 1.11 Onboard SCSI Controllers                         |    |

|   | 1.12 EISA Expansion Slots                             |    |

|   | 1.13 PCI Expansion Slots                              |    |

|   | 1.14 Boot Order                                       |    |

|   | 1.15 Super VGA Controller                             |    |

|   | 1.16 Keyboard and Mouse                               |    |

|   | 1.17 Advanced Integrated Peripheral (AIP)             |    |

|   | 1.17.1 Floppy Drive Support                           |    |

|   | 1.17.2 Serial Ports                                   |    |

|   | 1.17.3 Parallel Port                                  |    |

|   | 1.17.4 IDE Support                                    |    |

|   | 1.18 Miscellaneous Functions                          |    |

|   | 1.18.1 I <sup>2</sup> C Diagnostic Bus                |    |

|   | 1.18.2 Server Management Connector                    | 36 |

|     | 1.18.3 System Fan Interface                               | 36 |

|-----|-----------------------------------------------------------|----|

|     | 1.18.4 Hard Drive LED Interface                           | 36 |

|     | 1.19 Control Signals                                      | 37 |

|     | 1.19.1 Remote Sensing                                     | 37 |

|     | 1.19.2 Power Good (PGOOD & PWRGOOD) signals               | 37 |

|     | 1.20 Baseboard Jumper Settings                            | 38 |

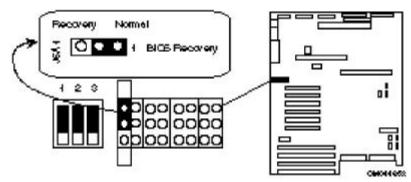

|     | 1.20.1 BIOS Recovery Jumper, J6A1                         | 39 |

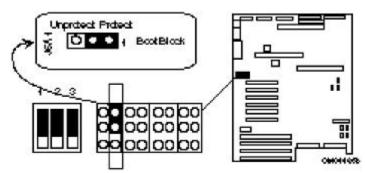

|     | 1.20.2 Boot Block Jumper, J6A1                            | 41 |

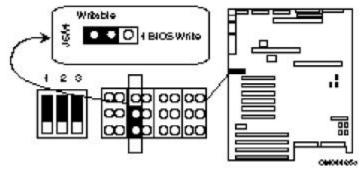

|     | 1.20.3 BIOS Write Jumper, J6A4                            | 41 |

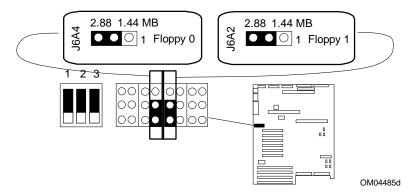

|     | 1.20.4 Floppy 0 Jumper at J6A4; Floppy 1 Jumper at J6A2   | 42 |

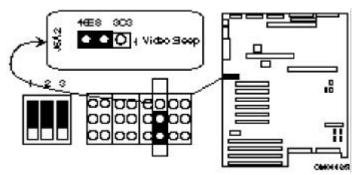

|     | 1.20.5 Video Sleep Jumper, J6A2                           | 43 |

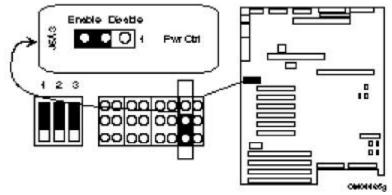

|     | 1.20.6 Power Control Jumper, J6A3                         | 43 |

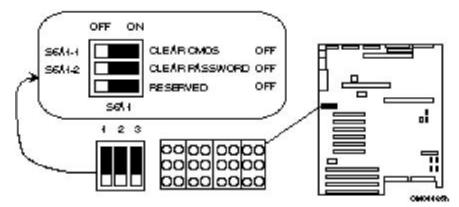

|     | 1.20.7 Configuration Switches                             | 44 |

|     | 1.21 Processor Module Jumper Settings                     | 46 |

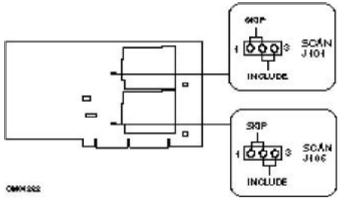

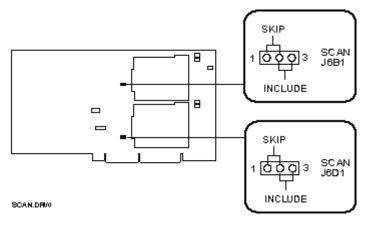

|     | 1.21.1 SCAN Jumpers, J101 and J106                        | 47 |

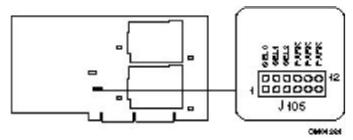

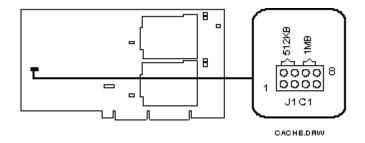

|     | 1.21.2 VID Jumpers, J103                                  | 47 |

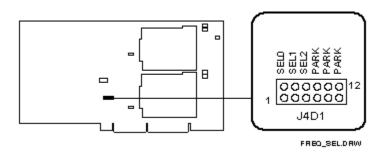

|     | 1.21.3 Processor Frequency Select Jumpers, J105           | 48 |

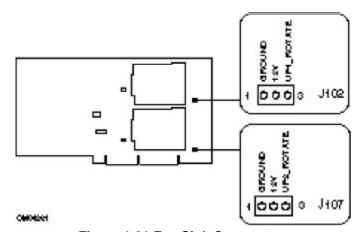

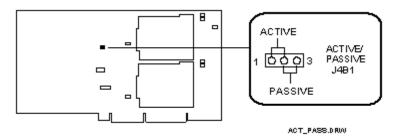

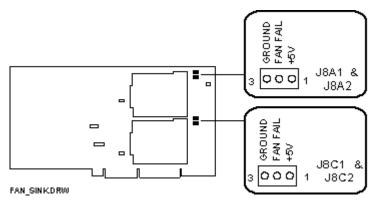

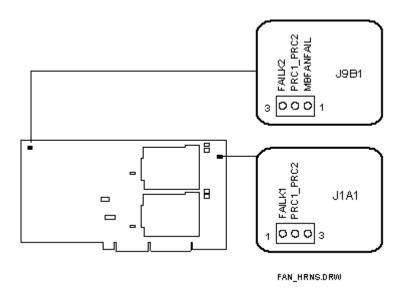

|     | 1.21.4 Processor Board Fan Sink Connectors, J102 and J107 | 49 |

|     | 1.21.5 Power Supply Considerations                        | 50 |

|     | 1.22 Regulatory Compliance                                | 50 |

|     | 1.23 Product Certification Markings                       | 50 |

|     | 1.23.1 European CE Marking                                | 50 |

|     | 1.23.2 UL Recognition                                     | 50 |

|     | 1.23.3 Canadian Compliance                                | 50 |

|     | 1.23.4 Installation Requirements                          | 51 |

|     | 1.23.5 Installation Precautions                           | 52 |

|     | 1.23.6 Battery Marking                                    | 52 |

|     | 1.23.7 Overload Protection                                | 52 |

| 2 : | System Resources                                          | 54 |

|     | 2.1 Memory Map                                            | 54 |

|     | 2.2 I/O Map                                               | 55 |

|     | 2.3 PCI Configuration Space Map                           | 57 |

|     | 2.4 DMA Channels                                          | 57 |

|     | 2.5 Interrupts                                            | 58 |

|     |                                                           |    |

| 3 BIOS, Setup, SCU and SCSISelect Utilities                | 59 |

|------------------------------------------------------------|----|

| 3.1 Introduction                                           | 59 |

| 3.2 BIOS                                                   |    |

| 3.2.1 BIOS Flash Memory Organization                       | 59 |

| 3.2.2 BIOS Upgrades                                        | 59 |

| 3.2.3 ISA IDE Support                                      |    |

| 3.2.4 PCI Auto-Configuration                               | 60 |

| 3.2.5 ISA Plug-N-Play                                      | 60 |

| 3.2.6 Language Support                                     | 61 |

| 3.2.7 Boot Options                                         | 61 |

| 3.2.8 Console Redirection                                  | 61 |

| 3.3 BIOS Setup                                             | 64 |

| 3.3.1 When to Run Setup                                    | 64 |

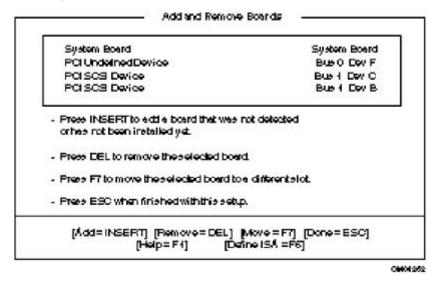

| 3.4 System Configuration Utility (SCU)                     | 66 |

| 3.4.1 When to Run the SCU                                  | 66 |

| 3.4.2 Where the SCU Gets Information                       | 66 |

| 3.4.3 Checking the Configuration at Power-on               | 66 |

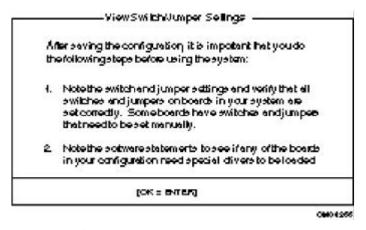

| 3.4.4 How to Use the SCU                                   | 67 |

| 3.4.5 Configuring the System                               | 68 |

| 3.4.6 About the Options                                    |    |

| 3.5 SCSISelect Utility                                     | 72 |

| 4 Error Messages and Beep Codes                            | 74 |

| 4.1 BIOS Beep Codes                                        | 74 |

| 4.2 POST Codes and Countdown Codes                         | 74 |

| 4.2.1 Recovery Port-80 Codes and Countdown Codes Displayed | 75 |

| 4.2.2 Standard Port-80 Codes and Countdown Codes Displayed | 76 |

| 4.3 POST Error Codes and Messages                          | 80 |

| 5 Electrical, Environmental and Mechanical Specifications  | 84 |

| 5.1 Absolute Maximum Ratings                               |    |

| 5.2 Electrical Specifications                              |    |

| 5.3 Environmental                                          | 86 |

| 5.4 Cooling Requirements                                   | 86 |

| 5.5 Power Budget                                           | 87 |

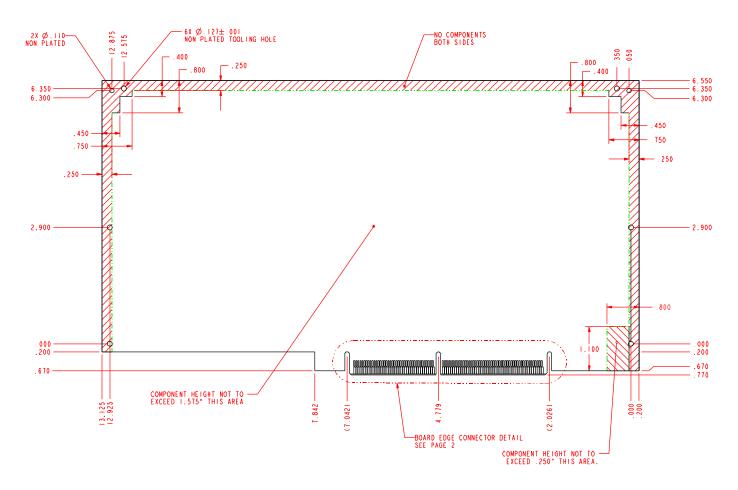

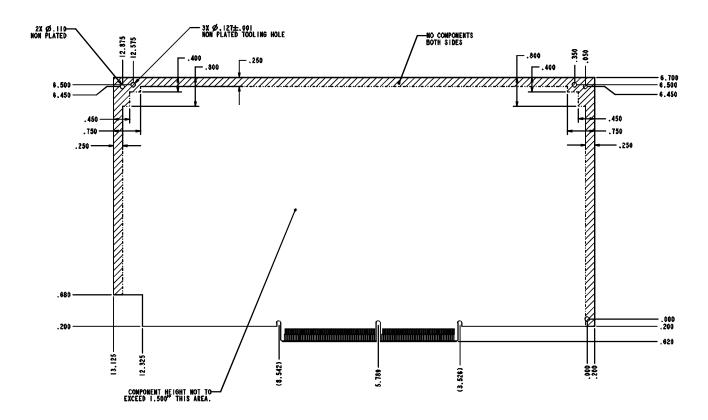

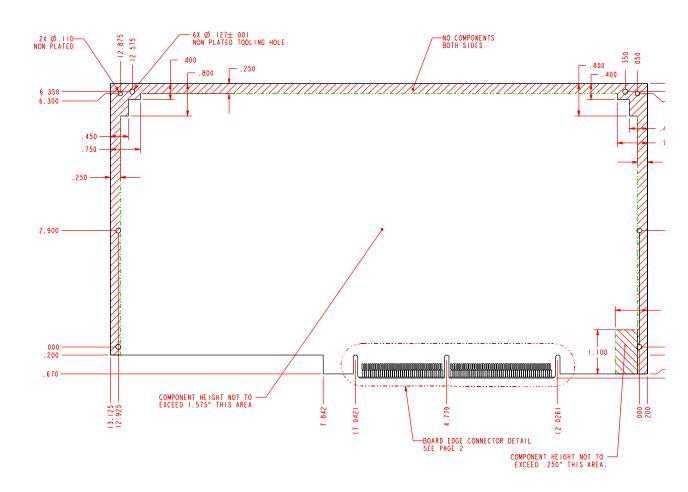

| 5.6 Mechanical Drawings                                    | 89 |

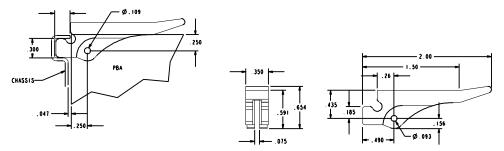

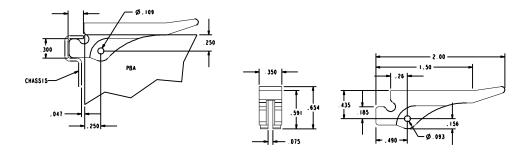

| 5.6.1 Processor and Terminator Module Mechanical Specifications               | 89  |

|-------------------------------------------------------------------------------|-----|

| 5.6.2 Memory Module Mechanical Specifications                                 | 90  |

| 5.6.3 Baseboard Mechanical Specifications                                     | 91  |

| 5.6.4 Module Insertion/Extractor Handle Specifications                        | 92  |

| 5.7 Connector Specifications                                                  | 93  |

| Appendix A Supported Environments                                             | 94  |

| Appendix B Product Codes                                                      | 95  |

| Appendix C Connector Pinouts                                                  | 96  |

| Appendix D - 450GX PCIset Register Changes                                    | 106 |

| Appendix E Errata                                                             | 107 |

| Appendix F – Pentium <sup>®</sup> Pro 1MB Processor Module for the AP450GX MP | ı   |

| Server Board Set                                                              | 128 |

# 1 Board Set Description

# 1.1 Overview

The AP450GX MP Server Board Set is a modular, high performance server system capable of supporting up to four Pentium<sup>®</sup> Pro processors. The board set includes the system baseboard, one or two processor modules, a memory module, and an optional bus terminator module.

| Board Set Feature                               | Description                                                                                                                                                                                                                                        |

|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Multi-processing support                        | Two expansion slots for processor modules; up to four Pentium® Pro microprocessors (two on each module). The system may include one processor module and one terminator module, or two processor modules.                                          |

| Upgradable memory                               | One expansion slot for a memory module, supporting up to 1GB of memory using 64 MB SIMMs. The module will support up to 2GB of memory using 128MB SIMMs. An alternate memory module is available to support up to 4GB of memory using 128MB DIMMs. |

| Bus Termination Module                          | Required per the GTL+ processor bus specification if only one processor module is installed in the system.                                                                                                                                         |

| PCI bus support                                 | Two PCI "peer" buses, each with three 32-bit PCI slots on the system base baseboard.                                                                                                                                                               |

| EISA bus support                                | Four dedicated EISA bus master slots on the system baseboard.                                                                                                                                                                                      |

| SCSI controller                                 | Two PCI based, integrated AIC-7880 controllers; fast and wide, Fast 20/Ultra SCSI-2 support.                                                                                                                                                       |

| Integrated Drive<br>Electronics (IDE) interface | Provides access to two IDE hard drives; ISA-based controller.                                                                                                                                                                                      |

| BIOS                                            | Basic Input/Output System (BIOS) stored in enhanced 512 KB (4Mbit) Paged flash memory device.                                                                                                                                                      |

| Video controller                                | Integrated ISA based CL-GD5424 super VGA controller shipped with 512 KB of video memory (expandable to 1 MB).                                                                                                                                      |

| External device connectors                      | Onboard connectors for 2 serial ports, parallel port, PS/2-compatible keyboard and mouse, and VGA monitor.                                                                                                                                         |

| Clock                                           | Real-time clock/calendar (RTC) chip with 8 KB of NVRAM.                                                                                                                                                                                            |

| Flash memory                                    | Contains Power-on Self Test (POST), BIOS core and Setup utilities.                                                                                                                                                                                 |

| System hardware monitoring                      | Detects chassis intrusion and contains sensors for temperature, voltage, power supply and fan failure.                                                                                                                                             |

| I <sup>2</sup> C Bus Support                    | I <sup>2</sup> C bus connects all major system components together for diagnostic information                                                                                                                                                      |

| Configuration utilities                         | System Configuration Utility (SCU) and SCSISelect Utility                                                                                                                                                                                          |

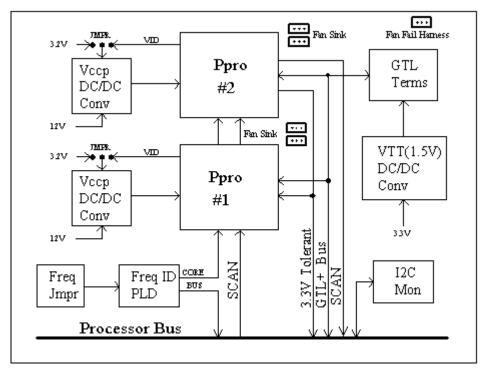

Pentium â Pro Pentium<sup>â</sup> Pro local power local power Bus Bus regulation regulation Termination Termination local power regulation local power regulation Pentiumâ Pentiumâ Pro Pro local power local power regulation regulation Processor Module **Processor** Module Processor Bus MC (MC-DP & MC-DC) PB PB SCSI B SCSI **INCA** #1 #0 Memory Bus PCI#0 **DRAM Buffers** & SIMM Sites **Memory Module** AIP, PCEB ESC Video Xbus Buffers Flash, NVRAM, RTC, Keyboard, Mouse XBus

The following diagram shows the functional blocks and system architecture.

Figure 1.1 System Block Diagram

# 1.2 Board Set Options

The server design allows expanded processor and memory capacity.

- Baseboard has two slots for processor modules and one slot for the memory module.

- Each processor module may contain one or two processors, for a configurable range from one to a maximum of four processors.

- A bus termination module is available to terminate the processor bus if only one processor

module is installed in the system. Both processor slots must be filled to correctly terminate the

processor bus.

- The standard memory module will support up to 2GB of memory using 128MB SIMMs.

- An optional memory module with 32 DIMM connectors is available which will support up to 4GB of memory using 128MB DIMMs.

- The video memory is expandable up to 1MB with a 512KB memory component.

#### 1.3 Form Factor

The board set is designed to fit into a custom form factor chassis. Currently Intel's chassis, identified as the AP450GX Chassis, is the only Intel designed chassis qualified for the AP450GX Board Set.

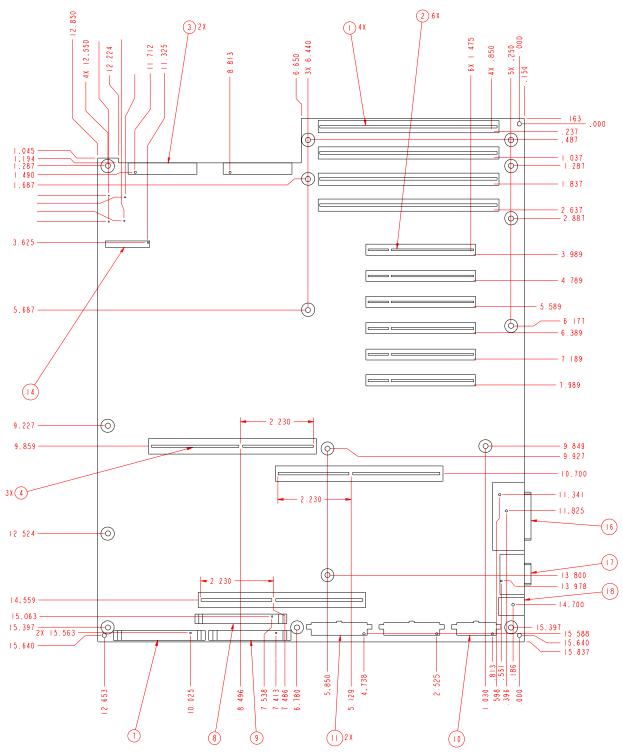

# 1.4 Placement Diagrams

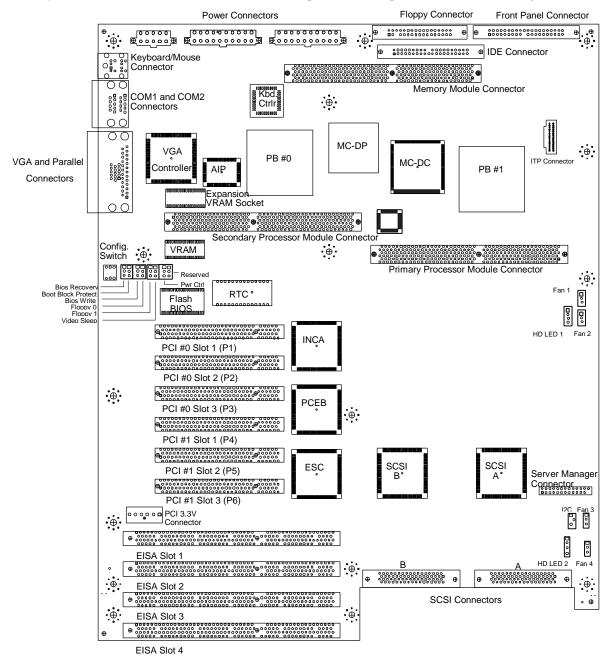

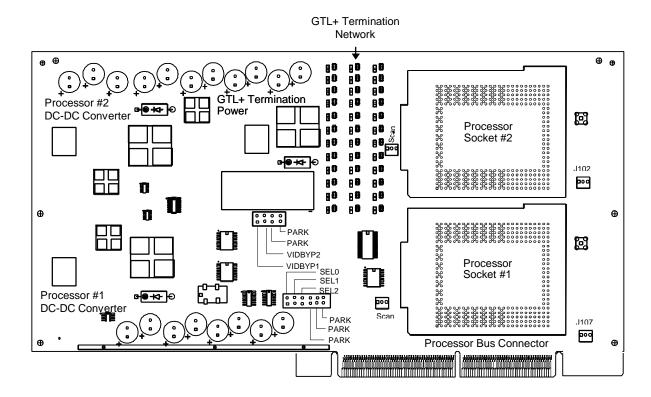

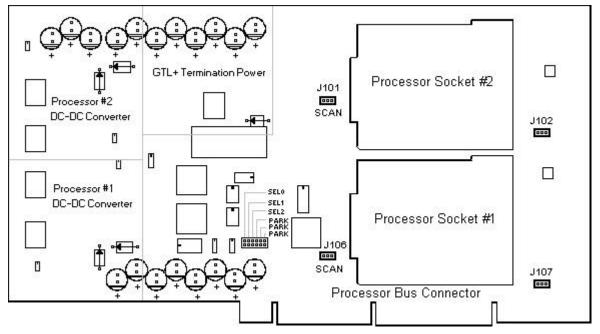

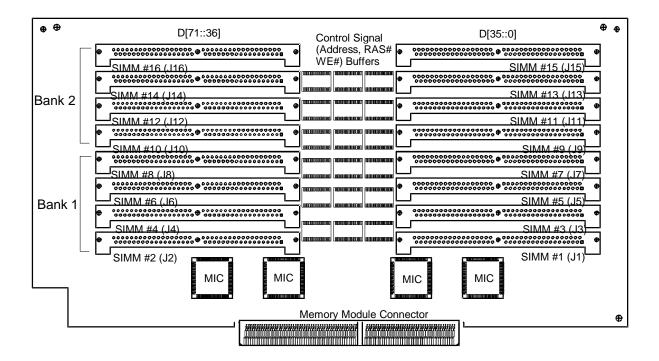

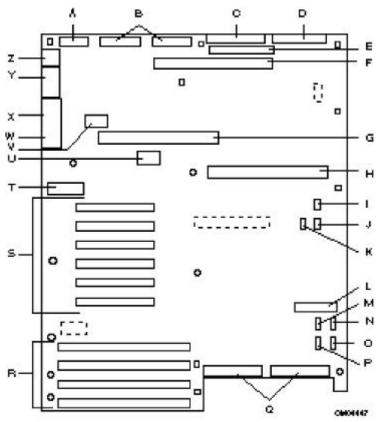

The following diagram shows the placement of major components and connector interfaces on the system baseboard, and the modules. See Chapter 5 for complete mechanical drawings.

Figure 1.2 Baseboard Layout

Figure 1.3 Fab 3.x Processor Module Layout (supports 166MHz/512KB processors only)

Figure 1.4 Fab 4.x Processor Module Layout (supports both 166MHz/512KB & 200MHz/512KB processors)

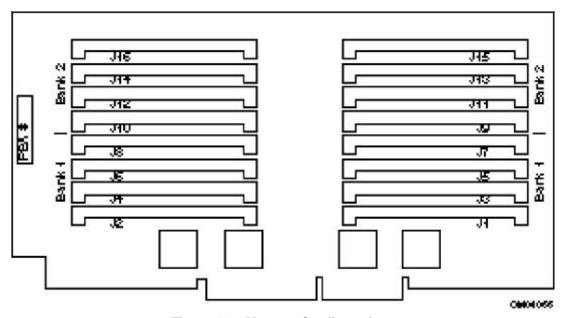

Figure 1.5 1GB Memory Module Layout

Figure 1.6 4GB Memory Module Layout

#### 1.5 Connector Locations

Baseboard connector locations are shown in the figure below. See Appendix C for the connector pinouts.

Figure 1.7 AP450GX Board Set Connectors

- \*\* Comments in italics are applicable when the board set is installed into Intel's AP450GX chassis.

- A Power control and status connector (PS3)

- B +5V, +12V, and 3.3V power connectors (PS1 and PS2) (identical)

- C Diskette drive connector

- D Front panel connector

- E IDE drive connector

- F Memory module connector

- G Secondary processor module (or termination module) connector

- H Primary processor module connector

- Fan 1 connector (not used, fan sense jumper should be installed)

- J Fan 2 connector (inner chassis fan)

- K Hard drive LED 1 connector (not used)

- L Connector for optional Server Management Module (SMM)

- M I<sup>2</sup>C connector (not used)

- N Fan 3 connector (upper outer chassis fan)

- O Fan 4 connector (lower outer chassis fan)

- P Hard drive LED 2 connector (not used)

- Q SCSI bus connectors: Channel A to the right, Channel B to the left

- R EISA slots 1 4 for add-in boards (slot 1 toward top, 4 toward bottom)

- S PCI slots 1 6 for add-in boards (slot 1 toward top, 6 toward bottom: PCI Bus 0 = slots 1 3; PCI Bus 1 = slots 4 6)

- T Configuration switches and jumpers

- U Real-time clock

- V Video DRAM expansion socket

- W VGA monitor connector (bottom)

- X Parallel port connector (top)

- Y Serial port connectors -- Port 1 (top), Port 2 (bottom)

- Z PS/2-compatible keyboard and mouse connectors (interchangeable)

Three connectors are shown in the board drawing as dotted-line boxes. They are not used in this system configuration. Their functions are as follows:

- ITP (In-target Probe): Located near the upper right corner of the baseboard for low level system debug.

- PCI test connector: Blue connector near middle of board (not used)

- 3.3V PCI power connector: Located near the lower left corner, below the PCI slots.

# 1.6 Microprocessor

The Pentium Pro processor utilizes a 387-pin dual-cavity PGA package. The package contains two devices: a 5.5 million transistor processing core with 8 KByte primary cache, and 32 million transistor 512 KB secondary cache (L2 cache).

The AP450GX Board Set operates with Pentium Pro processors whose voltage may range from 2.1V to 3.5V and are Voltage ID (VID) enabled (i.e. the processors have the ability to ask for a certain voltage). A voltage regulator circuit on the processor module makes use of the VID capabilities to automatically adjust its voltage output to match that of the installed processor. The board set also has jumpers allowing processors ranging from 133 to 266 MHz to be installed. It should be noted, however, that there will be limitations on which processors will be supported.

The following table indicates which steppings of the Pentium Pro processor can be mixed within the same system. An "X" denotes which steppings can be mixed and a blank indicates the AP450GX MP Server Board Set does not support the given stepping combination.

sA1/a sA1/b sA1/b sB1/b sB1/b Stepping (Proc/Cache) 166 Frequency 166 200 166 200 512 512 512 512 **Cache Size** Stepping ID 0617 0617 0617 0619 0619 QDF# SL22X SY034 SY047 SY048 SL22Z SY034 X X X X X X SY047 X SY048 X SL22X X X X SL22Z X X

**Table 1.1 Supported Processor Combinations**

#### NOTES:

- 1. The BIOS used must support each stepping installed in the system.

- 2. If the sB1 stepping of the Pentium® Pro processor is installed, BIOS revision 1.00.08.CD0 or later is required.

- 3. Refer to erratum 34 in the Pentium Pro Processor Specification Update for issues related to the sB1 stepping of the Pentium Pro processor.

- 4. Though Intel recommends using identical steppings of processor silicon in multiprocessor systems whenever possible (as this is the only configuration which receives full validation across all of Intel's testing), Intel supports mixing processor steppings, and does not actively prevent various steppings of the Pentium Pro processor from working together in multiple processor (MP) systems. However, since Intel cannot validate every possible combination of devices, each new stepping of a device is fully validated only against the latest steppings of other processors and chipset components. Refer to Specification Change 1 of the Pentium Pro Processor Specification Update for further details on issues related to mixed processor steppings in an MP system.

An approved Pentium Pro processor heatsink (Intel part #644591-002) is necessary for proper thermal dissipation. The processor/heatsink assembly must be securely fastened to the socket by two clips (Intel part #637885-002). These clips fit over the heatsink assembly and attach to the outer wide tabs of the socket assembly. The heat sink must use thermal grease for proper heat dissipation for any processor greater than 35W (i.e. the 200MHz/512KB). "Foil pads" with grease on them will not properly cool a >35W processor. A heat sink kit is available that contains the proper heatsink, two clips and thermal grease. The current Intel order code is ALHSINKKIT.

The Pentium Pro processor maintains full backward compatibility with the 8086, 80286, Intel386<sup>TM</sup>, Intel486<sup>TM</sup> and Pentium® processors. It also has a numeric coprocessor that significantly increases the speed of floating point operations, while maintaining backward compatibility with the i486DX math coprocessor and complying with ANSI/IEEE standard 754-1985.

#### **CAUTION**

Do not use the older style of bail-wire clips for securing the heatsink assembly. These clips have been found to cause damage when installed or removed incorrectly.

#### 1.6.1 Processors and Processor Modules

The processor module will support up to two Pentium® Pro processors. The two processor sites are ZIF socketed, so that only one might be installed at the time of shipment with upgrades to be added later. Each processor module contains termination circuitry required by the GTL+ signaling environment, DC to DC converters for proper power to each processor, an I²C controller, and logic for I²C support and clock ratio programming. Each processor module has three DC-DC converters: one for the 1.5V GTL+ termination voltage, and two identical converters for the processors. The processor converters are supplied from the +12V supply. The GTL+ converter is supplied from the +12V supply on Fab 3.x processor modules (identified as 647428-xxx), or from the 3.3V supply on Fab 4.x processor modules (identified as 659506-xxx). The Fab 4.x processor modules will support up to a 40W processor (i.e. the 200MHz/512KB). The Fab 3.x processor modules will only supply enough current for up to a 35W processor (i.e. the 166MHz/512KB).

#### 1.7 Bus Termination Module

This module is required when only one processor module is installed in the system. The terminator module provides GTL+ signal termination and voltage regulation. When used, this module must be installed in the secondary processor module slot on the system. The terminator module contains a single DC-DC converter which provides the 1.5V termination voltage. This converter is driven from the +12V supply.

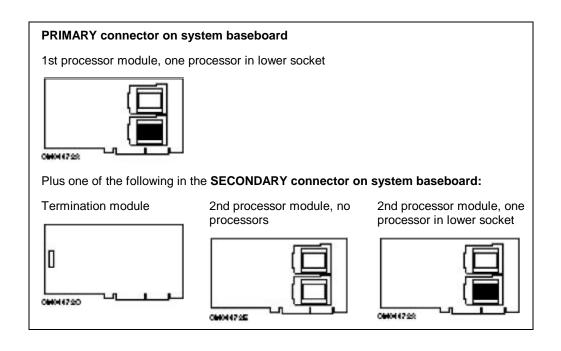

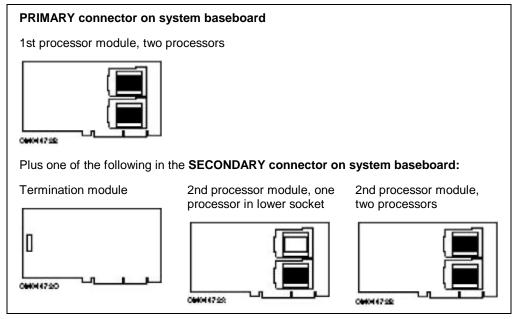

# 1.8 Processor Population Order

The system baseboard has a primary processor module connector and a secondary processor module connector. A processor module can have one or two Pentium Pro processors installed. The figures that follow show the different supported population orders for 1, 2, 3 or 4 processors. Other processor configurations are not supported.

# Processor board connectors on system baseboard

- A System baseboard

- B Connector for secondary processor module or bus termination module

- C Connector for primary processor module

**Figure 1.8 Processor Module Connector Locations**

**Figure 1.9 Processor Configuration Models**

Refer to section 1.21 for the processor module jumper configurations.

# 1.9 Memory

#### 1.9.1 System Memory

The memory subsystem consists of the memory chip set, the memory module connector on the system baseboard, and the memory module itself. The system baseboard contains the data path and data control portions of the chip set. The memory module contains the buffer devices from the chip set and 16 SIMM sites for up to 1 GB of system memory (using 64MB SIMMs) and 2 GB of system memory (using 128MB SIMMs). DRAM SIMMs on the module are organized as two 72-bit wide, 2-, or 4-way interleaves and 1 or 2 banks. SIMM sites accept 72-pin single- or double-sided SIMMs (60 or 70ns SIMMs only). All SIMMs in a bank must be identical (same size and speed).

Memory error checking and correction is supported via ECC logic in the chip set while using standard parity SIMM/DIMMs. The chip set will detect double bit errors and correct single bit errors. Errors may be generated by a defective memory module or soft errors. When a bad SIMM/DIMM is detected (i.e. a double bit error), during booting the BIOS will automatically downsize memory to eliminate the bad SIMM/DIMM location.

The 1GB memory module is available in two versions. Both are functionally identical except for the type of metal used in the SIMM connector and the type of capacitors used. One version has tin lead SIMM connectors and must be used with tin lead SIMMs. The other version is available with gold lead SIMM connectors and must be used with gold lead SIMMs. The gold lead module also has fused tantalum capacitors. The tin lead version simply has non-fused tantalum capacitors. There are separate order codes for each version. See Appendix B for the specific order codes.

Only use SIMMs approved for use in this system. Contact your Intel representative for an updated list of qualified SIMMs and DIMMs.

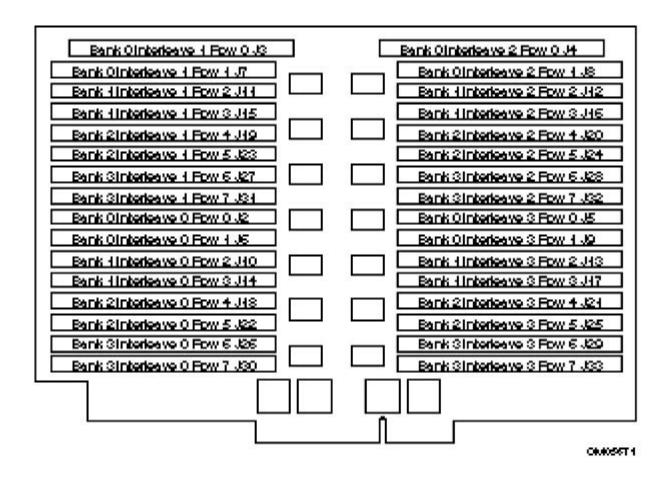

# 1.9.2 Memory Installation Options (1GB Memory Module)

The following SIMM interleaving options are supported:

- Two-way interleave, J1 through J4;

- Four-way interleave, single bank, J1 through J8

- Four-way interleave, dual bank, J1 through J16.

Figure 1.10 Memory Configurations

The 1GB memory module has 16 SIMM sockets, arranged in two banks. The system automatically detects system memory installed, so jumpers do not need to be set to specify memory size although the SCU must be run after you change the memory configuration. See Chapter 3 for details.

**Table 1.2 Supported Memory Options**

| Memory Size                                                                                                             | Bank Installation                                                                         | SIMM Type                                                                                                                                     |

|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Minimum memory configuration is 64 MB of                                                                                | Always begin with the bottom SIMM sites (lowest number is                                 | Use 16 MB, 64MB or 128 MB single-sided SIMMs or 32 MB double-sided SIMMs.                                                                     |

| DRAM (with four 16 MB SIMMs installed in J1, J2, J3, and J4).                                                           | J1) as you fill the board sockets.  All SIMMs in a bank must be                           | Use only 36-bit, 72-pin, 60 or 70ns fast page mode SIMMs, single- or double-sided. (Single-sided refers to the                                |

| Maximum memory configuration is 1GB of                                                                                  | identical (same size and speed).                                                          | addressing method, not to the physical layout of the SIMM.)                                                                                   |

| DRAM (with 64 MB SIMMs installed in each socket, J1 through J16). Maximum memory configuration is 2GB with 128MB SIMMs. | SIMMs in bank 1 may differ in size from the SIMMs in bank 2, but may not differ in speed. | Use the 1 GB memory module with tin lead SIMM connectors when using tin lead SIMMs. Use the 1 GB memory module with gold lead SIMM connectors |

|                                                                                                                         | Number of SIMMs supported: 4, 8, or 16 only.                                              | when using gold lead SIMMs.                                                                                                                   |

|                                                                                                                         | ·                                                                                         | Use JEDEC-compatible SIMMs. Contact your Intel representative for a list of approved SIMMs.                                                   |

# 1.9.3 Memory Performance Hints

Memory performance, and thus system performance, can be increased by changing the number of interleaves, number of banks and the speed of memory installed. For more information about system performance, refer to the *AP450GX MP Server System Performance Brief*.

#### 1.9.4 4GB Memory Module

An optional 4GB memory module is available and will support up to 4GB of memory using 128MB DIMMs. This module fits into the same memory module connector the 1GB module fits into and has the same mechanical form factor. The additional memory capacity is accomplished with the use of TOSP DRAM's packaged in JEDEC standard 16Mx72 60ns DIMMs only. Note these are 3.3V DIMMs, while the 1GB module uses 5V SIMMs. The DIMMs are also installed at a 90° angle to the memory module (vs. 45° for the 1GB memory module) and are 1.25" high. The 4GB module contains 32 DIMM sockets, which when populated in groups of 4 DIMMs, offers memory capacity options of 0.5GB through 4GB in 0.5GB increments. Memory on the module is organized in 8 banks and 4-way interleaves.

# 1.9.4.1 DIMM Requirements

The 4GB memory module will only support a 128MB DIMM which meet JEDEC Standard No. 21-C, Release 4. In addition the DIMM must utilize TSOP DRAMs and must not exceed 0.157" in width. Two JDEC standard options with identical mechanical pinouts are listed below.

- 1. 16Mx72 Fast Page Mode DRAM DIMM with ECC, 8K refresh, 3.3 V, 16Mx4 DRAM based, 13 row addresses, 11 column addresses internally.

- 2. 16Mx72 Fast Page Mode DRAM DIMM with ECC, 4K refresh, 3.3 V, 8Mx8/9 DRAM based, 12 row addresses, 11 column addresses internally.

Only use DIMMs approved for use in this system. Contact your Intel representative for an updated list of qualified SIMMs and DIMMs.

# 1.9.4.2 Memory Installation Options (4GB Memory Module)

For the 4GB memory module the following DIMM population procedure must be used. The DIMMs are to be populated from J2 through J33 consecutively in groups of 4. All configurations result in a four-way memory interleave. Refer to Figure 1.6.

**Memory Capacity DIMM** population instructions 0.5 GB populate J2, J3, J4, J5 1.0 GB add J6, J7, J8, J9 1.5 GB add J10, J11, J12, J13 2.0 GB add J14, J15, J16, J17 2.5 GB add J18, J19, J20, J21 3.0 GB add J22, J23, J24, J25 3.5 GB add J26, J27, J28, J29 4.0 GB add J30, J31, J32, J33

**Table 1.3 Supported 4GB Memory Module Options**

# 1.9.5 Memory Configuration Options

Error correction and detection, memory downsizing and address bit permuting are capabilities supported by both the 1GB and 4GB memory modules. Some options work slightly differently depending on the module and are described in the following sections.

#### 1.9.5.1 Error Detection and Correction

The memory controller of the Intel 450GX PCIset performs run-time correction of single bit errors and detects double bit errors. Because a double bit error is not correctable, system operation once a double bit error has been detected is unpredictable and dependent on the operating system's ability to recover from it. Both single and double bit errors are recorded in the system error log if error reporting is enabled.

# 1.9.5.2 Memory Downsizing

During POST the BIOS performs a check of memory to insure all SIMMs/DIMMs are fully functional. Should a bad memory location be detected during POST, the BIOS will resize memory to eliminate the bad memory location. Unlike some memory resizing algorithms which will eliminate an entire SIMM/DIMM module from the system if a bad memory location is detected, the memory resizing algorithm used in the AP450GX system maintains the current memory configuration (i.e. same number of SIMM/DIMMs, same number of banks, same number of interleaves) and eliminates only the bad memory location. This is done by reducing the amount of memory used by each SIMM/DIMM until the bad memory location is no longer allocated.

When an error is detected, the BIOS first determines which bank is affected by the error. The memory allocation for the affected bank is then decreased by a power of two (i.e. only half the memory of each SIMM/DIMM will be allocated). The BIOS will continue decreasing the affected banks memory size by a power of two until the bad memory location is no longer allocated. A BIOS error will also be displayed indicating memory has been resized. If memory for the affected bank is decreased to 4MB and the bad memory location cannot be eliminated, the BIOS will display an error message and will not boot.

The above algorithm is identical for both the 1GB and 4GB memory modules.

If double-sided (also called double-banked) SIMMs are used on the 1GB Memory Module, ECC memory errors may be reported on banks 1-4, even though the Memory Module only contains two physical memory banks. In this case, ECC errors on bank #1 would indicate a bad SIMM location in sockets J1-J8 and the error is on the front side of the SIMM. ECC errors on bank #2 would indicate a bad SIMM location in sockets J1-J8 and the error is on the back side of the SIMM. ECC errors on bank #3 would indicate a bad SIMM location in sockets J9-J16 and the error is on the front side of the SIMM. ECC errors on bank #4 would indicate a bad SIMM location in sockets J9-J16 and the error is on the back side of the SIMM.

#### 1.9.5.3 Address Bit Permuting

The 450GX PCIset has a performance enhancing feature called Address Bit Permuting (ABP). ABP, if enabled, swaps memory row selection bits with the lower order bits in the address. In some applications this can improve system performance by increasing the number of row misses and thus decreasing the number of precharge penalties. ABP can be enabled under certain memory configurations. These configurations are listed below for each memory module. The ABP option in the BIOS setup (Advanced Chip Set Menu) must also be enabled.

#### **1GB Memory Module**

ABP can be enabled by the BIOS if all of the following are true:

- ABP BIOS option set to enabled

- Same speed SIMMs in both banks

- Same sized SIMMs in both banks

Note: The ABP bit in the  $I^2C$  register is used to allow ABP with single sided SIMMs and will only be set if all of the above are true and the SIMMs installed in the system are single-sided. ABP will still be enabled if all of the above are true and double sided SIMMs are installed, but the  $I^2C$ register bit will not be set.

#### **4GB Memory Module**

ABP can be enabled by the BIOS if all of the following are true:

ABP BIOS option set to enabled

- Same speed DIMMs in all banks

- The module is populated in a two (1GB), four (2GB) or eight (4GB) bank configuration.

Note: ABP will not be enable if populated in a one, three, five, six or seven bank configuration.

#### 1.10 Intel 450GX PCIset

The Intel 450GX PCIset (B0 stepping & C0 stepping) consists of two functional groups, the PCI controller and the memory controller. The PCI controller consists of a single 82454GX PCI Bridge (PB) component, which supports PCI Bus mastering. Two of 82454GX components are on the system baseboard, each supporting a single PCI (peer) bus. The memory controller consists of six components; the 82452GX (DP) Data Path component, 82453GX (DC) Data path Controller, and the 82451GX (MIC) Memory Interface Controller. The DP and DC each reside on the system baseboard. Four of the MIC components are located on the memory module.

#### 1.11 Onboard SCSI Controllers

The baseboard includes two embedded wide SCSI-2 controllers (Adaptec AIC-7880, channels A and B) integrated as PCI bus masters. The controllers support data path widths of 8-bit (narrow SCSI) at a data transfer rate of 10 MB/sec, 16-bit (wide fast SCSI) at a data transfer rate of 20 MB/sec and 16-bit (Fast-20/Ultra) at a data trasfer rate of 40MB/sec. As PCI bus masters, these controllers support data transfer rates of 133 MB/sec.

You can connect up to seven 8-bit narrow SCSI devices or up to fifteen 8-bit narrow and/or 16-bit wide SCSI devices and one controller (maximum of seven 8-bit narrow devices) to each channel. Devices can be tape drives, printers, optical media drives, and other devices. Narrow SCSI devices are not supported in Fast-20/Ultra mode.

Active termination must be provided on the far end of the SCSI bus to ensure proper termination of the bus. The baseboard provides active termination at the near end.

Active negation outputs reduce the chance of data errors by actively driving both polarities of the SCSI bus and avoiding indeterminate voltage levels and common-mode noise on long cable runs. The SCSI output drivers can directly drive a 48 mA, single-ended SCSI bus with no additional drivers.

# 1.12 EISA Expansion Slots

The baseboard has four EISA bus slots. The EISA bus is an extension of the Industry Standard Architecture (ISA) bus. Because EISA is fully backward-compatible with ISA, you can install EISA or ISA add-in boards and software in your server. This compatibility is handled by the PCEB and ESC chip set components on the system baseboard.

The EISA bus provides:

- 32-bit memory addressing

- Type A transfers at 5.33 MB per second

- Type B transfers at 8 MB per second

- Burst transfers at 33 MB per second

- 8-, 16-, or 32-bit data transfers

- Automatic translation of bus cycles between EISA and ISA masters

- Interrupt sharing

All four slots have the capability of being bus masters. When EISA masters arbitrate for the bus, the following pairs of slots share arbitration requests: 1 and 2, 3 and 4. Therefore, in the round-robin scheme of letting EISA masters take over the bus, ownership of it occurs in the following sequence: 1, 2, 3, 4, 1, 2, 3, 4, etc.

# 1.13 PCI Expansion Slots

The system baseboard has six, 32 bit, PCI 2.0 compliant bus slots. The PCI subsystem consists of two I/O bus segments. PCI #0 is the primary or compatibility bus segment, running always at 33 MHz. PCI #0 connects the processor bus to the INCA (Intel's Interrupt Controller ASIC), a PCI/EISA bridge, and three PCI connectors. PCI #1 connects the processor bus to two embedded wide SCSI controllers and three PCI connectors. PCI #1 also always runs at 33MHz. The architecture supports Host-to-PCI, PCI-to-Memory, PCI-to-EISA, EISA-to-Memory, and PCI-to-PCI transfers. The PCI bus provides:

- 32 and 64-bit memory addressing

- +5 V and + 3 V signaling environments

- Burst transfers at 133 MB per second

- 8-, 16-, or 32-bit data transfers

- Plug-and-play configuration

- PeerBus to maximize throughput

The INCA device provides these features:

- PCI clock generation: 14 PCI clocks (7 per PCI segment)

- Three buffered clocks

- Interrupt control

- Arbitration support for six PCI masters on PCI #1

- General purpose I/O ports: two 8-bit I/O ports for control or status

- 3-mode diskette control support

- DMA steering for IDE and parallel port to 1 of 4 DRQs/DACKs

- Keyboard emulation

- Support for front panel interface and LCD

- Security features: watchdog timer (software start/reset) resets system if it expires; monitors keyboard/mouse; monitors system baseboard voltage (+12V, -12V, +5V, -5V, +3.3V); monitors baseboard temperature and chassis door switch

#### 1.14 Boot Order

When the system boots, it will look for a bootable device in a certain order. The system will then boot off the first bootable device it finds. Below is the order in which the system will look for bootable devices.

- 1. Floppy Drive

- 2. IDE Drive

- 3. E1 (EISA bus slot #1)

| 4.  | E2     | (EISA bus slot #2)                  |

|-----|--------|-------------------------------------|

| 5.  | E3     | (EISA bus slot #3)                  |

| 6.  | E4     | (EISA bus slot #4)                  |

| 7.  | P1     | (PCI Bus#0, slot 1)                 |

| 8.  | P2     | (PCI Bus#0, slot 2)                 |

| 9.  | P3     | (PCI Bus#0, slot 3)                 |

| 10. | P4     | (PCI Bus#1, slot 1)                 |

| 11. | SCSI A | (On-board AIC-7880 SCSI controller) |

| 12. | SCSI B | (On-board AIC-7880 SCSI controller) |

| 13. | P5     | (PCI Bus#1, slot 2)                 |

| 14. | P6     | (PCI Bus#1, slot 3)                 |

#### **Notes:**

- The actual boot order on the EISA bus may change depending on how the devices installed on the EISA bus are configured, but the EISA bus will always be scanned for bootable devices before the PCI buses.

- If a PCI-to-PCI bridge device (P2P) is installed in the system, the boot order will change and may vary depending on the configuration. Typically, if a P2P is installed in P2, for example, the boot order will likely look for a bootable device on the P2P before looking at P3. However under some circumstance, the system may actually go to P3 before looking for a bootable device on the P2P.

# 1.15 Super VGA Controller

The onboard, integrated Cirrus Logic CL-GD5424 super VGA controller (ISA based) is fully compatible with these video standards: CGA, EGA, Hercules Graphics, MDA, and VGA. The standard system configuration comes with 512 KB of onboard 70ns video memory. You can optionally expand the onboard video memory buffer size to 1 MB by adding one 40-pin 256 K x 16, 70 ns fast-page DRAM. Contact your Intel representative for an updated list of qualified video memory. The SVGA controller supports only analog monitors (single and multiple frequency, interlaced and noninterlaced) with a maximum vertical retrace interlaced frequency of 87 Hz.

The BIOS will automatically disable the onboard video if another add-in video adapter is installed into the system baseboard. Note, however, the BIOS will only support add-in video adapters in the first PCI bus (slots P1-P3). Video adapters placed in the second PCI bus (slots P4-P6 will not be recognized).

- Supported with 512 KB memory: Pixel resolutions of 640 x 480 x 256 colors, and 800 x 600 and 1024 x 768 in 16 colors.

- Supported with 1 MB memory (optional): 132-column text modes and high resolution graphics with 1280 x 1024 x 16 colors. Depending on the environment, the controller displays up to 64,000 colors in some video resolutions.

**Table 1.4 Standard VGA Modes**

| Mode(s)<br>in Hex | Colors<br>(number<br>/palette size) | Resolution | Pixel Freq.<br>(MHz) | Horiz. Freq.<br>(KHz) | Vert. Freq.<br>(Hz) |

|-------------------|-------------------------------------|------------|----------------------|-----------------------|---------------------|

| 0, 1              | 16/256K                             | 360 X 400  | 14                   | 31.5                  | 70                  |

| 2, 3              | 16/256K                             | 720 X 400  | 28                   | 31.5                  | 70                  |

| 4, 5              | 4/256K                              | 320 X 200  | 12.5                 | 31.5                  | 70                  |

| 6                 | 2/256K                              | 640 X 200  | 25                   | 31.5                  | 70                  |

| 7                 | Mono                                | 720 X 400  | 28                   | 31.5                  | 70                  |

| D                 | 16/256K                             | 320 X 200  | 12.5                 | 31.5                  | 70                  |

| E                 | 16/256K                             | 640 X 200  | 25                   | 31.5                  | 70                  |

| F                 | Mono                                | 640 X 350  | 25                   | 31.5                  | 70                  |

| 10                | 16/256K                             | 640 X 350  | 25                   | 31.5                  | 70                  |

| 11                | 2/256K                              | 640 X 480  | 25                   | 31.5                  | 60                  |

| 12                | 16/256K                             | 640 X 480  | 25                   | 31.5                  | 60                  |

| 12+               | 16/256K                             | 640 X 480  | 31.5                 | 37.5                  | 75                  |

| 13                | 256/256K                            | 320 X 200  | 12.5                 | 31.5                  | 70                  |

Table 1.5 Extended VGA Modes

| Mode(s)<br>in Hex | Colors (number /palette size  | Resolution  | Pixel Freq.<br>(MHz) | Horiz. Freq.<br>(KHz) | Vert. Freq.<br>(Hz) |

|-------------------|-------------------------------|-------------|----------------------|-----------------------|---------------------|

| 14, 55            | 16/256K                       | 1056 X 400  | 41.5                 | 31.5                  | 70                  |

| 54                | 16/256K                       | 1056 X 350  | 41.5                 | 31.5                  | 70                  |

| 58, 6A            | 16/256K                       | 800 X 600   | 40                   | 37.8                  | 60                  |

| 58, 6A            | 16/256K                       | 800 X 600   | 49.5                 | 46.9                  | 75                  |

| 5C*               | 256/256K                      | 800 X 600   | 36                   | 35.2                  | 56                  |

| 5C*               | 256/256K                      | 800 X 600   | 40                   | 37.9                  | 60                  |

| 5C*               | 256/256K                      | 800 X 600   | 49.5                 | 46.9                  | 75                  |

| 5D                | 16/256K (interlaced)          | 1024 X 768  | 44.9                 | 35.5                  | 87                  |

| 5D                | 16/256K                       | 1024 X 768  | 65                   | 48.3                  | 60                  |

| 5D                | 16/256K                       | 1024 X 768  | 75                   | 56                    | 70                  |

| 5D                | 16/256K                       | 1024 X 768  | 78.7                 | 60                    | 75                  |

| 5F                | 256/256K                      | 640 X 480   | 25                   | 31.5                  | 60                  |

| 5F                | 256/256K                      | 640 X 480   | 31.5                 | 37.5                  | 75                  |

| 60*               | 256/256K (interlaced)         | 1024 X 768  | 44.9                 | 35.5                  | 87                  |

| 60*               | 256/256K                      | 1024 X 768  | 65                   | 48.3                  | 60                  |

| 60*               | 256/256K                      | 1024 X 768  | 75                   | 56                    | 70                  |

| 60*               | 256/256K                      | 1024 X 768  | 78.7                 | 60                    | 75                  |

| 64*               | 64K                           | 640 X 480   | 25                   | 31.5                  | 60                  |

| 64*               | 64K                           | 640 X 480   | 31.5                 | 37.5                  | 75                  |

| 65*               | 64K                           | 800 X 600   | 36                   | 35.2                  | 56                  |

| 65*               | 64K                           | 800 X 600   | 40                   | 37.8                  | 60                  |

| 65*               | 64K                           | 800 X 600   | 49.5                 | 46.9                  | 75                  |

| 66*               | 32K Direct/256 Mixed          | 640 X 480   | 25                   | 31.5                  | 60                  |

| 66*               | 32K Direct/256 Mixed          | 640 X 480   | 31.5                 | 37.5                  | 75                  |

| 67*               | 32K Direct/256 Mixed          | 800 X 600   | 40                   | 37.8                  | 60                  |

| 67*               | 32K Direct/256 Mixed          | 800 X 600   | 49.5                 | 46.9                  | 75                  |

| 6C*               | 16/256K (interlaced)          | 1280 X 1024 | 75                   | 48                    | 87                  |

| 6C*               | 16/256K                       | 1280 X 1024 | 108                  | 65                    | 60                  |

| 6D*               | 256/256K (interlaced)         | 1280 X 1024 | 75                   | 48                    | 87                  |

| 6D*               | 256/256K                      | 1280 X 1024 | 108                  | 65                    | 60                  |

| 71*               | 16M                           | 640 X 480   | 25                   | 31.5                  | 60                  |

| 72*               | 16M 32-bit/pixel              | 800 X 600   | 40                   | 37.8                  | 60                  |

| 73*               | 16M 32-bit/pixel (interlaced) | 1024 X 768  | 44.9                 | 35.5                  | 87                  |

| 74*               | 64K (interlaced)              | 1024 X 768  | 44.9                 | 35.5                  | 87                  |

| 74*               | 64K                           | 1024 X 768  | 65                   | 48.3                  | 60                  |

| 74*               | 64K                           | 1024 X 768  | 75                   | 56                    | 70                  |

| 74*               | 64K                           | 1024 X 768  | 78.7                 | 60                    | 75                  |

| 75*               | 64K (interlaced)              | 1280 X 1024 | 75                   | 48                    | 87                  |

| 76*               | 16M 32-bit/pixel              | 640 X 480   | 25                   | 31.5                  | 60                  |

| 76*               | 16M 32-bit/pixel              | 640 X 480   | 31.5                 | 37.5                  | 75                  |

$<sup>\</sup>ensuremath{^{*}}$  Requires 1MB video memory option.

# 1.16 Keyboard and Mouse

The 8742 keyboard controller is PS/2-compatible. The system may be locked automatically if there is no keyboard or mouse activity for a predefined length of time, as specified through the Setup utility. The default keystroke combination to enable this feature is <Ctrl + Alt + Backspace>. Once the inactivity timer has expired, the keyboard or mouse does not respond until the previously stored password in the keyboard controller is entered. The keyboard LED will blink until the password is entered.

The mouse is disabled on power-up; in this state, interrupt IRQ12 is available for use by add-in boards, and the mouse clock input to the keyboard controller is connected to the mouse clock output, with no connection to the external mouse.

# 1.17 Advanced Integrated Peripheral (AIP)

The AIP resides on the EISA bus and contains a floppy disk controller (FDC), 2 serial ports, a multifunction parallel port and an IDE interface.

# 1.17.1 Floppy Drive Support

The FDC on the AIP is functionally compatible with the 82077SL, 82077AA and 8272A floppy disk controllers and can provide a data rate up to 2MB/s. The FDC will support up to two floppy disk drives.

#### 1.17.2 Serial Ports

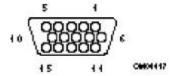

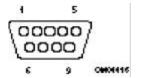

Two 9-pin serial ports are provide in a single stacked housing (ports 1 and 2). Port 1 is located on the top, port 2 on the bottom. Both serial ports are 16550 compatible with 16-byte FIFO's. Each serial port can be set to 1 of 4 different COM ports (via the BIOS setup), and can be enabled separately. When enabled, each port can be programmed to generate edge or level sensitive interrupts. When disabled, serial port interrupts are available to adapter cards.

#### 1.17.3 Parallel Port

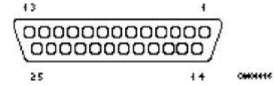

A single PS/2 compatible 25-pin bi-directional parallel port is provided. The parallel port supports Extended Capabilities Port (ECP) protocol with DMA, EPP protocol and IEEE 1284 protocol for PS/2 bi-directional compatibility. The parallel port can be enabled or disabled via the BIOS setup. When disabled, the interrupt is available to adapter cards.

# 1.17.4 IDE Support

IDE is an 8-bit or 16-bit interface for intelligent disk drives with AT disk controller electronics onboard. AC timing constraints allow only Type 2 IDE drives in the CAM specification (or faster) to be supported. The processor can transfer data from the IDE interface at a maximum transfer rate of 2.4Mbytes per second. This IDE implementation will also support DMA to the IDE device, which has a maximum transfer rate of 4.2Mbytes per second. Typical IDE devices can access data a peak rate of 1.2Mbytes per second. Therefore, the usage of DMA will significantly reduce the bus utilization (with respect to IDE device access), and will significantly improve system performance.

The IDE interface can be disabled. It is disabled on reset; in this state, the I/O address space and interrupt IRQ14 are available for add-in modules. The system BIOS may disable the interface when it finds the registers of another hard disk controller.

#### 1.18 Miscellaneous Functions

The board set provides the additional miscellaneous functions listed below:

- I<sup>2</sup>C Diagnostic Bus

- Server Management Connector

- System Fan Interface

- Hard Drive LED Interface

# 1.18.1 I<sup>2</sup>C Diagnostic Bus

The baseboard has an integral I<sup>2</sup>C (Inter-Integrated Circuit) bus which can be used for general purpose system management such as providing module revision or status information from anywhere in the system. This bus is routed to processor and memory modules, the front panel and power supply connectors, the Server Management Connector and a single user connector on the baseboard.

A Philips PCF8584 I<sup>2</sup>C controller is mapped into EISA I/O space and can be used by system software to access the I<sup>2</sup>C bus. The 8584 appears at addresses CA0h and CA1h. The interrupt from the 8584 is routed to input PCI8 on the INCA component.

The baseboard, processor, memory and terminator modules have PCF8574 and PCF8474A I/O devices on them. These are 8-bit devices that connect the I<sup>2</sup>C bus and provide system information from each module. Below is the I<sup>2</sup>C base address for each component.

| Component                                 | I <sup>2</sup> C Base Address |

|-------------------------------------------|-------------------------------|

| Baseboard                                 | 0x40                          |

| Primary Processor Module Slot             | 0x70                          |

| Secondary Processor Module Slot           | 0x72                          |

| Primary Processor Module Slot, Reserved   | 0x90                          |

| Secondary Processor Module Slot, Reserved | 0x92                          |

| Memory Module                             | 0x42                          |

The information available from each module when accessed via the I<sup>2</sup>C bus is shown in the following table along with the bit definitions.

Table 1.6 Baseboard I<sup>2</sup>C Bit Map

| Bit | Bit Name     | Description                                                                           |  |

|-----|--------------|---------------------------------------------------------------------------------------|--|

| 2:0 | BRDREV(2:0)  | Baseboard board revision ID                                                           |  |

|     |              | 001 = Fab 1                                                                           |  |

|     |              | 010 = Fab 2                                                                           |  |

|     |              | 011 = Fab 3                                                                           |  |

| 6:3 | RESERVED     | Reserved                                                                              |  |

| 6:3 | FANFAIL(3:0) | A zero (0) indicates a failed fan. Bits 6:3 are valid as FANFAIL when bit $7 = "1"$ . |  |

|     |              | bit 3 = fan 4 (Outer chassis fan, lower)                                              |  |

|     |              | bit 4 = fan 3 (Outer chassis fan, upper)                                              |  |

|     |              | bit 5 = fan 2 (Inner chassis fan)                                                     |  |

|     |              | bit 6 = fan 1 (Not used in AP450GX MP Server chassis)                                 |  |

|     |              | (not a supported feature)                                                             |  |

| 7   | FANFAILSEL   | When "1", bits 6:3 are fan fail                                                       |  |

|     |              | When "0", bits 6:3 are Reserved                                                       |  |

|     | 2            | (not a supported feature)                                                             |  |

Table 1.7 Processor Module I<sup>2</sup>C Bit Map

| Bit | Bit Name    | Description                                                                                                       |

|-----|-------------|-------------------------------------------------------------------------------------------------------------------|

| 2:0 | P6ID(2:0)   | Pentium® Pro processor core/bus frequency ID                                                                      |

|     |             | 000 = 150/60 MHz                                                                                                  |

|     |             | 001 = 180/60 MHz                                                                                                  |

|     |             | 010 = 210/60 MHz                                                                                                  |

|     |             | 011 = 240/60 MHz                                                                                                  |

|     |             | 100 = 166/66 MHz                                                                                                  |

|     |             | 101 = 200/66 MHz                                                                                                  |

|     |             | 110 = 233/66 MHz                                                                                                  |

|     |             | 111 = 266/66 MHz                                                                                                  |

| 4:3 | Reserved    |                                                                                                                   |

| 5:3 | BRDREV(0:2) | Processor Module Board Revision ID                                                                                |

|     |             | 000 = Fab 3                                                                                                       |

|     |             | 001 = Fab 4                                                                                                       |

|     |             | 100 = Fab 3 modified for the sB1 processor                                                                        |

|     |             | 101 = Fab 4 modified for the sB1 processor                                                                        |

|     |             | Bits 5:3 are valid as BRDREV when bit 7 = "1".                                                                    |

|     |             | All previous processor module revisions are not compatible with Fab 3 which is why the numbering starts with 000. |

| 6:5 | Reserved    |                                                                                                                   |

| 7   | BRDREVSEL   | When "1", bits 5:3 indicate the board revision, bit 6 is reserved                                                 |

|     |             | When "0", bit 6:3 are reserved.                                                                                   |

Table 1.8 1GB Memory Module I<sup>2</sup>C Bit Map

| Bit | Bit Name | Description                                    |

|-----|----------|------------------------------------------------|

| 1:0 |          | Board Revision ID                              |

|     |          | 00 = 1GB Module (Fab1 or Fab2)                 |

|     |          | 01 = 1GB Module (Fab3)                         |

|     |          | 10 = 4GB Module                                |

|     |          | 11 = Reserved                                  |

| 3:2 |          | Bank 0 SIMM Speed                              |

|     |          | 00 = 50ns (bank 0)                             |

|     |          | 01 = 80ns (bank 0)                             |

|     |          | 10 = 70ns (bank 0)                             |

|     |          | 11 = 60ns (bank 0)                             |

| 5:4 |          | Bank 1 SIMM Speed                              |

|     |          | 00 = 50ns (bank 1)                             |

|     |          | 01 = 80ns (bank 1)                             |

|     |          | 10 = 70ns (bank 1)                             |

|     |          | 11 = 60ns (bank 1)                             |

| 6   |          | Reserved                                       |

| 7   |          | RAS/CAS Multiplexing for Address Bit permuting |

|     |          | 0 = Enabled                                    |

|     |          | 1 = Disabled                                   |

Table 1.9 4GB Memory Module I<sup>2</sup>C Bit Map

| Bit | Bit Name     | Description                         |

|-----|--------------|-------------------------------------|

| 1:0 | BRDREV(1:0)  | Board Revision ID                   |

|     |              | 00 = 1GB Module (Fab1 or Fab2)      |

|     |              | 01 = 1GB Module (Fab3)              |

|     |              | 10 = 4GB Module                     |

|     |              | 11 = Reserved                       |

| 5:2 | REFRESH(3:0) | Refresh                             |

|     |              | 1110 = 8Mx8/9 DRAM based 4K refresh |

|     |              | 1111 = 16Mx4 DRAM based 8K refresh  |

|     |              | All others are reserved.            |

| 7:6 | DIMMSPD(1:0) | DIMM Speed (All Banks)              |

|     |              | 00 = 50ns                           |

|     |              | 01 = 80ns                           |

|     |              | 10 = 70ns                           |

|     |              | 11 = 60ns                           |

Table 1.10 Termination Module I<sup>2</sup>C Bit Map

| Bit | Bit Name    | Description                                                                                                                                                                                                                                      |

|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2:0 | BRDREV(2:0) | AP450GX Terminator Module revision ID                                                                                                                                                                                                            |

|     |             | 000 = Fab 3                                                                                                                                                                                                                                      |

|     |             | All previous terminator module revisions are not compatible with Fab 3 which is why the numbering starts with 000.                                                                                                                               |

| 6:3 | N/C         | These signals are not used.                                                                                                                                                                                                                      |

| 7   | GROUND      | Hard wired to ground.                                                                                                                                                                                                                            |

|     |             | To differentiate between a terminator module and a processor module, write a one "1" to bit 7 then do a read of bit 7. If a one "1" is read back, the board is a processor module. If a zero "0" is read back, the board is a terminator module. |

#### 1.18.2 Server Management Connector

A 26-pin connector is provided to interface with an emergency management adapter card. It is designed for Intel's Server Monitor Module which allows the user to manage (monitor and control) the server from a remote console, but could be used by other similar implementations. The connector provides access to the I<sup>2</sup>C bus, power on/off signals, power good from the power supply and a host of other signals. Refer to the connector pin-out in Appendix C for a list of all signals.

# 1.18.3 System Fan Interface

There are four fan connectors on the system baseboard. The connector pin-out is listed in Appendix C. These connectors provide a ground, 12V power to the fan and a fan-fail input from the fan. The system will be able to detect the failure and will report it via Intel's LANDesk® Server Control Software. These fan failures are also logged in the BIOS event log, and are denoted by the fan fail light on the system front panel. All four fan-fail inputs are tied to A/D channel 8 for monitoring by the INCA component. The current LANDesk software does have the ability to distinguish between the four fans. It simply knows if one fan has failed. If one or more of the fan connectors is not used in a particular application, pins 1 (GND) and 3 (Fan Fail) on the connector must be connected together. This connection is required to prevent an erroneous failed fan indication.

#### 1.18.4 Hard Drive LED Interface

There are two Hard Drive LED interface connectors on the baseboard (locking polarized, 4 position, single in-line, .025 in square pin). See Appendix C for the pinout. Pin 2 of both connectors is tied together as well as to the IDE connector (pin 39), the SCSI A LED signal and the front panel signal HD1\_LED\_ACT# (pin 10). They are tied together so that any of these sources can activate a light on the front panel to indicate hard drive access.

Likewise pin 3 of both connectors is tied together as well as to the SCSI B LED signal and the front panel signal HD2\_LED\_ACT# (pin 11).

The purpose of the connectors themselves is to provide a way for a front panel LED to be driven from an add-in disk controller. Note Intel's AP450GX MP Server chassis does provide LED's on its front panel that can be driven by either of these signals.

# 1.19 Control Signals

## 1.19.1 Remote Sensing

Remote sensing exists on the +5.1 Vdc, +12 Vdc, and +3.3 Vdc outputs. The -12 Vdc, -5 Vdc, and +5 V standby outputs are referenced to the negative (-) remote sense point. Only voltage drops exterior to the power supply are included. The loss of a remote sense connection will not cause the power supply to go into a high output voltage condition. Intel strongly recommends using the signals for remote sense. Without remote sense capabilities, it will be difficult to keep the power rails within the board set specifications.

**Table 1.11 Amount of Drop to Regulate**

| Output voltage | Maximum voltage drop |

|----------------|----------------------|

| +5.1 Vdc       | 0.3V                 |

| +12 Vdc        | 0.2V                 |

| +3.3 Vdc       | 0.2V                 |

| Ground         | 0.2V                 |

#### 1.19.2 Power Good (PGOOD & PWRGOOD) signals

Each power supply provides a power good signal to the power distribution backplane. This signal indicates that all outputs have reached operating state. The PGOOD signal is deasserted for a minimum of 250uS before any of the output voltages fall below the regulation limit. During normal power on, PGOOD will be asserted between 100mS and 1500mS after the 5.1V output reaches a minimum of 4.75V.

To indicate that all power supplies are within regulation, the PGOOD signals from each supply are OR'd together on the power distribution backplane to create a single PWRGOOD signal which is passed on to the baseboard. The PWRGOOD signal has the same timing parameters as the individual PGOOD signals described above.

# 1.20 Baseboard Jumper Settings

Table 1.12 Jumper Configuration, Baseboard

| Baseboard configuration jumper summary (listed by |      |                                                                                                                                                                                                |

|---------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| block number on board)                            | Pins | Description                                                                                                                                                                                    |

| J6A1, BIOS Recovery                               | 1-2* | Normal BIOS boot block                                                                                                                                                                         |

|                                                   | 2-3  | Recovery BIOS boot block                                                                                                                                                                       |

|                                                   |      | If the normal BIOS gets corrupted, and you are unable to reload a new BIOS from floppy disk, install the jumper into recovery mode which will allow the system to boot from the recovery BIOS. |

| J6A1, Boot Block Protect                          | 1-2* | BIOS boot block is write-protected                                                                                                                                                             |

|                                                   | 2-3  | BIOS boot block is programmable                                                                                                                                                                |

|                                                   |      | The programmable mode should only be enabled under carefully controlled circumstances. Incorrect programming of the boot block will render the system unbootable.                              |

| J6A4, BIOS write                                  | 1-2  | Disables BIOS update of flash memory                                                                                                                                                           |

|                                                   | 2-3* | Enables BIOS update of flash memory with special utility                                                                                                                                       |

|                                                   |      | Install the jumper in the enable mode when updating the system BIOS. This jumper should always be set to enable. Some operating systems will not boot without this jumper enabled.             |

| J6A4, Floppy 0                                    | 1-2  | For 1.44 MB diskette drive size or autodetection. Disables 2.88 MB size detection                                                                                                              |

|                                                   | 2-3* | For forced 2.88 MB diskette drive size                                                                                                                                                         |

| J6A2, Floppy 1                                    | 1-2  | For 1.44 MB diskette drive size or autodetection. Disables 2.88 MB size detection                                                                                                              |