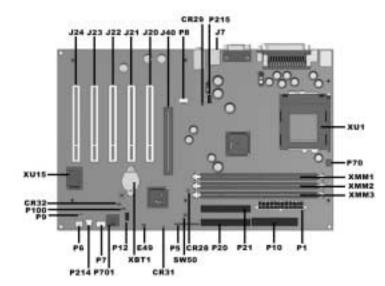

### **Connectors and Jumpers**

| CR28           | 3.3V Aux LED                                                   |  |

|----------------|----------------------------------------------------------------|--|

| CR29           | 3.3V Main LED (NI)                                             |  |

| CR31           | Power Button LED (ON when pushed)                              |  |

| CR32           | 5V Aux (ON)/PS_ON_LED (OFF)                                    |  |

| E49            | Clear Password Header (Installed = Enabled, Removed = Cleared) |  |

| SW50           | Clear CMOS                                                     |  |

| P1             | Power Supply Connector                                         |  |

| P5(pins 1-9)   | Power Button, Pwr LED and HD<br>LED Connector                  |  |

| P5(pins 10-11) | SCSI LED Connector                                             |  |

| P6             | Speaker Connector                                              |  |

| P7             | CD-ROM Audio                                                   |  |

| P701           | CD-ROM Audio                                                   |  |

| P8             | Chassis Fan Connector                                          |  |

| P12    | SOS Connector                |  |

|--------|------------------------------|--|

| P214   | Hood Intrusion Sensor        |  |

| P215   | Hood Lock Solenoid Connector |  |

| P10    | Diskette Drive Connector     |  |

| P20    | Primary IDE Connector        |  |

| P21    | Secondary IDE Connector      |  |

| P70    | CPU Fan                      |  |

| P100   | ITP Connector                |  |

| J20-24 | PCI Slots                    |  |

| J40    | AGP/AIMM Connector           |  |

| XBT1   | External Battery             |  |

| XMM1-3 | DIMM Memory Slots            |  |

| XU1    | Primary Processor Socket     |  |

### **System Hardware Interrupts**

| IRQ | System Function              |  |

|-----|------------------------------|--|

| 0   | Timer Interrupt              |  |

| 1   | Keyboard                     |  |

| 2   | Interrupt Controller Cascade |  |

| 3   | Serial Port (COM B)          |  |

| 4   | Serial Port (COM A)          |  |

| 5   | Available for PCI            |  |

| 6   | Diskette Drive               |  |

| 7   | Parallel Port (LPT 1)        |  |

| IRQ | System Function          |

|-----|--------------------------|

| 8   | Real-Time Clock          |

| 9   | Available for PCI        |

| 10  | Available for PCI        |

| 11  | Available for PCI        |

| 12  | Mouse                    |

| 13  | Coprocessor              |

| 14  | Primary IDE Controller   |

| 15  | Secondary IDE Controller |

# System Hardware DMA

| DMA | System Function                                     | DMA | System Function          |

|-----|-----------------------------------------------------|-----|--------------------------|

| 0   | Unused                                              | 4   | DMA Controller Cascading |

| 1   | Unused                                              | 5   | Unused                   |

| 2   | Diskette Drive                                      | 6   | Unused                   |

| 3   | ECP Parallel Port LPT1 (Default; Alternate = DMA 0) | 7   | Unused                   |

## ICH Fixed I/O Registers

| ICH Fixed I/O Registers                                          |                                                                                                                                                                       |  |

|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Port                                                             | Register Name                                                                                                                                                         |  |

| 00h, 02h, 04h, 06h                                               | Channel 0, 1, 2, 3 DMA Base & Current Address Regsiter                                                                                                                |  |

| C0h, C4h, C8h, CCh                                               | Channel 4, 5, 6, 7 DMA Base & Current Address Register                                                                                                                |  |

| 01h, 03h, 05h, 07h                                               | Channel 0, 1, 2, 3 DMA Base & Current Count Register                                                                                                                  |  |

| C2h, C6h, Cah, CEh                                               | Channel 4, 5, 6, 7 DMA Base & Current Count Register                                                                                                                  |  |

| 10h-1Fh                                                          | Aliased at 00h-0Fh                                                                                                                                                    |  |

| 20h                                                              | Master PIC ICW1 Init. Cmd Word 1 Register<br>Master PIC OCW2 Op Ctrl Word 2 Register<br>Master PIC OCW3 Op Ctrl Word 3 Register                                       |  |

| 21h                                                              | Master PIC ICW2 Init. Cmd Word 1 Register Master PIC ICW3 Init. Cmd Word 1 Register Master PIC ICW4 Init. Cmd Word 1 Register Master PIC OCW1 Op Ctrl Word 3 Register |  |

| 24h-25h, 28-29h, 2Ch-2Dh, 30h-<br>31h, 34h-35h, 38h-39h, 3Ch-3Dh | Aliased at 20h-21h                                                                                                                                                    |  |

| 40h                                                              | Counter 0 Interval Time Status Byte Format<br>Counter 0 Counter Access Port Register                                                                                  |  |

| 41h                                                              | Counter 1 Interval Time Status Byte Format<br>Counter 1 Counter Access Port Register                                                                                  |  |

| 42h                                                              | Counter 2 Interval Time Status Byte Format<br>Counter 2 Counter Access Port Register                                                                                  |  |

| 43h                                                              | Timer Control Word Register<br>Timer Control Word Register Read Back<br>Counter Latch Command                                                                         |  |

| 50h-53h                                                          | Aliased at 40h-43h                                                                                                                                                    |  |

| 61h                                                              | NMI Status and Control Register                                                                                                                                       |  |

| 70h                                                              | NMI Enable Register<br>Real-Time Clock (Standard RAM) Index Register                                                                                                  |  |

| 71h                                                              | Real-Time Clock (Standard RAM) Target Register                                                                                                                        |  |

| 72h                                                              | Extended RAM Index Register                                                                                                                                           |  |

| 73h                                                              | Extended RAM Target Register                                                                                                                                          |  |

| 74h-75h                                                          | Aliased at 70h-71h                                                                                                                                                    |  |

| 76h-77h                                                          | Aliased at 72h-73h or 70h-71h                                                                                                                                         |  |

| 80h, 84h-86h, 88h                                                | Reserved Page Registers                                                                                                                                               |  |

| 81h, 82h, 83h                                                    | Channel 2, 3, 1 DMA Memory Low Page Register                                                                                                                          |  |

| 89h, 8Ah, 8Bh                                                    | Channel 6, 7, 5 DMA Memory Low Page Register                                                                                                                          |  |

| 8CH-8Eh                                                          | Reserved Page Registers                                                                                                                                               |  |

| 8Fh                                                              | Refresh Low Page Register                                                                                                                                             |  |

| 91h-9Fh (except 92h)                                             | Aliased at 81h-8Fh                                                                                                                                                    |  |

| 92h                                                              | Fast A20 and INIT Register                                                                                                                                            |  |

|                                                                  |                                                                                                                                                                       |  |

| ICH Fixed I/O Registers (Continued)                                 |                                                                                                                                                                            |  |

|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Port                                                                | Register Name                                                                                                                                                              |  |

| A0h                                                                 | Slave PIC ICW1 Init. Cmd Word 1 Register<br>Slave PIC OCW2 Op Ctrl Word 2 Register<br>Slave PIC OCW3 Op Ctrl Word 3 Register                                               |  |

| Al                                                                  | Slave PIC ICW2 Init. Cmd Word 2 Register<br>Slave PIC ICW3 Init. Cmd Word 3 Register<br>Slave PIC ICW4 Init. Cmd Word 4 Register<br>Slave PIC OCW1 Op Ctrl Word 1 Register |  |

| A4h-A5h, A8h-A8h, ACh-ADh,<br>B0h-B1h, B4h-B5h, B8h-B9h,<br>BCh-BDh | Aliased at A0h-A1h                                                                                                                                                         |  |

| B2h                                                                 | Advanced Power Management Control Port Register                                                                                                                            |  |

| B3h                                                                 | Advanced Power Management Status Port Register                                                                                                                             |  |

| C0h, C4h, C8h, CCh                                                  | Channel 4, 5, 6, 7 DMA Base and Current Address Register                                                                                                                   |  |

| C1h                                                                 | Aliased at C0h                                                                                                                                                             |  |

| C5h                                                                 | Aliased at C4h                                                                                                                                                             |  |

| C9h                                                                 | Aliased at C8h                                                                                                                                                             |  |

| CDh                                                                 | Aliased at CCh                                                                                                                                                             |  |

| C2h, C6h, CAh, CEh                                                  | Channel 4, 5, 6, 7 DMA Base and Current Count Register                                                                                                                     |  |

| C3h                                                                 | Aliased at C2h                                                                                                                                                             |  |

| C7h                                                                 | Aliased at C6h                                                                                                                                                             |  |

| CBh                                                                 | Aliased at CAh                                                                                                                                                             |  |

| CFh                                                                 | Aliased at Ceh                                                                                                                                                             |  |

| D0h                                                                 | Channel 4-7 DMA Command Register<br>Channel 4-7 DMA Status Register                                                                                                        |  |

| D1h                                                                 | Aliased at D0h                                                                                                                                                             |  |

| D4h                                                                 | Channel 4-7 DMA Write Single Mask Register                                                                                                                                 |  |

| D5h                                                                 | Aliased at D4h                                                                                                                                                             |  |

| D6h                                                                 | Channel 4-7 DMA Channel Mode Register                                                                                                                                      |  |

| D7h                                                                 | Aliased at D6h                                                                                                                                                             |  |

| D8h                                                                 | Channel 4-7 DMA Clear Byte Pointer Register                                                                                                                                |  |

| D9h                                                                 | Aliased at D8h                                                                                                                                                             |  |

| DAh                                                                 | Channel 4-7 DMA Master Clear Register                                                                                                                                      |  |

| DBh                                                                 | Aliased at DAh                                                                                                                                                             |  |

| DCh                                                                 | Channel 4-7 DMA Clear Mask Register                                                                                                                                        |  |

| DEh                                                                 | Aliased at DCh                                                                                                                                                             |  |

| DEh                                                                 | Channel 4-7 DMA Write All Mask Register                                                                                                                                    |  |

| DFh                                                                 | Aliased at DEh                                                                                                                                                             |  |

| F0h                                                                 | Coprocessor Error Register                                                                                                                                                 |  |

| 170h-177h                                                           | PIO Mode Command Block Offset for Secondary Drive                                                                                                                          |  |

| 1F0h-1F7h                                                           | PIO Mode Command Block Offset for Primary Drive                                                                                                                            |  |

| 376h                                                                | PIO Mode Control Block Offset for Secondary Drive                                                                                                                          |  |

| 3F6h                                                                | PIO Mode Control Block Offset for Primary Drive                                                                                                                            |  |

| 4D0h                                                                | Master PIC Edge/Level Triggered Register                                                                                                                                   |  |

| 3F6h                                                                | PIO Mode Control Block Offset for Primary Drive                                                                                                                            |  |

| 4D0h                                                                | Master PIC Edge/Level Triggered Register                                                                                                                                   |  |

| 4D1h                                                                | Slave PIC Edge/Level Triggered Register                                                                                                                                    |  |

| 400-47F                                                             | Super I/O                                                                                                                                                                  |  |

| CF9h                                                                | Reset Control Register                                                                                                                                                     |  |

| F800-F87F                                                           | Reserved (power management)                                                                                                                                                |  |

| FA00-FA3F                                                           | Reserved (GPIO management)                                                                                                                                                 |  |

| FC00-FC0F                                                           | Reserved (SMBUS controller)                                                                                                                                                |  |

$Note: When the \ POS\_DEC\_EN \ bit \ is \ set, \ additional \ I/O \ ports \ get \ positively \ decoded \ by \ the \ ICH$

## System Memory Map

| Size    | Memory Address         | System Function              |

|---------|------------------------|------------------------------|

| 512 KB  | FFFFFFFh to FFF80000   | System ROM                   |

| 2030 MB | FEDFFFFFh to 80000000h | PCI Memory Expansion         |

| 2047 MB | 7FFFFFFh to 00100000h  | HOST or PCI Memory Expansion |

| 128KB   | 000FFFFFh to 000E0000h | System ROM                   |

| 128 KB  | 000DFFFFh to 000C0000h | PCI Option ROMs              |

| 128 KB  | 000BFFFFh to 000A0000h | Video RAM                    |

| 640 KB  | 0009FFFFh to 00000000h | Base Memory                  |

# Clearing CMOS

The computer's configuration (CMOS) may occasionally be corrupted. If it does, it is necessary to clear the CMOS memory using jumper SW50

To clear and reset the configuration, perform the following procedure:

1. Prepare the computer for disassembly.

CAUTION: The power cord must be disconnected from the power source before pushing the Clear CMOS Button (NOTE: All LEDs on the board should be OFF). Failure to do so may damage the system board

- 2. Remove the access panel (Section 4.6).

- 3. Press the CMOS button located on the system board and keep it depressed for 5 seconds.

- Replace the access panel.

- Turn the computer on.

- $6. \quad Run\,F10\,Computer\,Setup\ (delete-utility)\ to\ reconfigure\ the\ system.$

## Disabling or Clearing the Power-On and Setup Passwords

- Turn off the computer and any external devices, and disconnect the power cord from the power outlet.

- 3. Locate the header and jumper labeled E49.

- 4. Remove the jumper from pins 1 and 2. Place the jumper over pin 2 only, in order to avoid losing it.

- 6. Plug in the computer and turn on power to all equipment. Allow the operating system to start. This clears the current passwords and disables the password features.

- 7. To re-enable the password features, repeat steps 1-3, then replace the jumper on pins 1 and 2.

- 8. Repeat steps 5-6, then establish new passwords.

Refer to the Computer Setup (F10 Setup) instructions to establish new passwords.