# Dual-Core Intel<sup>®</sup> Xeon<sup>®</sup> processor LV and ULV

**Thermal Design Guide**

August 2006

Reference Number: 311374-002

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families. See <a href="http://www.intel.com/products/processor\_number">http://www.intel.com/products/processor\_number</a> for details.

The Dual-Core Intel<sup>®</sup> Xeon<sup>®</sup> processor LV and ULV may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Hyper-Threading Technology requires a computer system with an Intel<sup>®</sup> Pentium<sup>®</sup> 4 processor supporting HT Technology and a HT Technology enabled chipset, BIOS and operating system. Performance will vary depending on the specific hardware and software you use. See http://www.intel.com/products/ht/Hyperthreading\_more.htm for additional information.

This Thermal Design Guide as well as the software described in it is furnished under license and may only be used or copied in accordance with the terms of the license. The information in this manual is furnished for informational use only, is subject to change without notice, and should not be construed as a commitment by Intel Corporation. Intel Corporation assumes no responsibility or liability for any errors or inaccuracies that may appear in this document or any software that may be provided in association with this document.

Except as permitted by such license, no part of this document may be reproduced, stored in a retrieval system, or transmitted in any form or by any means without the express written consent of Intel Corporation.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

BunnyPeople, Celeron, Celeron Inside, Centrino, Centrino logo, Core Inside, Dialogic, FlashFile, i960, InstantIP, Intel, Intel logo, Intel386, Intel486, Intel740, IntelDX2, IntelDX2, IntelSX2, Intel Core, Intel Inside, Intel Inside logo, Intel. Leap ahead., Intel. Leap ahead. logo, Intel NetBurst, Intel NetBurst, Intel NetBurst, Intel Structure, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel Viiv, Intel vPro, Intel XScale, IPLink, Itanium, Itanium Inside, MCS, MMX, Oplus, OverDrive, PDCharm, Pentium, Pentium Inside, skoool, Sound Mark, The Journey Inside, VTune, Xeon, and Xeon Inside are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2006, Intel Corporation. All Rights Reserved.

# Contents

| 1.0 | Intro<br>1.1<br>1.2<br>1.3<br>1.4        | duction<br>Design Flow<br>Definition of Terms<br>Reference Documents<br>Thermal Model Availability                                                                                                                                                                                               | . 6<br>. 7<br>. 8                            |

|-----|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 2.0 | Packa                                    | age Information                                                                                                                                                                                                                                                                                  | . 9                                          |

| 3.0 | <b>Therr</b><br>3.1<br>3.2               | mal Specifications<br>Thermal Design Power<br>Maximum Allowed Component Temperature                                                                                                                                                                                                              | 16                                           |

| 4.0 | Mech<br>4.1<br>4.2<br>4.3                | anical Specifications<br>Package Mechanical Requirements<br>Package Keep-Out Zones Requirements<br>Board Level Keep-Out Zone Requirements                                                                                                                                                        | 17<br>17                                     |

| 5.0 | <b>Therr</b><br>5.1                      | mal Solution Requirements       2         Characterizing the Thermal Solution Requirement       2                                                                                                                                                                                                |                                              |

| 6.0 | <b>Refer</b><br>6.1<br>6.2<br>6.3<br>6.4 | Pence Thermal SolutionsAdvancedTCA* Reference Heatsink6.1.1 Mechanical Design6.1.2 Keep-Out Zone Requirements6.1.3 Thermal Performance1U+ Reference Heatsink6.2.1 Mechanical Design6.2.2 Keep-Out Zone Requirements6.2.3 Thermal PerformanceThermal Interface Material (TIM)Heatsink Orientation | 23<br>24<br>24<br>25<br>25<br>26<br>26<br>27 |

| 7.0 | <b>Therr</b><br>7.1<br>7.2<br>7.3<br>7.4 | mal Metrology                                                                                                                                                                                                                                                                                    | 29<br>29<br>29                               |

| 8.0 | Relia                                    | bility Guidelines                                                                                                                                                                                                                                                                                | 30                                           |

| Α   | <b>Therr</b><br>A.1<br>A.2               | mal Modeling Tools.<br>Recommended Thermal Modeling Method<br>Example Estimating $\Psi$ <sub>JA</sub> Using Thermal Models                                                                                                                                                                       | 31                                           |

| В   | <b>Therr</b><br>Suppl<br>B.1             | nal Solution Component<br>liers<br>Reference Heatsink                                                                                                                                                                                                                                            |                                              |

| С   | Mech                                     | anical Drawings                                                                                                                                                                                                                                                                                  | 36                                           |

# **Figures**

| 1 | Thermal Design Process                             | 7  |

|---|----------------------------------------------------|----|

| 2 | Package Dimensions (3D View)                       | 9  |

|   | Package Dimensions (Top and Side View: One of Two) |    |

| 4 | Package Dimensions (Bottom View: One of Two)       | 11 |

| 5  | Package Dimensions (Front View)12                                                  |

|----|------------------------------------------------------------------------------------|

| 6  | Dimension Information for Package                                                  |

| 7  | Package Dimensions (Top and Side View: Two of Two)14                               |

| 8  | Package Dimensions (Bottom View: Two of Two)15                                     |

| 9  | Board Level Primary Side Keep-Out Zone Requirements                                |

| 10 | Board Level Secondary Side Keep-Out Zone Requirements19                            |

| 11 | Processor Thermal Characterization Parameter Relationships                         |

| 12 | AdvancedTCA* Reference Heatsink Assembly24                                         |

| 13 | AdvancedTCA* Reference Heatsink Thermal Performance vs. Volumetric Airflow Rate25  |

| 14 | 1U Reference Heatsink Assembly                                                     |

| 15 | 1U Reference Heatsink Thermal Performance versus Volumetric Airflow Rate27         |

| 16 | Thermal Modeling Method Flow Chart31                                               |

| 17 | Example of Thermal Modeling Results Showing the Temperature of the Heatsink Base33 |

| 18 | AdvancedTCA* Reference Heatsink PCB Keep-Out Zone Requirements: One of Two37       |

| 19 | AdvancedTCA* Reference Heatsink PCB Keep-Out Zone Requirements: Two of Two38       |

| 20 | AdvancedTCA* Reference Heatsink Assembly Drawing                                   |

| 21 | AdvancedTCA* Reference Heatsink Drawing40                                          |

| 22 | 1U Reference Heatsink PCB Keep-Out Zone Requirements: One of Two41                 |

| 23 | 1U Reference Heatsink PCB Keep-Out Zone Requirements: Two of Two42                 |

| 24 | 1U Reference Heatsink Assembly Drawing43                                           |

| 25 | 1U Reference Heatsink Drawing44                                                    |

# Tables

| 1 | Definition of Terms                                                         | 7  |

|---|-----------------------------------------------------------------------------|----|

| 2 | Thermal Design Power (TDP) Specifications                                   | 16 |

| 3 | Required Heatsink Thermal Performance ( $\Psi_{JA}$ )                       | 22 |

|   | Reliability Requirements                                                    |    |

|   | Recommended $\Psi_{IS}$ Values for the Reference Thermal Interface Material |    |

| 6 | Reference Heatsink                                                          | 35 |

| 7 | Mechanical Drawing List                                                     | 36 |

# **Revision History**

| Date        | Revision | Description                                                                         |

|-------------|----------|-------------------------------------------------------------------------------------|

| March 2006  | 001      | Initial public release                                                              |

| August 2006 | 002      | Added support for the Dual-Core Intel <sup>®</sup> Xeon <sup>®</sup> Processor ULV. |

# 1.0 Introduction

The power dissipation of electronic components has risen along with the increase in complexity of computer systems. To ensure quality, reliability, and performance goals are met over the product's life cycle, the heat generated by the device must be properly dissipated. Typical methods to improve heat dissipation include selective use of airflow ducting and/or the use of heatsinks.

The goals of this document are to:

- Explain the thermal and mechanical specification for the Dual-Core Intel<sup>®</sup> Xeon<sup>®</sup> processor LV and ULV.

- Describe a reference thermal solution that meets the specifications.

A properly designed thermal solution adequately cools the device die temperature at or below the thermal specification. This is accomplished by providing a suitable localambient temperature, ensuring adequate local airflow, and minimizing the die to localambient thermal resistance. Operation outside the functional limits can degrade system performance and may cause permanent changes in the operating characteristics of the component.

This document describes thermal design guidelines for the processor in the micro Flip Chip-Pin Grid Array (micro FCPGA) package. Detailed mechanical and thermal specifications for these processors can be found in the *Dual-Core Intel<sup>®</sup> Xeon<sup>®</sup>* processor LV and ULV Datasheet.

The information provided in this document is for reference only and additional validation must be performed prior to implementing the designs into final production. The intent of this document is to assist each original equipment manufacturer (OEM) with the development of thermal solutions for their individual designs. The final heatsink solution, including the heatsink, attachment method, and thermal interface material (TIM) must comply with the mechanical design, environmental, and reliability requirements delineated in the processor datasheet. It is the responsibility of each OEM to validate the thermal solution design with their specific applications.

This document addresses thermal and mechanical design specifications for the Dual-Core Intel<sup>®</sup> Xeon<sup>®</sup> processor LV and ULV only. For thermal design information on other Intel<sup>®</sup> components, refer to the respective component datasheet.

*Note:* Unless otherwise specified, the term "processor" refers to the Dual-Core Intel<sup>®</sup> Xeon<sup>®</sup> processor LV and ULV.

## 1.1 Design Flow

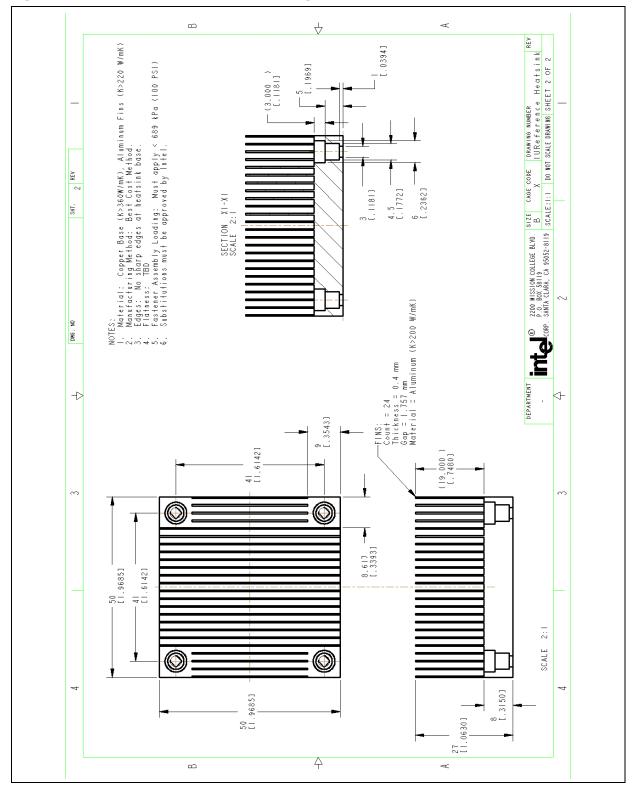

Several tools are available from Intel Corporation to assist in the development of a reliable, cost-effective thermal solution. Figure 1 illustrates a typical thermal solution design process with available tools noted. The tools are available through your local Intel Corporation field sales representative.

#### Figure 1. Thermal Design Process

# 1.2 Definition of Terms

#### Table 1.Definition of Terms

| Term                      | Definition                                                                                                                                                                                                                                                                                                   |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CFM                       | Volumetric airflow rate in cubic feet per minute.                                                                                                                                                                                                                                                            |

| DP                        | Dual processing capability.                                                                                                                                                                                                                                                                                  |

| FCPGA                     | Flip-Chip Pin Grid Array. A pin grid array packaging technology where the die is exposed on the package substrate.                                                                                                                                                                                           |

| LFM                       | Airflow velocity in linear feet per minute.                                                                                                                                                                                                                                                                  |

| LV                        | Low Voltage                                                                                                                                                                                                                                                                                                  |

| PCB                       | Printed Circuit Board                                                                                                                                                                                                                                                                                        |

| T <sub>JUNCTION MAX</sub> | Maximum allowed component temperature. Also referred to as T <sub>J-MAX</sub> .                                                                                                                                                                                                                              |

| TDP                       | Thermal Design Power. TDP is Intel's specification for the amount of power that a thermal solution should be designed to dissipate. TDP is based on running worst-case real world applications and benchmarks. TDP is not maximum theoretical power.                                                         |

| TIM                       | Thermal Interface Material. The thermally conductive compound between the heatsink and processor case. This material fills air gaps and voids, and enhances spreading of the heat from the case to the heatsink.                                                                                             |

| T <sub>LA</sub>           | Local ambient temperature. This is the temperature measured inside the chassis, approximately 1" upstream of a component heatsink. Also referred to as $T_{\rm A}$                                                                                                                                           |

| T <sub>SINK</sub>         | Heatsink temperature. This is the temperature measured at the geometric center on the underside of the heatsink base. Also referred to as ${\rm T}_{\rm S}$                                                                                                                                                  |

| $\Psi_{JA}$               | Junction-to-ambient thermal characterization parameter. A measure of heatsink thermal performance using the thermal design power. Defined as $(T_{JUNCTION} - T_{LA})$ / Total Package Power. Note: The heat source size should be specified for $\Psi$ calculations.                                        |

| $\Psi_{SA}$               | Sink-to-ambient thermal characterization parameter. A measure of heatsink thermal performance using the thermal design power. Defined as $(T_{SINK} - T_{LA})$ / Total Package Power.<br>Note: The heat source size should be specified for $\Psi$ calculations.                                             |

| $\Psi_{TIM}$              | Thermal interface material thermal characterization parameter. A measure of heatsink thermal performance using the thermal design power. Defined as $(T_{JUNCTION} - T_{SINK})$ / Total Package Power. Note: The heat source size must be specified for $\Psi$ calculations. Also referred to as $\Psi_{JS}$ |

| ULV                       | Ultra Low Voltage                                                                                                                                                                                                                                                                                            |

# 1.3 Reference Documents

The reader of this specification should also be familiar with material and concepts presented in the following documents:

- Intel<sup>®</sup> Mobile Processor Micro-FCPGA Socket (mPGA479M) Design Guidelines

- Dual-Core  $\mathsf{Intel}^{\mathbb{R}}$  Xeon  $^{\mathbb{R}}$  processor LV and ULV Datasheet

*Note:* Unless otherwise noted, these documents are available through your Intel field sales representative.

# 1.4 Thermal Model Availability

Intel provides thermal simulation models of the device and a thermal model user's guide to aid designers in simulating, analyzing, and optimizing thermal solutions in an integrated, system-level environment. The models are for use with commercially available Computational Fluid Dynamics (CFD)-based thermal analysis tools including Flotherm\* (version 3.1 or higher) by Flomerics, Inc. or Icepak\* by Fluent, Inc. Contact your Intel representative to order the thermal models and associated user's guides.

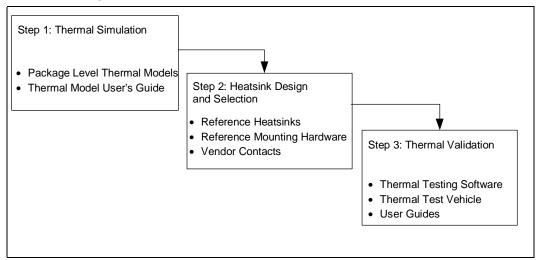

# 2.0 Package Information

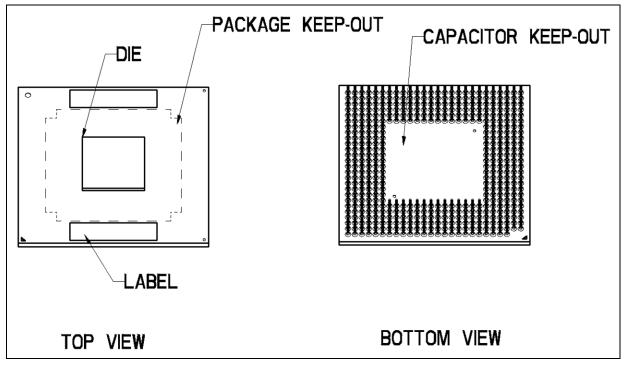

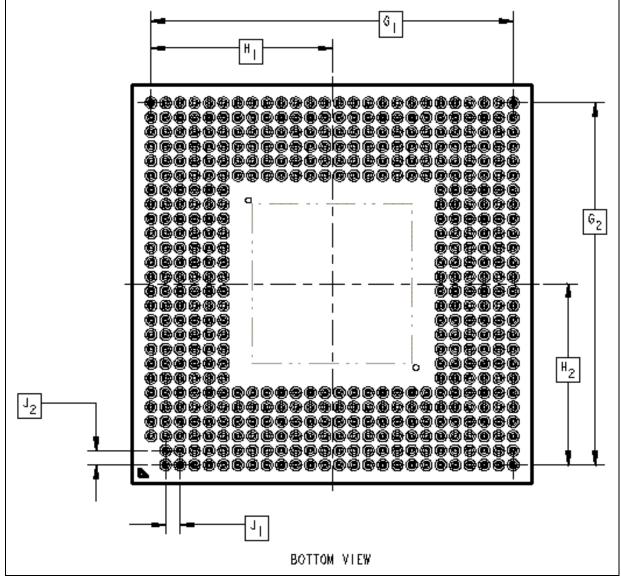

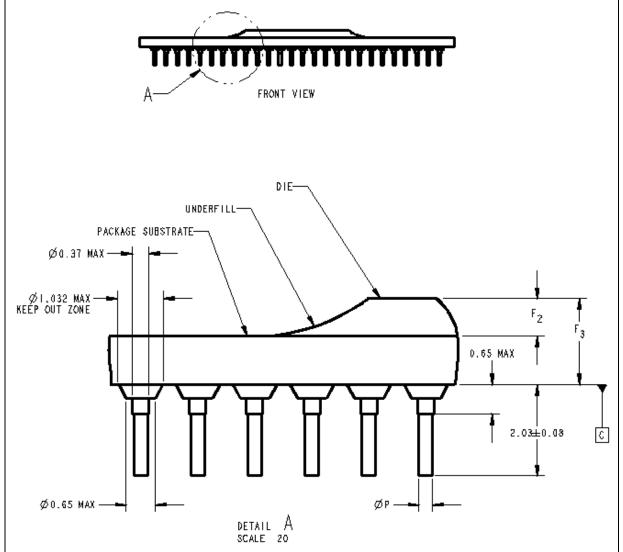

The component utilizes a 35 mm x 35 mm, micro FCPGA package (see Figure 2 through Figure 8). The data is provided for reference only. Refer to the device's most recent datasheet for up-to-date data. In the event of conflict, the device's datasheet supersedes data shown.

The processor connects to the baseboard through a 479-pin surface mount, zero insertion force (ZIF) socket. A description of the socket can be found in the *Intel<sup>®</sup> Mobile Processor Micro-FCPGA Socket (mPGA479M) Design Guidelines.*

The processor package has mechanical load limits that are specified in the processor datasheet. These load limits should not be exceeded during heatsink installation, removal, mechanical stress testing, or standard shipping conditions. The heatsink mass can also add additional dynamic compressive load to the package during a mechanical shock event. Amplification factors due to the impact force during shock must be taken into account in dynamic load calculations. The total combination of dynamic and static compressive load should not then exceed the processor datasheet compressive dynamic load specification during a vertical shock. It is not recommended to use any portion of the processor substrate as a mechanical reference or load bearing surface in either static or dynamic compressive load conditions.

#### Figure 3. Package Dimensions (Top and Side View: One of Two)

Notes:

Dimensions are in millimeters [inches]. Refer to Figure 6 for details. 1. 2.

#### Figure 4. Package Dimensions (Bottom View: One of Two)

Notes:

1. Dimensions are in millimeters [inches].

2. Refer to Figure 6 for details.

#### Notes:

Dimensions are in millimeters [inches]. Refer to Figure 6 for details. 1. 2.

E

| SYMBOL         | MILLIMETERS<br>[INCHES] |         | COMMENTS |

|----------------|-------------------------|---------|----------|

|                | MIN                     | MAX     |          |

| ۱ <sup>в</sup> | 34.95                   | 35.05   |          |

| B <sub>2</sub> | 34.95                   | 35.05   |          |

| c١             | 11                      | . I     |          |

| ¢2             | 8                       | . 2     |          |

| F <sub>2</sub> | 0.                      | 89      |          |

| ۶ <sub>3</sub> | 1.993                   | 2.273   |          |

| <sup>6</sup>   | 31.75                   | BASIC   |          |

| 6 <sub>2</sub> | 31.75                   | BASIC   |          |

| н <sub>I</sub> | 15.875                  | 5 BASIC |          |

| H <sub>2</sub> | 15.875                  | 5 BASIC |          |

| ٦              | 1.27                    | BASIC   |          |

| J <sub>2</sub> | 1.27                    | BASIC   |          |

| Р              | 0.255                   | 0.355   |          |

| P DIE          | 689                     | kPa     |          |

| W              | 6                       | g       |          |

|                | Keying Pins             |         | AI, BI   |

# Figure 6. Dimension Information for Package

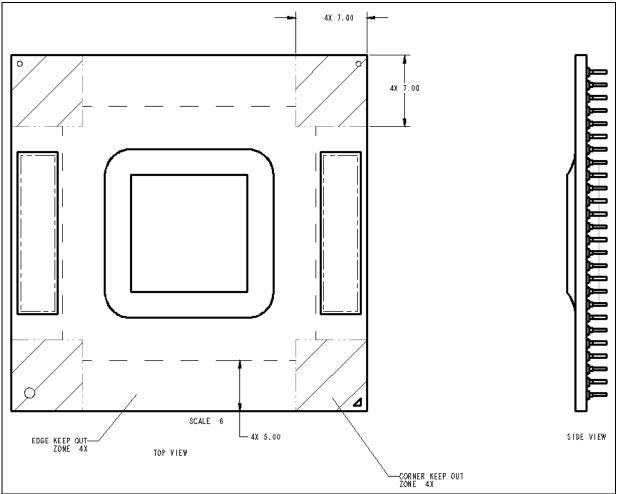

#### Figure 7. Package Dimensions (Top and Side View: Two of Two)

Notes:

1. Dimensions are in millimeters [inches].

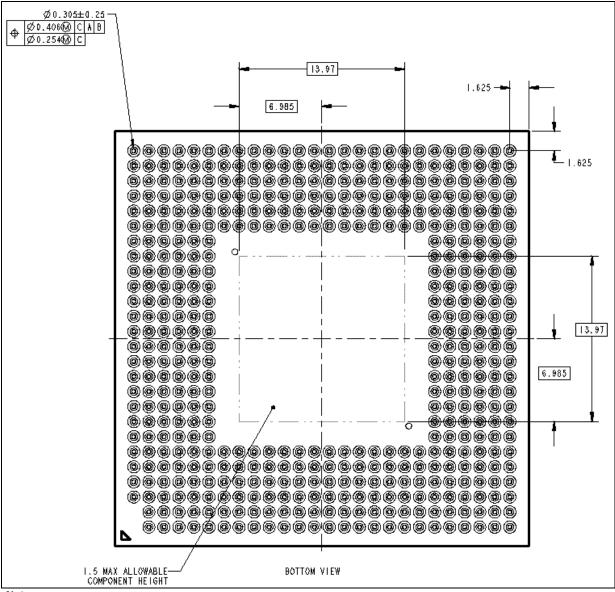

#### Figure 8. Package Dimensions (Bottom View: Two of Two)

Notes:

1. Dimensions are in millimeters [inches].

# 3.0 Thermal Specifications

# 3.1 Thermal Design Power

The Thermal Design Power (TDP) specification is listed in Table 2. Heat transfer through the micro FCPGA package and into the base board is negligible. The cooling capacity without a thermal solution is also limited, so Intel recommends the use of a heatsink for all usage conditions.

# 3.2 Maximum Allowed Component Temperature

The device must maintain a maximum temperature at or below the value specified in Table 2. The thermal solution is required to meet the temperatures specification while dissipating the Thermal Design Power. Section 5.0 includes guidelines for accurately measuring the package temperature.

| Component                                                                           | Parameter                 | Maximum | Notes                                                   |

|-------------------------------------------------------------------------------------|---------------------------|---------|---------------------------------------------------------|

| Dual-Core Intel <sup>®</sup> Xeon <sup>®</sup> processor LV<br>and ULV              | T <sub>JUNCTION MAX</sub> | 100 °C  | Maximum allowed component temperature during operation. |

| Dual-Core Intel <sup>®</sup> Xeon <sup>®</sup> processor LV<br>and ULV              | T <sub>JUNCTION MIN</sub> | 0 °C    | Minimum allowed component temperature during operation. |

| Dual-Core Intel <sup>®</sup> Xeon <sup>®</sup> processor ULV<br>at 1.66 GHz         | TDP                       | 15 W    |                                                         |

| Dual-Core Intel <sup>®</sup> Xeon <sup>®</sup> processor LV at 2.0 GHz and 1.66 GHz | TDP                       | 31 W    |                                                         |

#### Table 2. Thermal Design Power (TDP) Specifications

# 4.0 Mechanical Specifications

# 4.1 Package Mechanical Requirements

The package level requirement are detailed in Section 2.0 including the maximum pressure allowed on the bare die package. More information may be available in the *Dual-Core Intel<sup>®</sup> Xeon<sup>®</sup> processor LV and ULV Datasheet*.

## 4.2 Package Keep-Out Zones Requirements

The heatsink should not touch the package in the areas shown in Figure 7. However, the heatsink should include a means to prevent the heatsink from forming an electrical short with the capacitors placed on the top side of the package. Suitable methods include using electrically insulated gasket material at the base of the heatsink.

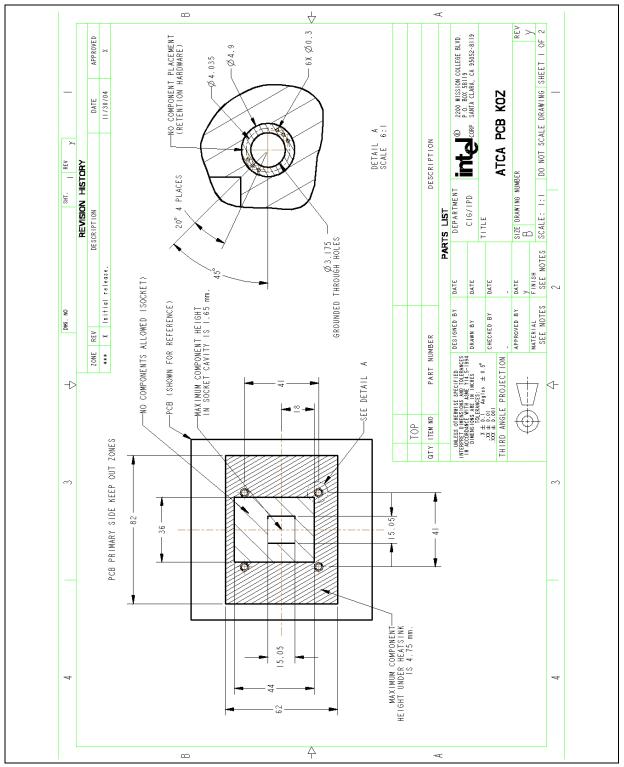

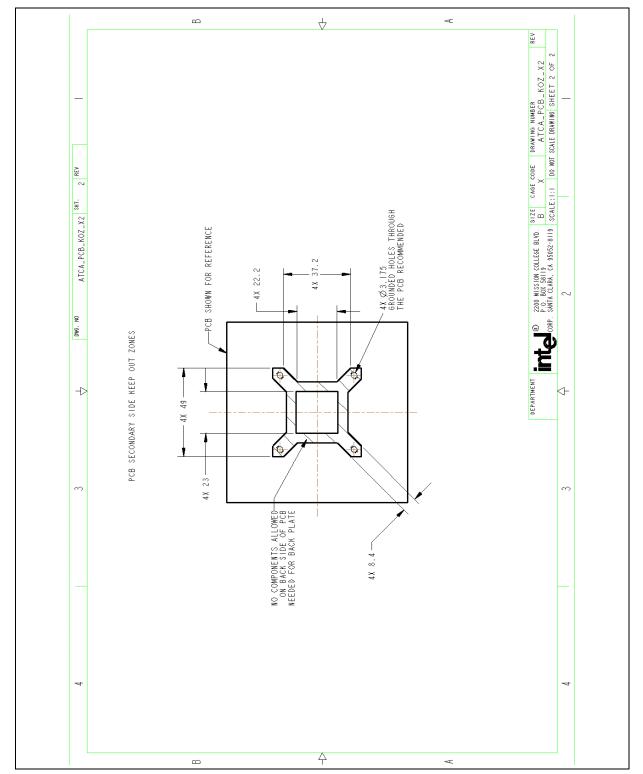

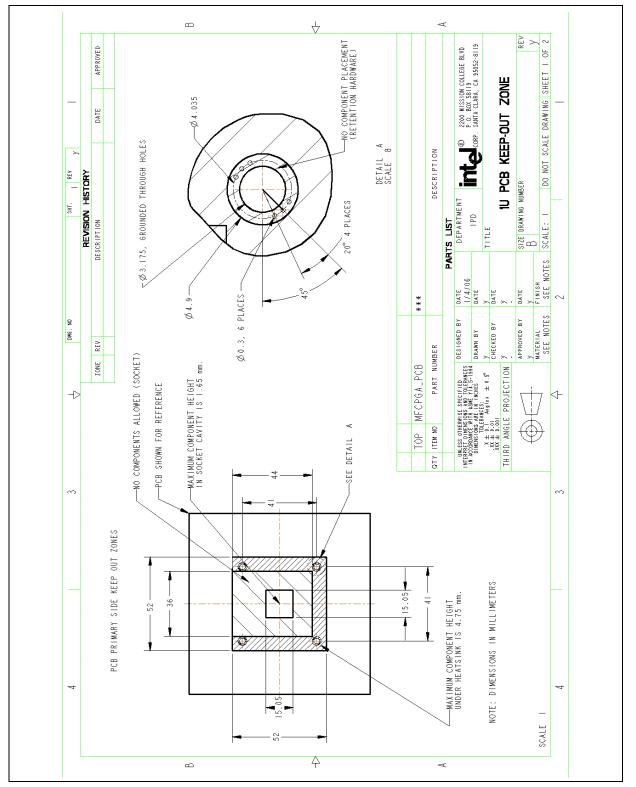

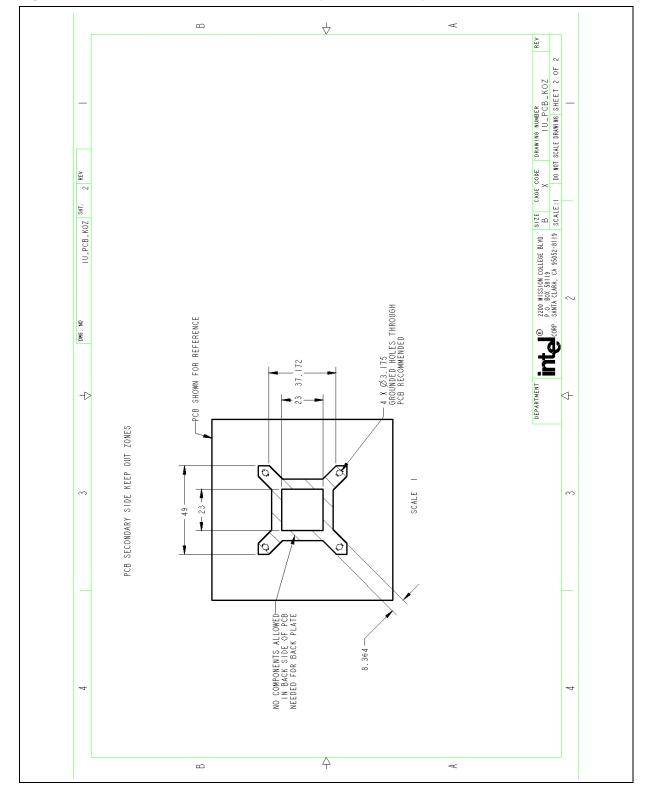

# 4.3 Board Level Keep-Out Zone Requirements

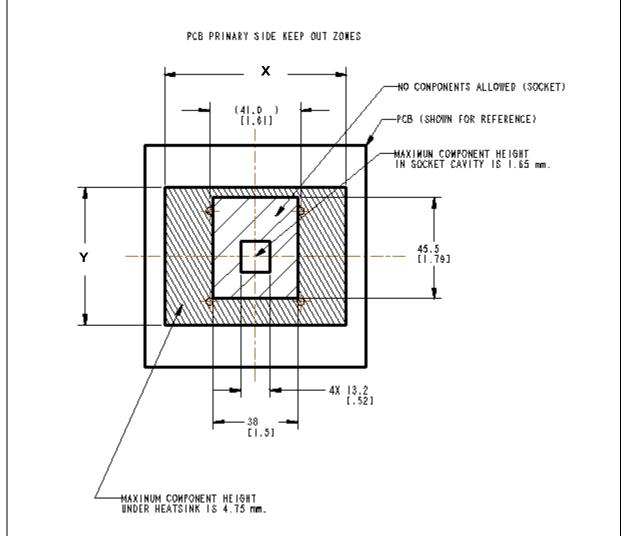

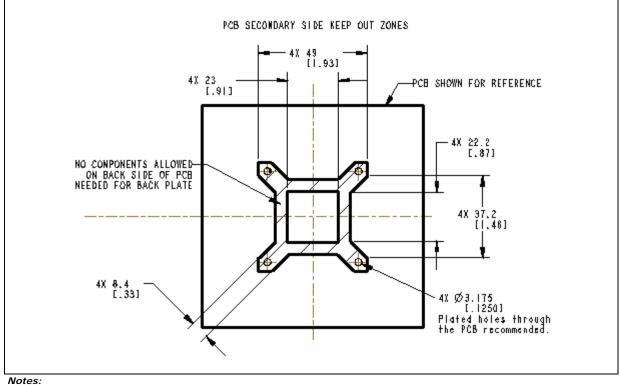

A general description of the keep-out zones and mounting hole pattern for the reference thermal solutions are shown in Figure 9 and Figure 10. Detailed drawings for the PCB keep-out zones are contained in Appendix B, "Mechanical Drawings". Components placed between the underside of the heatsink and motherboard cannot exceed 4.75 mm in height when using heatsinks that extend beyond the socket envelope shown in Figure 9.

Figure 9. Board Level Primary Side Keep-Out Zone Requirements

Notes:

Dimensions are in millimeters [inches]. X and Y depend on the dimensions of the heatsink. 1. 2.

#### Figure 10. Board Level Secondary Side Keep-Out Zone Requirements

1. Dimensions are in millimeters [inches].

# 5.0 Thermal Solution Requirements

# 5.1 Characterizing the Thermal Solution Requirement

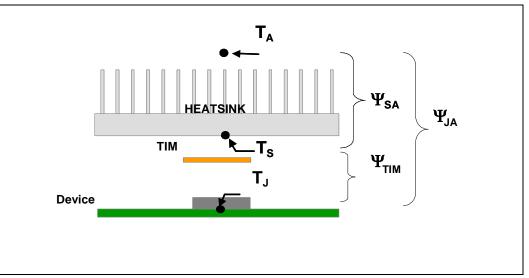

The idea of a "thermal characterization parameter"  $\Psi$  (pronounced Psi), is a convenient way to characterize the performance needed for the thermal solution and to compare thermal solutions in identical situations (i.e., heating source, local ambient conditions, etc.). The thermal characterization parameter is calculated using total package power, whereas actual thermal resistance,  $\theta$  (theta), is calculated using actual power dissipated between two points. Measuring actual power dissipated into the heatsink is difficult, since some of the power is dissipated via heat transfer into the package and board.

The junction-to-local ambient thermal characterization parameter ( $\Psi_{JA}$ ) is used as a measure of the thermal performance of the overall thermal solution. It is defined by Equation 1 and expressed in units of °C/W.

#### Equation 1. Junction-to-Local Ambient Thermal Characterization Parameter ( $\Psi_{JA}$ )

$$\Psi_{JA} = \frac{T_J - T_{LA}}{TDP}$$

Where:

$\Psi_{JA}$  = Junction-to-local ambient thermal characterization parameter (°C/W)

T<sub>JUNCTION MAX</sub> = Maximum allowed device temperature (°C)

T  $_{LA}$  = Local ambient temperature near the device (°C)

$\mathsf{TDP} = \mathsf{Thermal Design Power (W)},$  assumes all power dissipates through the top surface of the device.

The junction-to-local ambient thermal characterization parameter,  $\Psi_{JA}$ , is comprised of  $\Psi_{JS}$ , which includes the thermal interface material thermal characterization parameter, and of  $\Psi_{SA}$ , the sink-to-local ambient thermal characterization parameter:

#### Equation 2. Junction-to-Local Ambient Thermal Characterization Parameter ( $\Psi_{JA}$ )

$$\Psi_{JA} = \Psi_{JS} + \Psi_{SA}$$

Where:

$\Psi_{JS}\left(\Psi_{TIM}\right)$  = Thermal characterization parameter from the junction-to-sink, this also includes the resistance of the thermal interface material (°C/W)

$\Psi_{SA}$  = Thermal characterization parameter from heatsink-to-local ambient (°C/W)

$\Psi_{\text{TIM}}$  is strongly dependent on the thermal conductivity and thickness of the TIM between the heatsink and device package.

$\Psi_{SA}$  is a measure of the thermal characterization parameter from the bottom of the heatsink to the local ambient air.  $\Psi_{SA}$  is dependent on the heatsink material, thermal conductivity, and geometry. It is also strongly dependent on the air velocity through the fins of the heatsink. Figure 11 illustrates the combination of the different thermal characterization parameters.

#### Figure 11. Processor Thermal Characterization Parameter Relationships

# Example 1. Calculating the Required Thermal Performance for Dual-Core Intel<sup>®</sup> Xeon<sup>®</sup> processor LV

The cooling performance,  $\Psi_{JA,}$  is defined using the thermal characterization parameter:

- Define a target component temperature T<sub>JUNCTION</sub> and corresponding TDP.

- Define a target local ambient temperature, T<sub>LA</sub>.

The following provides an example of how you might determine the appropriate performance targets.

Assume:

- TDP = 31 W and  $T_{JUNCTION}$  = 100 °C

- Local processor ambient temperature,  $T_{LA} = 40$  °C.

Then the following could be calculated using Equation 1 for the given processor frequency:

$$\Psi_{JA} = \frac{T_J - T_{LA}}{TDP} = \frac{100 - 40}{31} = 1.94 \,^{\circ}C/W$$

To determine the required heatsink performance, a heatsink solution provider would need to determine  $\Psi_{JS}$  performance for the selected TIM and mechanical load configuration. If the heatsink solution were designed to work with a TIM material performing at  $\Psi_{TIM} \leq$  1.0 °C/W, solving from Equation 2, the performance needed from the heatsink is:

$$\Psi_{SA} = \Psi_{JA} - \Psi_{TIM} = 1.94 - 1.00 = 0.94 \ C/W$$

If the local processor ambient temperature is relaxed to 35 °C, the same calculation can be carried out to determine the new case-to-ambient thermal resistance:

$$\Psi_{JA} = \frac{T_J - T_{LA}}{TDP} = \frac{100 - 35}{31} = 2.09 \,^{\circ}C/W$$

It is evident from the above calculations that a reduction in the local ambient temperature has a significant effect on the junction-to-ambient thermal resistance requirement. This effect can contribute to a more reasonable thermal solution including reduced cost, heatsink size, heatsink weight, and a lower system airflow rate.

Table 3 summarizes the thermal budget required to adequately cool the processors. Since the results are based on air data at sea level, a correction factor would be required to estimate the thermal performance at other altitudes.

#### Table 3. Required Heatsink Thermal Performance ( $\Psi_{JA}$ )

| Device                                                               | $\Psi_{\text{JA}}$ (°C/W) at T_{LA} = 40 °C | at 55 °C |

|----------------------------------------------------------------------|---------------------------------------------|----------|

| 15 W Dual-Core Intel <sup>®</sup> Xeon <sup>®</sup><br>processor ULV | 4.00                                        | 3.00     |

| 31 W Dual-Core Intel <sup>®</sup> Xeon <sup>®</sup><br>processor LV  | 1.94                                        | 1.45     |

Notes:

$\rm T_{LA}$  is defined as the local (internal) ambient temperature measured approximately 1" upstream from the device. 1.

2.  $\Psi_{JA}$  is determined by (T<sub>JUNCTION</sub> - T<sub>LA</sub>)/TDP, so this value will change if any parameter changes.

# 6.0 Reference Thermal Solutions

Intel has developed reference thermal solutions designed to meet the cooling needs of the processor in embedded form factor applications. This chapter describes the overall requirements for the reference thermal solution including critical-to-function dimensions, operating environment, and verification criteria. This document details solutions that are compatible with the CompactPCI\*, AdvancedTCA\*, and Server System Infrastructure (1U and larger) form factors.

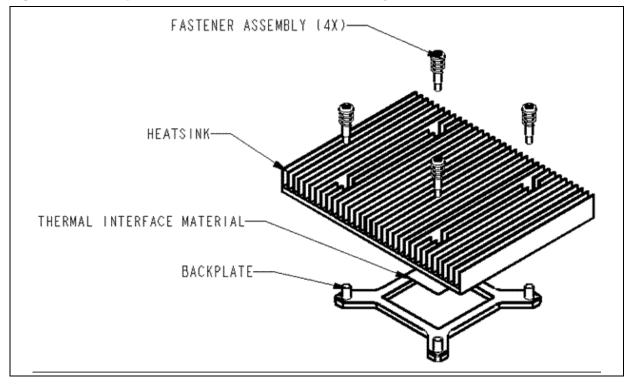

The heatsinks are attached to the board using a screw, spring and back plate assembly. The heatsink uses the fastener assembly (refer to Section 6.2) to mount to the PCB. Detailed drawings of this heatsink are provided in Appendix B, "Mechanical Drawings".

Figure 11 illustrates an example of the thermal solution assembly. Full mechanical drawings of the thermal solutions and the corresponding heatsink clip are provided in Appendix B, "Mechanical Drawings". Appendix A, "Thermal Solution Component Suppliers" contains vendor information for each thermal solution component.

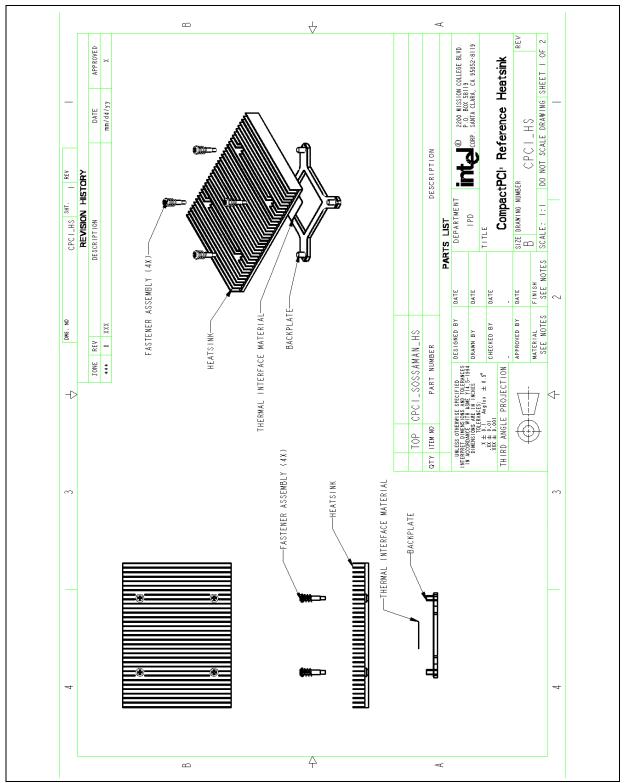

# 6.1 CompactPCI \* Reference Heatsink

The reference thermal solution compatible with the CompactPCI\* form factor is designed assuming a maximum ambient temperature (as measured outside the chassis) of 40 °C with a minimum volumetric airflow rate through each slot of 10 CFM. Assuming these boundary conditions are met, the reference thermal solutions will meet the thermal specifications for the ULV Processor.

*Note:* The CompactPCI\* reference heatsink may not be suitable for the 31 W Processor.

## 6.2 Mechanical Design

The reference heatsink is shown in Figure 12. The maximum component height is 13.716 mm, so the maximum heatsink height is constrained to 8.68 mm. The heatsink uses the fastener assembly (refer to Section 6.2) to mount to the PCB. Detailed drawings are provided in the Appendix B, "Mechanical Drawings".

Figure 12. CompactPCI \* Reference Heatsink Assembly

#### 6.2.1 Keep-Out Zone Requirements

The keep-out zone requirements on the PCB to use this heatsink are detailed in Appendix A, "Reference Heatsink". It is critical for the board designer to allocate space on the board for the heatsink since it extends beyond the footprint of the socket.

### 6.2.2 Thermal Performance

The CompactPCI\* reference heatsink should be made from copper to achieve the necessary thermal performance. Based on the boundary conditions stated (ambient temperature =  $40 \,^{\circ}$ C), the heatsink will meet the thermal performance needed to cool ULV Processor in the CompactPCI\* form factor. The heatsink performance versus volumetric airflow rate is shown in Figure 13.

The system integrator can make trade-offs to determine the best heatsink material to use based on usage conditions. For example, a higher ambient temperature might be considered with use of the copper heatsink.

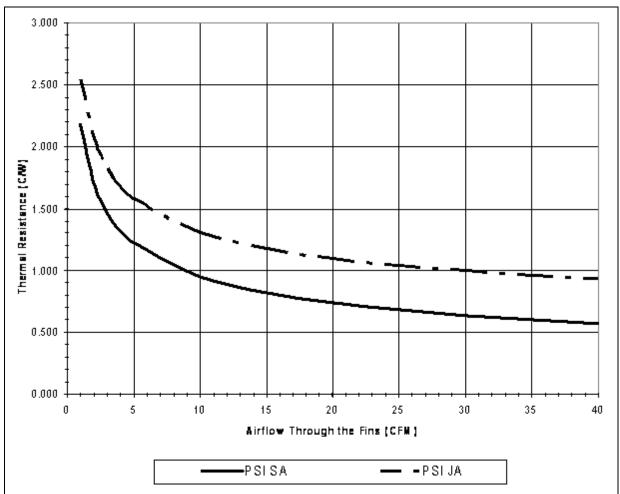

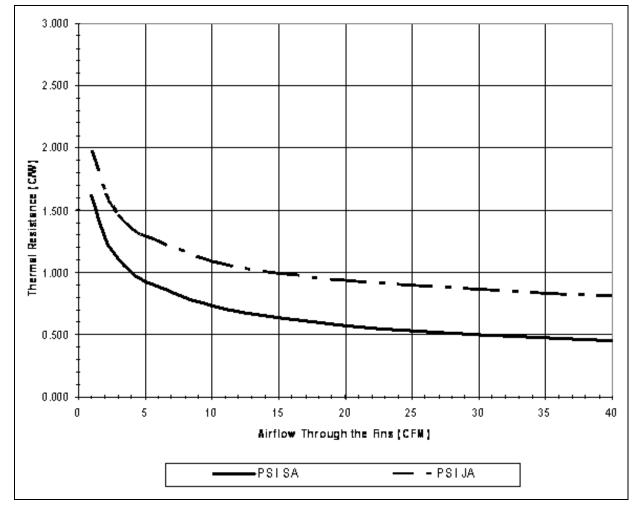

#### Figure 13. CompactPCI \* Reference Heatsink Thermal Performance vs. Volumetric Airflow Rate

# 6.3 AdvancedTCA\* Reference Heatsink

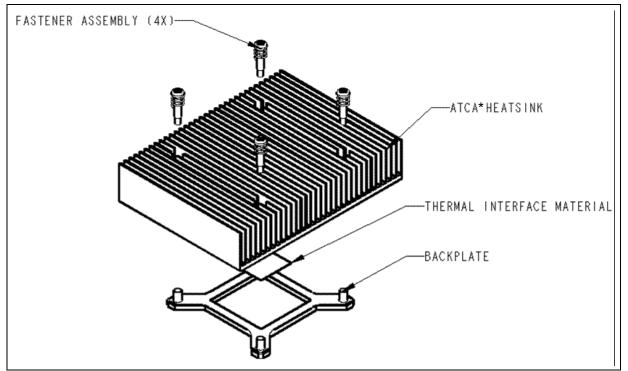

The reference thermal solution compatible with the AdvancedTCA\* form factor is designed assuming a maximum ambient temperature (as measured outside the chassis) of 40 °C with a minimum volumetric airflow rate through the AdvancedTCA slot of 30 CFM. Assuming these boundary conditions are met, the reference thermal solutions will meet the thermal specifications for both the 15 W and 31 W processor.

Furthermore, the AdvancedTCA reference heatsink is suitable for dual-processor configurations. Section 6.7 provides further guidance to optimize the component placement to enable the dual processor configuration.

*Note:* The AdvancedTCA reference heatsink is suitable for the 15 W Processor. It is also suitable for the 31 W Processor if the system is properly designed. For example, Figure 14 illustrates optimal processor placement on a PCB to ensure that both processors receive cool (not preheated) airflow. This enables the heatsinks to dissipate the same amount of power on each processor. The platform designer must determine the processor cooling limitations for their specific designs and decide if the 31 W processor can be cooled.

## 6.3.1 Mechanical Design

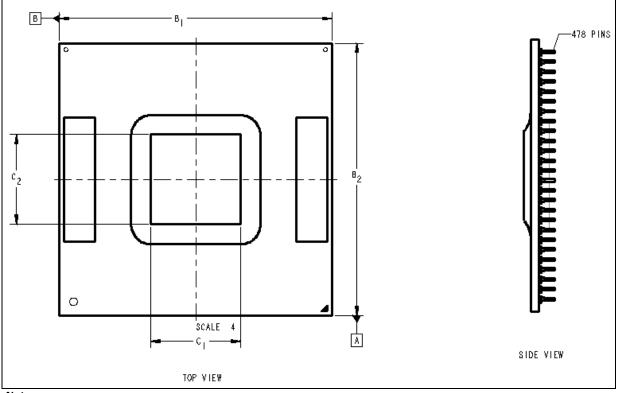

The AdvancedTCA reference thermal solution is shown in Figure 14. The maximum component height for this form factor is 21.33 mm, so the maximum heatsink height is constrained to 16.27 mm. The heatsink uses the fastener assembly (refer to Section 6.2) to mount to the PCB. Detailed drawings of this heatsink are provided in Appendix B, "Mechanical Drawings".

## 6.3.2 Keep-Out Zone Requirements

The keep-out zone requirements on the PCB to use this heatsink are detailed in Appendix A, "Reference Heatsink". It is critical for the board designer to allocate space on the board for the heatsink since it extends beyond the footprint of the socket.

#### 6.3.3 Thermal Performance

The AdvancedTCA reference heatsink should be made from copper to achieve the necessary thermal performance. Based on the boundary conditions stated (ambient temperature = 40 °C), the heatsink will meet the thermal performance needed to cool both the 15 W and 31 W processor in the AdvancedTCA form factor. The heatsink performance versus volumetric airflow rate is shown in Figure 15.

The system integrator can make trade-offs to determine the best heatsink material to use based on usage conditions. For example, a higher ambient temperature might be considered with use of the copper heatsink.

#### Figure 15. AdvancedTCA\* Reference Heatsink Thermal Performance vs. Volumetric Airflow Rate

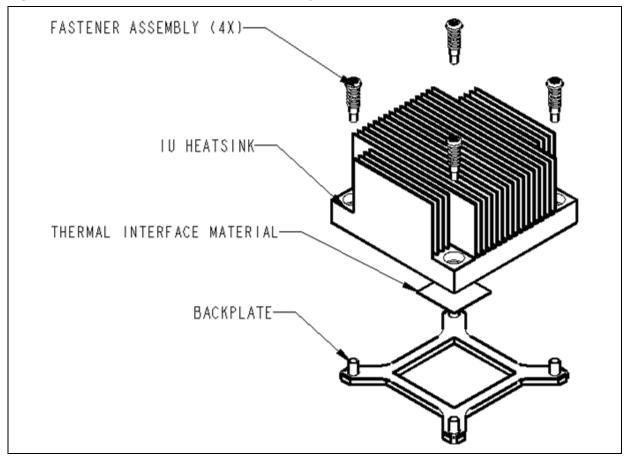

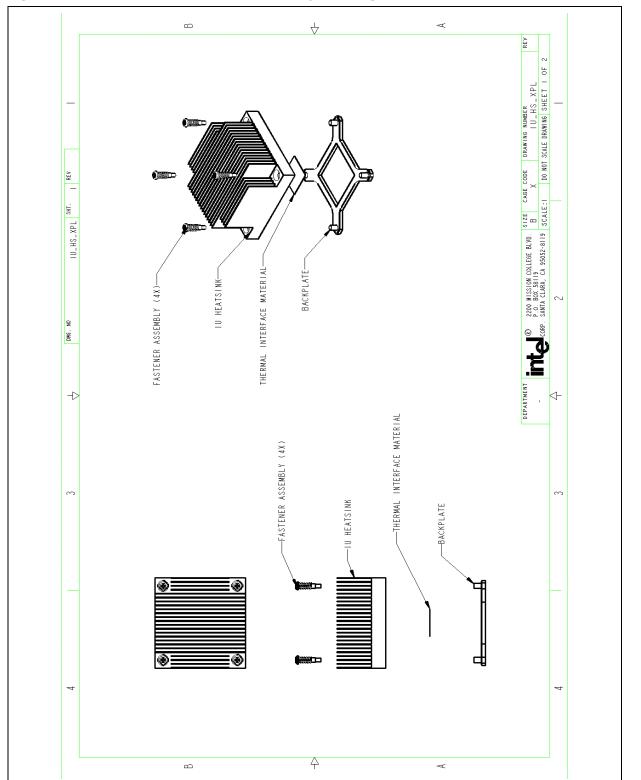

# 6.4 1U+ Reference Heatsink

The reference thermal solution compatible with the 1U and larger form factor is designed assuming a maximum ambient temperature (as measured outside the chassis) of 40 °C with a minimum volumetric airflow rate through the heatsink fins of 5 CFM. Assuming these boundary conditions are met, the reference thermal solutions will meet the thermal specifications for both the 15 W and 31 W processor.

Furthermore, the 1U reference heatsink is suitable for dual processor configurations. Section 6.7 provides further guidance to optimize the component placement to enable the dual processor configuration.

## 6.4.1 Mechanical Design

The 1U reference thermal solution is shown in Figure 16. The maximum heatsink height is constrained to 27 mm. The heatsink uses the fastener assembly (refer to Section 6.2) to mount to the PCB. Detailed drawings of this heatsink are provided in Appendix B, "Mechanical Drawings".

#### Figure 16. 1U Reference Heatsink Assembly

#### 6.4.2 Keep-Out Zone Requirements

The keep-out zone requirements on the PCB to use this heatsink are detailed in Appendix B, "Mechanical Drawings". It is critical for the board designer to allocate space on the board for the heatsink since it extends beyond the footprint of the socket.

#### 6.4.3 Thermal Performance

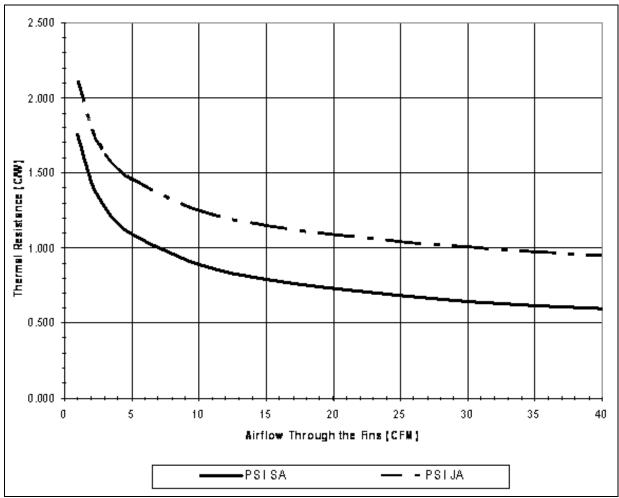

The 1U reference heatsink should be made from copper to achieve the necessary thermal performance. Based on the boundary conditions stated (T ambient = 40 °C), the heatsink will meet the thermal performance needed to cool both the 15 W and 31 W processor in the 1U form factor. The heatsink performance versus volumetric airflow rate is shown in Figure 17.

The system integrator can make trade-offs to determine the best heatsink material to use based on usage conditions. For example, a higher ambient temperature might be considered with use of the copper heatsink.

Figure 17. 1U Reference Heatsink Thermal Performance versus Volumetric Airflow Rate

# 6.5 Thermal Interface Material (TIM)

The thermal interface material provides improved conductivity between the die and heatsink. It is important to understand and consider the impact of the interface between the die and heatsink base to the overall thermal solution. Specifically, the bond line thickness, interface material area, and interface material thermal conductivity must be selected to optimize the thermal solution.

It is important to minimize the thickness of the thermal interface material (TIM), commonly referred to as the bond line thickness. A large gap between the heatsink base and the die yields a greater thermal resistance. The thickness of the gap is determined by the flatness of both the heatsink base and the die, plus the thickness of the thermal interface material, and the clamping force applied by the heatsink attachment method. To ensure proper and consistent thermal performance, the TIM and application process must be properly designed.

The processor reference thermal solution uses Honeywell\* PCM45F. Alternative materials can be used at your discretion. Regardless, the entire heatsink assembly, including the heatsink, and TIM (including attach method), must be validated together for specific applications.

It is important to realize that the thermal interface material degrades over time and exposure to environmental effects. Figure 13, Figure 15, and Figure 17 show the junction-to-ambient thermal performance assuming the "end of life" performance for the reference TIM. End of life usually occurs in to 5 to 7 years. Actual test data may differ from the values shown since the TIM thermal resistance will be comparable to the "beginning of life" impedance. It is common for the TIM impedance to increase significantly over time (i.e., > 2x). The end user must ensure that they account for the TIM thermal performance over the expected lifetime of the computing system.

# 6.6 Heatsink Orientation

All of the heatsinks were designed to maximize the available space within the volumetric keep-out zone and their respective form factor limitations. These heatsinks must be oriented in a specific direction relative to the processor keep-out zone and airflow. In order to use these designs, the processor must be placed on the PCB in an orientation so the heatsink fins will be parallel to the airflow. Figure 18 illustrates this orientation.

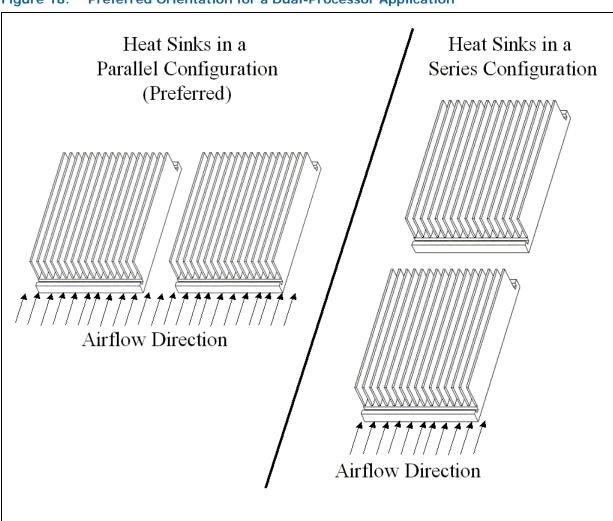

# 6.7 Dual Processor Considerations

The heatsink designs presented are suitable for use in dual-processor configurations. However additional precautions must be taken with the orientation of the processors on the motherboard. The results of computer modeling and testing indicate that processors placed in series, that is one processor placed directly behind the other relative to the airflow, will have a higher CPU temperature when compared to processors placed in parallel (side-by-side relative to the airflow). As a result, it is strongly recommended that the processors be placed in the parallel configuration for optimized thermal performance. For a better understanding, Figure 18 illustrates the preferred configuration.

#### Figure 18. Preferred Orientation for a Dual-Processor Application

# 7.0 Thermal Metrology

The system designer must make measurements to accurately determine the performance of the thermal solution. The heatsink designs must be validated using a thermal test vehicle. The thermal test vehicle is a device that simulates the thermal characteristics of the processor. It is also recommended to perform a final verification test of the heatsink with an actual processor in a real working environment.

This section provides guidelines on techniques to perform thermal tests including; Section 7.2 provides guidelines on how to accurately measure the component temperature, Section 7.3 details the use of the thermal test vehicle, and Section 7.3 provides information on running a power simulation software that will emulate anticipated thermal design powers on an actual processor.

# 7.1 Heatsink Validation Using Thermal Test Vehicles

Contact your Intel representative for more information about the thermal test vehicle.

### 7.2 Die Temperature Measurements

The component  $T_{JUNCTION}$  must be maintained at or below the maximum temperature specification as noted in Figure 6. The best method to measure the die temperature is using the Digital Thermal Sensor as described in the processor's datasheet. Note that the Digital Thermal Sensor can only be read through a Model Specific Register (MSR) of the processor.

*Note:* The legacy on board thermal diode is not recommended for performing heatsink validation. The thermal diode is suitable for long term trending data, but is not an accurate indicator of the processor's temperature.

## 7.3 Power Simulation Software

The power simulation software is a utility designed to dissipate the thermal design power on a processor. To assess the thermal performance of the processor thermal solution under "worst-case realistic application" conditions, Intel has developed a software utility that operates the processor at near worst-case power dissipation.

The power simulation software being developed should only be used to test customer thermal solutions at or near the thermal design power. For power supply current, please refer to each component's datasheet for the  $I_{CC}$  (Max Power Supply Current) specification. Contact your Intel representative for more information.

# 7.4 Additional Thermal Features

The Dual-Core Intel<sup>®</sup> Xeon<sup>®</sup> processor LV and ULV supports other thermal features including the Intel<sup>®</sup> Thermal Monitor, PROCHOT#, FORCEPR#, and THERMTRIP# Signal Pins. Details for using these features are contained in the processor datasheet.

# 8.0 Reliability Guidelines

Each motherboard, heatsink and attach combination may vary the mechanical loading of the component. The user should carefully evaluate the reliability of the completed assembly prior to use in high volume. Some general recommendations are shown in Table 4.

#### Table 4. Reliability Requirements

| Test             | Requirement                                                               | Pass/Fail Criteria                             |

|------------------|---------------------------------------------------------------------------|------------------------------------------------|

| Mechanical Shock | 50 g, board level, 11 msec, 3 shocks/axis                                 | Visual Check and Electrical<br>Functional Test |

| Random Vibration | 7.3 g, board level, 45 min/axis, 50 Hz to 2000<br>Hz                      | Visual Check and Electrical<br>Functional Test |

| Temperature Life | 85 °C, 2000 hours total, checkpoints at 168,<br>500, 1000, and 2000 hours | Visual Check                                   |

| Thermal Cycling  | -5 °C to +70 °C, 500 cycles                                               | Visual Check                                   |

| Humidity         | 85% relative humidity, 55 °C, 1000 hours                                  | Visual Check                                   |

#### Notes:

1. The above tests should be performed on a sample size of at least 12 assemblies from three lots of

material.

2. Additional Pass/Fail Criteria may be added at the discretion of the user.

# Appendix A Thermal Solution Component Suppliers

# A.1 Reference Heatsink

#### Table 5.Reference Heatsink

| Part                                          | Supplier<br>(Part Number)          | Contact Information                                                    |  |

|-----------------------------------------------|------------------------------------|------------------------------------------------------------------------|--|

| AdvancedTCA* Heatsink<br>CompactPCI* Heatsink | ECC-00177-01-GP<br>ECC-00178-01-GP | Cooler Master*<br>Wendy Lin                                            |  |

| 1U Passive Heatsink                           | ECC-00179-01-GP                    | 510-770-8566, x211                                                     |  |

| Active Heatsink                               | EEP-N41CS-I1-GP                    | Wendy@coolermaster.com                                                 |  |

| Thermal Interface Material<br>PCM45F          | PCM45F                             | Honeywell*<br>Paula Knoll<br>858-279-2956<br>paula.knoll@honeywell.com |  |

**Note:** The enabled components may not be currently available from all suppliers. Contact the supplier directly to verify time of component availability.

# **Appendix B Mechanical Drawings**

Table 6 lists the mechanical drawings included in this appendix.

#### Table 6. Mechanical Drawing List

| Description                                                                | Figure Number |

|----------------------------------------------------------------------------|---------------|

| AdvancedTCA* Reference Heatsink PCB Keep-Out Zone Requirements: One of Two | 19            |

| AdvancedTCA* Reference Heatsink PCB Keep-Out Zone Requirements: Two of Two | 20            |

| AdvancedTCA* Reference Heatsink Assembly Drawing                           | 21            |

| AdvancedTCA* Reference Heatsink Drawing                                    | 22            |

| CompactPCI* Reference Heatsink PCB Keep-Out Zone Requirements: One of Two  | 23            |

| CompactPCI* Reference Heatsink PCB Keep-Out Zone Requirements: Two of Two  | 24            |

| CompactPCI* Reference Heatsink Assembly Drawing                            | 25            |

| CompactPCI* Reference Heatsink Drawing                                     | 26            |

| 1U Reference Heatsink PCB Keep-Out Zone Requirements: One of Two           | 27            |

| 1U Reference Heatsink PCB Keep-Out Zone Requirements: Two of Two           | 28            |

| 1U Reference Heatsink Assembly Drawing                                     | 29            |

| 1U Reference Heatsink Drawing                                              | 30            |

Mechanical Drawings

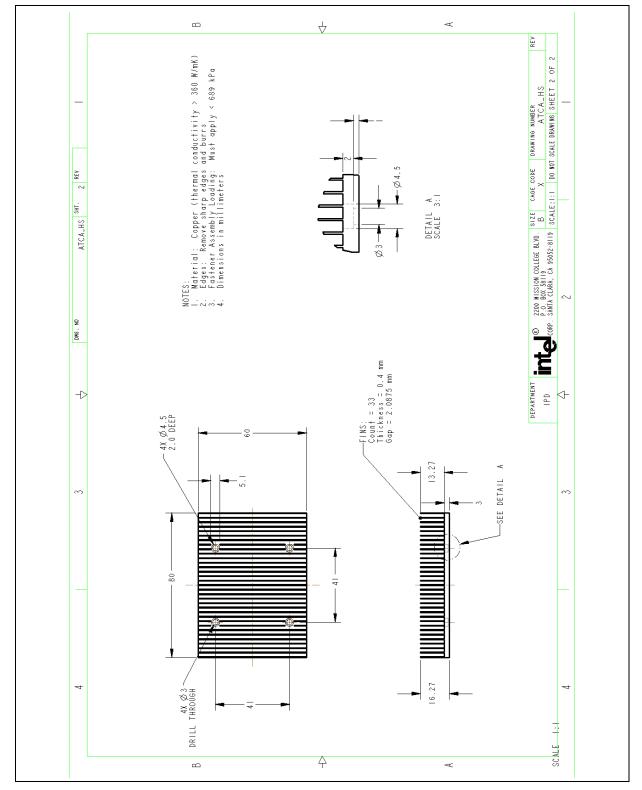

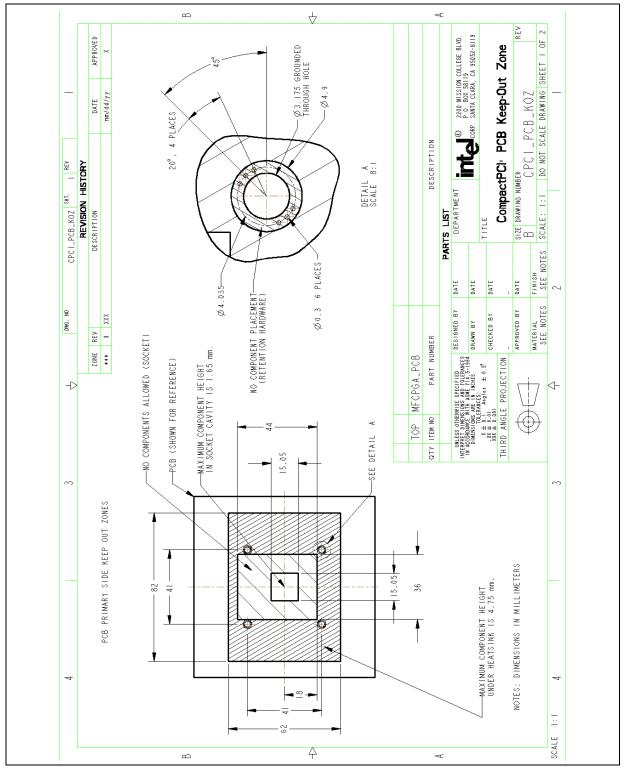

# Figure 19. AdvancedTCA\* Reference Heatsink PCB Keep-Out Zone Requirements: One of Two

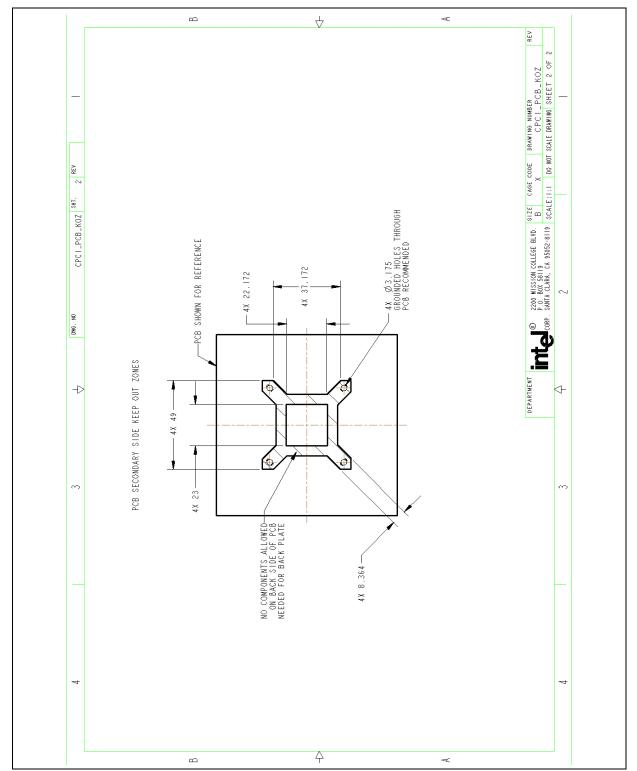

# Figure 20. AdvancedTCA\* Reference Heatsink PCB Keep-Out Zone Requirements: Two of Two

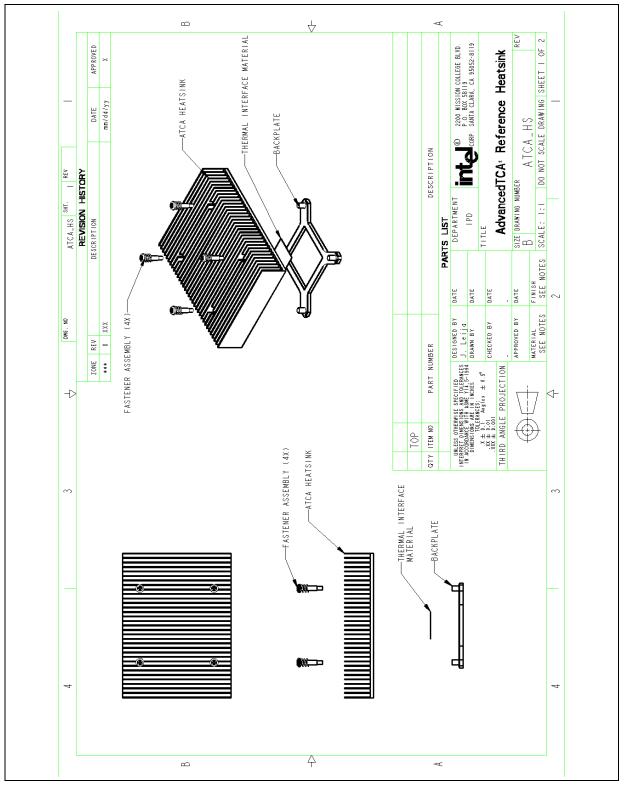

#### Figure 21. AdvancedTCA\* Reference Heatsink Assembly Drawing

#### Figure 22. AdvancedTCA\* Reference Heatsink Drawing

Mechanical Drawings

# Figure 23. CompactPCI \* Reference Heatsink PCB Keep-Out Zone Requirements: One of Two

# Figure 24. CompactPCI \* Reference Heatsink PCB Keep-Out Zone Requirements: Two of Two

Figure 25. CompactPCI \* Reference Heatsink Assembly Drawing

#### Figure 26. CompactPCI \* Reference Heatsink Drawing

(intel)

Figure 27. 1U Reference Heatsink PCB Keep-Out Zone Requirements: One of Two

#### Figure 28. 1U Reference Heatsink PCB Keep-Out Zone Requirements: Two of Two

Figure 29. 1U Reference Heatsink Assembly Drawing