# VRM 8.4 DC–DC Converter Design Guidelines

October 2001

Order Number 245335-006

Information in this document is provided in connection with Intel® products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel® products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

This document contains information on products in the design phase of development. Do not finalize a design with this information. Revised information will be published when the product is available. Verify with your local sales office that you have the latest datasheet before finalizing a design.

Intel processors may contain design defects or errors known as errata, which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Copyright © Intel Corporation 2000, 2001.

Intel and the Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and foreign countries.

\*Other names and brands may be claimed as the property of others.

# **Table Of Contents**

| 1.         | ELECTRICAL SPECIFICATIONS                     | 5              |

|------------|-----------------------------------------------|----------------|

| 1.1        | Output Requirements                           | 5              |

| 1.2        | Input Voltage and Current                     | 8              |

| 1.3        | Input Controls                                | 8              |

| 1.4        | <b>Module Test Conditions</b>                 | 9              |

| 1.5        | Efficiency                                    | 10             |

| 1.6        | Protection                                    | 10             |

| 1.7        | Current Sharing                               | 10             |

|            |                                               |                |

| 2.         | MODULE REQUIREMENTS                           | 10             |

| 2.<br>3.   | MODULE REQUIREMENTS TESTS AND STANDARDS       | 10<br>12       |

|            |                                               |                |

| 3.         | TESTS AND STANDARDS                           | 12             |

| 3.         | TESTS AND STANDARDS Reliability               | 12<br>12       |

| 3.1<br>3.2 | TESTS AND STANDARDS Reliability Environmental | 12<br>12<br>13 |

# **Applications and terminology**

This document defines a range of DC-to-DC converters to meet the power requirements of computer systems using Intel microprocessors. It does not attempt to define a specific voltage regulator module (VRM) implementation. VRM requirements will vary according to the needs of different computer systems, including the range of processors a specific VRM is expected to support in a system. The "VRM" designation may refer to a voltage regulator on a system board, as well as to the module defined in Section 2.

The VRM 8.4 definition is specifically intended to meet the needs of Intel Celeron™ and Pentium<sup>®</sup> III processor-based systems.

Each guideline is placed into one of three categories. The category immediately follows the section heading and is one of the following:

**REQUIRED**: An essential part of the design—necessary to meet processor voltage and current

specifications.

**EXPECTED**: Part of Intel's processor power definitions; necessary for consistency with the

designs of many systems and power devices.

**PROPOSED**: Normally met by of this type of DC-to-DC converter and, therefore, included as

a design target. Likely to be specified by system manufacturers.

# 1. Electrical Specifications

## 1.1 Output Requirements

**REQUIRED**

A VRM 8.4 DC-DC converter supplies the required voltage and current to an Intel<sup>®</sup> Pentium<sup>®</sup> III or Celeron<sup>TM</sup> processor as shown in the following tables.

Specifications in this document assume that the DC-DC converter will be either a VRM circuit on the motherboard or a module with the necessary complement of external capacitance. For either implementation, Vcc<sub>CORE</sub> must meet the specifications shown at the processor pins.

The following conditions apply to the specifications:

- · Specifications apply to all frequencies unless specific frequencies are listed.

- $\cdot$  Icc<sub>CORE</sub> is measured at nominal Vcc<sub>CORE</sub> under maximum signal loading conditions.

- · Note that these values are for reference only. Please refer to the appropriate component documentation (e.g. data sheet) for these specifications.

#### Static Voltage Regulation

**REQUIRED**

The output voltage measured at the processor input pins on the system board (or test point in Figure 1) must be within the static range shown in the respective tables, except for input voltage turn-on and turn-off and for current transitions as shown under "Transient Voltage Regulation" below. The static limits apply to ambient temperatures between 0°C and 60°C. Static voltage regulation includes:

- DC output initial voltage set point adjust

- Output ripple and noise

- Output load ranges specified in tables above

- Temperature and warm up specified in Section 3.1.

#### Transient Voltage Regulation

**REQUIRED**

The output voltage measured at the processor input pins on the system board (or test point in Figure 1) must be within the transient range shown in the respective tables. This includes the transition from Icc<sub>SGNT</sub>CORE (Stop-Grant state) to Icc<sub>CORE</sub> (Maximum) or Icc<sub>CORE</sub> (Maximum) to Icc<sub>SGNT</sub>CORE (Stop-Grant state), except as noted for input voltage turn-on and turn-off. This tolerance must include the variation due to static voltage regulation plus the effects of the output load transient at the VRM output pins. Load transient response may not exceed the static voltage specification for longer than 100 µsec. The toggle rate for the output load transition must range from 100 Hz to 100 kHz. Under the above conditions and for all toggle rates, the transient response must be measured over a 20 MHz frequency band, and at ambient temperatures between 25°C and 50°C.

| Table 1, Pentium® III Processo | r Voltage and | <b>Current S</b> | pecifications <sup>1</sup> |

|--------------------------------|---------------|------------------|----------------------------|

|--------------------------------|---------------|------------------|----------------------------|

|                          |                                            | Core Freq  | uency <sup>2</sup> |        |              |       |      |

|--------------------------|--------------------------------------------|------------|--------------------|--------|--------------|-------|------|

| Symbol                   | Parameter                                  |            |                    | Min    | Typical      | Max   | Unit |

| $Vcc_{CORE}$             | Vcc <sub>CORE</sub> Vcc for processor core |            | Maximum VID        |        | 2.05         |       | V    |

|                          |                                            | CPUID 068A |                    |        | 1.75         |       |      |

|                          |                                            | CPUID (    | )686 <sup>2</sup>  |        | 1.70 –       |       |      |

|                          |                                            |            |                    |        | 1.75         |       |      |

|                          |                                            | CPUID (    | )683 <sup>2</sup>  |        | 1.60 –       |       |      |

|                          |                                            |            | 2                  |        | 1.70         |       |      |

|                          |                                            | CPUID (    | )681 <sup>2</sup>  |        | 1.60 –       |       |      |

| Vcc <sub>CORE</sub>      | Vcc <sub>CORE</sub> tolerance at           | All,       | Static             | -0.080 | 1.65         | 0.040 | V    |

| tolerance                | processor connector pins                   | , ,        | Transient          | -0.080 |              | 0.050 | · •  |

| torerance                | on system board (or test                   | except:    |                    |        |              |       | ***  |

|                          | point in Figure 1) —                       | CPUID 0683 | Static             | -0.050 |              | 0.040 | V    |

|                          | SC242                                      | at 1 GHz   | Transient          | -0.050 |              | 0.050 |      |

|                          | Vcc <sub>CORE</sub> tolerance at           | < 933 MHz  | Static             | -0.080 |              | 0.040 | V    |

|                          | processor socket pins on                   |            | Transient          | -0.130 |              | 0.080 |      |

|                          | system board (or test point                | 933 MHz –  | Static             | -0.080 |              | 0.040 | V    |

|                          | in Figure 1) — FC-PGA                      | 1.0 GHz    | Transient          | -0.110 |              | 0.080 |      |

| Icc <sub>CORE</sub>      | Icc for processor core <sup>3,4</sup>      | 600 M      | Hz                 |        |              | 12.6  | A    |

|                          |                                            | 633 M      | Hz                 |        |              | 13.0  |      |

|                          |                                            | 667 M      |                    |        |              | 13.9  |      |

|                          |                                            | 700 M      |                    |        |              | 14.8  |      |

|                          | 733 MHz<br>766 MHz                         |            |                    |        | 15.4<br>16.0 |       |      |

|                          |                                            | 800 M      |                    |        |              | 16.6  |      |

|                          |                                            | 850 M      |                    |        |              | 17.3  |      |

|                          |                                            | 950 M      |                    |        |              | 19.4  |      |

|                          |                                            | 1 GH       |                    |        |              | 20.2  |      |

|                          |                                            | 1.1 G      | Hz                 |        |              | 22.6  |      |

| Icc <sub>SGNT</sub> CORE | Icc for Stop-Grant Vcc <sub>CORE</sub>     |            |                    |        |              | 6.9   | A    |

| Icc <sub>DSLP</sub> CORE | Icc for Deep-SleepVcc <sub>CORE</sub>      |            |                    |        |              | 6.9   | A    |

| dIcc <sub>CORE</sub> /dt | Icc slew rate — SC242                      |            |                    |        |              | 20    | A/μs |

| dIcc <sub>CORE</sub> /dt | Icc slew rate — FC-PGA                     |            |                    |        |              | 240   | A/μs |

- 1. Please see the latest corresponding data sheet for processor requirements, including Vcc and Icc specifications for each CPUID and frequency.

- 2. This table shows specifications for frequencies only 600 MHz and above

- 3. Icc values shown are at Vcc = 1.75V.

- 4. Note: Maximum Icc<sub>CORE</sub> measurement note (applies to Table 1-3) Voltage regulators may be designed with a minimum equivalent internal resistance to ensure that the output voltage, at maximum current output, is no greater than the nominal (i.e., typical) voltage level of Vcc<sub>CORE</sub> (Vcc<sub>CORE-TYP</sub>). In this case the maximum current level for the regulator (Icc<sub>CORE-REG</sub>) can be reduced from the specified maximum Icc<sub>CORE</sub> (Icc<sub>CORE-MAX</sub>) and is calculated by the equation:

$$\begin{split} & Icc_{CORE-REG} = Icc_{CORE-MAX} \ X \ (\ Vcc_{CORE-TYP} \ -\ Vcc_{CORE} \ static \ tolerance) \ /\ Vcc_{CORE-TYP} \\ & For \ example, \ a \ VRM \ supporting \ the \ 1.0 \ GHz \ processor \ could \ be \ designed \ for: \\ & Icc_{CORE-REG} = 19.4 \ X \ (1.75 \ -\ 0.04) \ /1.75 = 19.0 \ A. \end{split}$$

| Symbol                   | Parameter                                                                    | (MHz u  | Frequency<br>nless shown<br>GHz) | Min    | Typical | Max          | Unit |

|--------------------------|------------------------------------------------------------------------------|---------|----------------------------------|--------|---------|--------------|------|

| Vcc <sub>CORE</sub>      | Vcc for processor core                                                       | All CF  | PUID 0686                        |        | 1.70    |              | V    |

|                          |                                                                              | CPUID   | 0683 ≥ 633                       |        | 1.65    |              |      |

|                          |                                                                              | CPUID   | 0683 < 633                       |        | 1.50    |              |      |

|                          |                                                                              | CPU     | ID 068A                          |        | 1.75    |              |      |

|                          | Vcc <sub>CORE</sub> tolerance at processor<br>connector pins on system board | All     | Static                           | -0.089 |         | 0.100        | V    |

|                          | (or test point in Figure 1) — PPGA                                           |         | Transient                        | -0.144 |         | 0.144        |      |

|                          | Vcc <sub>CORE</sub> tolerance at processor connector pins on system board    | All     | Static                           | -0.080 |         | 0.040        | V    |

|                          | (or test point in Figure 1) —<br>FC-PGA                                      |         | Transient                        | -0.130 |         | 0.080        |      |

| Icc <sub>CORE</sub>      | Icc for processor core                                                       |         | 600                              |        |         | 12.6         | A    |

|                          |                                                                              |         | 633                              |        |         | 13.0         |      |

|                          |                                                                              |         | 667                              |        |         | 13.9         |      |

|                          |                                                                              |         | 700<br>733                       |        |         | 14.8<br>15.4 |      |

|                          |                                                                              | 750     |                                  |        |         | 15.4         |      |

|                          |                                                                              |         | 767                              |        |         | 16.0         |      |

|                          |                                                                              | 800     |                                  |        |         | 16.6         |      |

|                          |                                                                              |         | 850                              |        |         | 17.3         |      |

|                          |                                                                              | 900     |                                  |        |         | 18.4         |      |

|                          |                                                                              | 1.0 GHz |                                  |        |         | 20.2         |      |

|                          |                                                                              | 1.      | 1 GHz                            |        |         | 22.6         |      |

| Icc <sub>SGNT</sub> CORE | Icc for Stop-Grant Vcc <sub>CORE</sub>                                       |         |                                  |        |         | 6.9          | A    |

| Icc <sub>DSLP</sub> CORE | Icc for Deep-SleepVcc <sub>CORE</sub>                                        |         |                                  |        |         | 6.6          | A    |

| dIcc <sub>CORE</sub> /dt | Icc slew rate                                                                |         |                                  |        |         | 240          | A/μs |

Table 2, Intel<sup>®</sup> Celeron<sup>TM</sup> Processor Voltage and Current Specifications

Note: Please see the latest corresponding data sheet for processor requirements, including Vcc and Icc specifications for each CPUID and frequency.

#### Output Ripple and Noise

**PROPOSED**

Ripple and noise are defined as periodic or random signals over a 20 MHz frequency band at the output pins under constant load. Output ripple should be consistent with the static voltage requirements.

#### Variation with Load

**PROPOSED**

To assist in providing margin during high-slew-rate current load transitions, the vendor may target module performance to provide for a positive offset (<40 mV) under minimum load conditions, and a negative offset (<40 mV) under maximum load conditions. This approach applies to the Vcc specifications in Table 1 and Table 2; the load line described in Figure 1 and Table 4 requires a different, specific set of voltage variations.

#### Turn-on Response Time

**PROPOSED**

The output voltage should be within its specified range within 10ms of the input reaching 95% of its nominal voltage.

#### Overshoot at Turn-On or Turn-Off

**REQUIRED**

Overshoot upon the application or removal of the input voltage under the conditions specified in Section 1.2 must be less than 10% above the initial set output voltage. No negative voltage may be present on any output during turn-on or turn-off.

### Power Good Output—PWRGD

**EXPECTED**

An open collector signal consistent with TTL DC specifications should be provided. This signal should transition to the open (>100K-ohm) state within 20 milliseconds of the input stabilizing within the range specified in Section 1.2. The signal should be in the low-impedance (to ground) state whenever Vout is more than  $\pm 12\%$  from nominal and be in the open state whenever Vcc<sub>CORE</sub> is within its specified range.

Some systems logically combine power-good signals from multiple processors and reset all processors if any processor's  $Vcc_{CORE}$  source fails. Other systems use VID codes for voltages below 1.8V for identification purposes. Such systems may require the VRM's PWRGD output to be in the high state when the VRM's  $Vcc_{CORE}$  output is disabled by VID inputs, including the no-processor code (11111). That is,

PWRGD = (Vcc<sub>CORE</sub> outputs within 12% of nominal) OR (output disabled in response to VID code).

## 1.2 Input Voltage and Current

## • Input Voltages EXPECTED

Available inputs are at  $12V \pm 5\%$ ,  $5V \pm 5\%$  and  $3.3V \pm 5\%$ . The VRM may use any single voltage or combination. These voltages are supplied by a conventional computer power supply through a cable to the motherboard. Input voltage requirements should be clearly marked on modules.

#### Load Transient Effects on Input Voltages

**PROPOSED**

The VRM should be able to provide for an output current step at the load from  $Icc_{CORE}$  (Stop-Grant state) to  $Icc_{CORE}$  (Maximum) or  $Icc_{CORE}$  (Maximum) to  $Icc_{CORE}$  (Stop-Grant state) within the time interval listed in Section 1.1. During this step response the input current di/dt should not exceed  $0.1A/\mu sec$ . For applications with multiple VRMs supplied by any voltage source on a board the step response di/dt of an individual VRM should not exceed  $0.04A/\mu sec$ .

# **1.3** Input Controls

These are signals that control the VRM (shown with the corresponding module pins in Table 4).

### Output Enable—OUTEN

**EXPECTED**

The VRM should accept an open collector signal consistent with TTL DC specifications for controlling the output voltage: The logic low state disables the output voltage.

#### Voltage Identification—VID[0:4]

**EXPECTED**

The VRM should accept five signals used to indicate the voltage required by the processor, as defined by Table 3. Five processor package pins will have an open—ground pattern corresponding to the voltage required by the individual processor unit. System designs may use pull-up resistors to pull open VID lines to a TTL VIH level. Generally these pull-ups will use the VRM input voltage, with an appropriate resistor divider if the input voltage is 12V. If used, such pull-ups should have a resistance of at least 10K ohms.

|                   | $Vcc_{CORE}^{2}$ |      |      |      |       |

|-------------------|------------------|------|------|------|-------|

|                   |                  |      |      |      |       |

| VID4 <sup>1</sup> | VID3             | VID2 | VID1 | VID0 | (VDC) |

| 0                 | 1                | 1    | 1    | 1    | 1.30  |

| 0                 | 1                | 1    | 1    | 0    | 1.35  |

| 0                 | 1                | 1    | 0    | 1    | 1.40  |

| 0                 | 1                | 1    | 0    | 0    | 1.45  |

| 0                 | 1                | 0    | 1    | 1    | 1.50  |

| 0                 | 1                | 0    | 1    | 0    | 1.55  |

| 0                 | 1                | 0    | 0    | 1    | 1.60  |

| 0                 | 1                | 0    | 0    | 0    | 1.65  |

| 0                 | 0                | 1    | 1    | 1    | 1.70  |

| 0                 | 0                | 1    | 1    | 0    | 1.75  |

| 0                 | 0                | 1    | 0    | 1    | 1.80  |

| 0                 | 0                | 1    | 0    | 0    | 1.85  |

| 0                 | 0                | 0    | 1    | 1    | 1.90  |

| 0                 | 0                | 0    | 1    | 0    | 1.95  |

| 0                 | 0                | 0    | 0    | 1    | 2.00  |

| 0                 | 0                | 0    | 0    | 0    | 2.05  |

**Table 3, Voltage Identification Code**

- 1. VID4 use is optional, for compatibility with VRM 8.1, 8.2, 8.3

- 2. Implementations should include the full range to 2.05V

#### 1.4 Module Test Conditions

#### **EXPECTED**

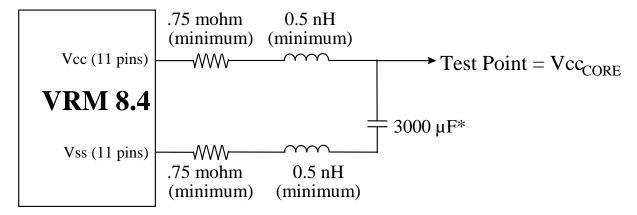

Voltage regulator modules are expected to require bulk capacitance near the processor connector. Figure 1 represents the distribution for test purposes.

Figure 1, Test Circuit for VRM with External Capacitance

<sup>\*</sup> Typical value, based on two OS-CON capacitors, each 1500µF. The actual value depends on board-specific requirements to meet the Vcc specifications at the processor connector.

## 1.5 Efficiency

**PROPOSED**

The efficiency of the VRM should be greater than:

- 80% at maximum output current

- 40% at 0.5A.

#### 1.6 Protection

These are features built into the VRM to prevent damage to itself or the circuits it powers.

## Over Voltage Protection

**PROPOSED**

Protection Level: The VRM should provide over-voltage protection by shutting itself off when the

output voltage rises beyond Vtrip. Vtrip should be set between 110% and 125% of

the voltage demanded by the processor (via the VID pins).

Voltage Sequencing: No combination of input voltages should falsely trigger an OVP event.

#### Short Circuit Protection

**PROPOSED**

Load short circuit is defined as a load impedance of less than approximately 90 m $\Omega$ . The VRM should be capable of withstanding a continuous short-circuit to the output without damage or over-stress to the unit.

#### Reset After Shutdown

**PROPOSED**

If the VRM goes into a shutdown state due to a fault condition on its outputs it should return to normal operation after the fault has been removed, or after the fault has been removed and power has been cycled off and on.

# 1.7 Current Sharing

**PROPOSED**

The pin designated Ishare is intended to permit two or more VRMs to balance the total current load between them. There is no expectation of interoperability between the sharing mechanisms of different VRM or system implementations.

# 2. Module Requirements

The VRM 8.4 interface should be mechanically compatible with Intel's Voltage Regulator Module Header 8, revision 3.0. For additional voltage regulator module, connector, and header dimensions, see *VRM 8.1 DC-DC Converter Design Guidelines*, available from the Intel Pentium<sup>®</sup> II Processor developers' web site: http://developer.intel.com/design/PentiumII/applnots/243408.htm.

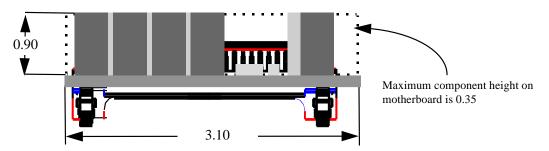

• Dimensions EXPECTED

Outline dimensions should be equal to or less than 3.1" x 1.5" x 1.1". Maximum component height should be 0.90" on the connector side and 0.14" on the backside of the module.

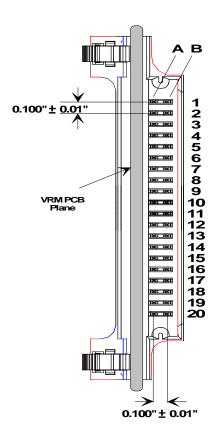

• Interconnect EXPECTED

Interconnect should consist of a 40 pin interface, type AMPMOD2 or equivalent, with the socket (part number 532956-7 or equivalent) mounted to the module. The current capacity must be at least 2A/pin. The pin electrical interface should be as given in Table 4.

Table 4, Module Pinout

| Pin# | Row A               | Row B               |

|------|---------------------|---------------------|

| 1    | 5Vin                | 5Vin                |

| 2    | 5Vin                | 5Vin                |

| 3    | 5Vin                | 5Vin                |

| 4    | 12Vin               | 12Vin               |

| 5    | 12Vin               | Reserved            |

| 6    | Ishare              | OUTEN               |

| 7    | VID0                | VID1                |

| 8    | VID2                | VID3                |

| 9    | VID4                | PWRGD               |

| 10   | Vcc <sub>CORE</sub> | Vss                 |

| 11   | Vss                 | Vcc <sub>CORE</sub> |

| 12   | Vcc <sub>CORE</sub> | Vss                 |

| 13   | Vss                 | Vcc <sub>CORE</sub> |

| 14   | Vcc <sub>CORE</sub> | Vss                 |

| 15   | Vss                 | Vcc <sub>CORE</sub> |

| 16   | Vcc <sub>CORE</sub> | Vss                 |

| 17   | Vss                 | Vcc <sub>CORE</sub> |

| 18   | Vcc <sub>CORE</sub> | Vss                 |

| 19   | Vss                 | Vcc <sub>CORE</sub> |

| 20   | Vcc <sub>CORE</sub> | Vss                 |

Figure 2, Pin Orientation

#### Mating header (reference)

The VRM 8.4 Header is a 40-position, two-row, shrouded header with straight posts on 0.1 inch centers (ref. AMP # 146315-1 or equivalent). The module is retained to and removed from the header by features on the header that mate with the voltage regulator module. The removal and installation process must not require the use of tools. The removal features must be accessible from the backside (opposite the receptacle) of the module. (ref. Figure 2).

Weight

EXPECTED

Package weight, including any integral heat sink, should be less than three ounces.

Marking

EXPECTED

The input voltage (+3.3VDC, +5VDC or +12VDC) should be conspicuously marked on the module, to be visible during insertion of the module into the header. Marking options include:

- Color-code the text on the label: yellow = +3.3V; red = +5V; blue = +12V.

- List the output voltage range and input and output currents.

Figure 3, Module Top View

(dimensions in inches)

# 3. Tests and Standards

**PROPOSED**

# 3.1 Reliability

The VRM should be designed to function to electrical specifications, within the environmental specifications, with 60°C air at a velocity of 100 LFM directed along the connector axis.

## Component De-rating

The following component de-rating guidelines should be followed:

- Semiconductor junction temperatures should be < 115°C with ambient at 50°C.

- Capacitor case temperature should not exceed 80 % of rated temperature.

- Resistor wattage de-rating should be consistent with the resistor type.

- Component voltage and current de-rating should be > 20%, the effects of ripple current heating should be accounted for in this de-rating.

#### Mean-Time-Between-Failures (MTBF)

Design, including materials, should be consistent with the manufacture of units with an MTBF of 500,000 hours of continuous operation at 55°C, maximum-outputs load, and worst-case line, while meeting specified requirements. MTBF should be calculated in accordance with MIL-STD-217F (parts stress method).

## 3.2 Environmental

Design, including materials, should be consistent with the manufacture of units that meet the environmental reference points in Table 5.

**Table 5, Environmental Specifications**

|               | Operating                                                 | Non-Operating               |

|---------------|-----------------------------------------------------------|-----------------------------|

| Temperature   | Ambient 0°C to +60°C at full load with a maximum          | Ambient –40°C to 70°C with  |

|               | rate of change of 5°C/10 minutes minimum but no           | a maximum rate of change of |

|               | more than 10°C/hour. 1                                    | 20°C/hour. <sup>2</sup>     |

| Humidity      | To 85% relative humidity.                                 | To 95% relative humidity.   |

| Altitude      | 0 to 10,000 feet                                          | 0 to 50,000 feet.           |

| Electrostatic | 15 KV initialization level. The direct ESD event          | 25 KV initialization level. |

| discharge     | shall cause no out-of-regulation conditions. <sup>3</sup> |                             |

<sup>&</sup>lt;sup>1</sup> See Section 1.1 for static and transient test conditions.

## 3.3 Shock and Vibration

The VRM should not be damaged and the interconnect integrity not compromised during:

- A shock of 50G with an 11 millisecond half sine wave, non-operating, the shock to be applied in each of the orthogonal axes.

- Vibration of 0.01G<sup>2</sup> per Hz at 5 Hz, sloping to 0.02G<sup>2</sup> per Hz at 20 Hz and maintaining 0.02G<sup>2</sup> per Hz from 20 Hz to 500 Hz, non-operating, applied in each of the orthogonal axes.

## 3.4 Electromagnetic

Design, including materials, should be consistent with the manufacture of units that comply with the limits of FCC Class B and VDE 243 Level B for radiated emissions, given the existence of an external package around the VRM with 20dB of shielding.

# 3.5 Safety

Design, including materials, should be consistent with the manufacture of units that meet the standards of UL flammability specifications per 94V-0.

<sup>&</sup>lt;sup>2</sup> Thermal shock of –40°C to +70°C, 10 cycles; transfer time shall not exceed 5 minutes, duration of exposure to temperature extremes shall be 20 minutes.

<sup>&</sup>lt;sup>3</sup> Includes overshoot, undershoot, and nuisance trips of the over-voltage protection, over-current protection or remote shutdown circuitry.