# intel®

# Intel XScale® Microarchitecture Programmer Model for Big Endian

**Application Note**

June 2001

Order Number: 278402-001

# intel

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

This document and the software described in it are furnished under license and may only be used or copied in accordance with the terms of the license. The information in this document is furnished for informational use only, is subject to change without notice, and should not be construed as a commitment by Intel Corporation. Intel Corporation assumes no responsibility or liability for any errors or inaccuracies that may appear in this document or any software that may be provided in association with this document. Except as permitted by such license, no part of this document may be reproduced, stored in a retrieval system, or transmitted in any form or by any means without the express written consent of Intel Corporation.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 2001

Intel and Intel XScale are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries. \*Other names and brands may be claimed as the property of others.

# int<sub>el</sub>。 Contents

| 1.0 | Intro | duction |                        | 5  |

|-----|-------|---------|------------------------|----|

| 2.0 | Endi  | an Conf | figuration             | 6  |

| 3.0 | Data  | transfe | r                      | 6  |

|     | 3.1   | Word    | Accesses               | 7  |

|     |       |         | Word Load (LDR)        |    |

|     |       | 3.1.2   | Word Store (STR)       | 8  |

|     |       | 3.1.3   | Word Swap (SWP)        | 9  |

|     | 3.2   | Half-W  | Vord Access            | 10 |

|     |       |         | Half Word Load (LDRH)  |    |

|     |       | 3.2.2   | Half Word Store (STRH) | 11 |

|     | 3.3   | Byte A  | ACCESS                 | 12 |

|     |       | 3.3.1   | Byte Load (LDRB)       | 12 |

|     |       | 3.3.2   | Byte Store (STRB)      |    |

|     |       | 3.3.3   | Byte Swap (SWPB)       |    |

|     | 3.4   | Endiar  | nness Test Code        |    |

# **Figures**

| 1 | Big Endian Byte, Half Word, and Word Memory Mapping    | .5 |

|---|--------------------------------------------------------|----|

| 2 | Little Endian Byte, Half Word, and Word Memory Mapping | .6 |

# intel®

# 1.0 Introduction

This document describes the configuration and behavior of the Intel XScale<sup>®</sup> Microarchitecture in big endian mode. The memory data transfer instruction sets being discussed are load, store, and swap in word, half word and byte with aligned and unaligned access. Section 3.4, "Endianness Test Code" on page 14 is an example code for system endianness testing.

Intel XScale<sup>®</sup> Microarchitecture has the option to operate in either little or big endian mode. This refers to the way how the memory is being accessed. Big endian byte ordering assigns the lowest byte address to the most significant byte of a 32-bit memory word, where the little endian byte order is the reverse. For an example, a decimal word of 1025 is represented as

#### 0000000 0000000 00000100 0000001

This is represented in the different modes:

• Big Endian

| -             | 31       | 24 | 23        | 16 | 15       | 8 | 7        | 0 |

|---------------|----------|----|-----------|----|----------|---|----------|---|

|               | 0000001  |    | 00000100  |    | 00000000 |   | 00000000 |   |

| Little Endian |          |    |           |    |          |   |          |   |

|               | 31       | 24 | 23        | 16 | 15       | 8 | 7        | 0 |

|               | 00000000 |    | 000000000 |    | 00000100 |   | 00000001 |   |

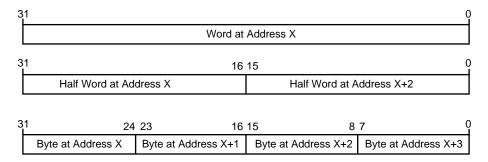

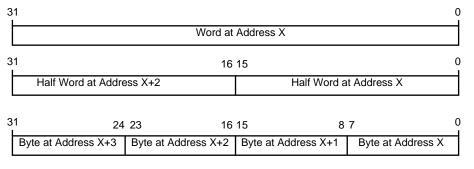

Figures 1 and 2 show memory mapping for big and little endian modes respectivly. Both of these figures assume that address X is word aligned.

#### Figure 1. Big Endian Byte, Half Word, and Word Memory Mapping

A8989-01

#### Figure 2. Little Endian Byte, Half Word, and Word Memory Mapping

A9005-01

# 2.0 Endian Configuration

The big and little endian modes are controlled by the B-bit of the Control Register (Coprocessor 15, register1, bit 7). The default mode at reset is little endian. To enable the big endian mode, the B bit must be set before performing any sub-word accesses to memory, or undefined results would occur. The bit takes effect even if the MMU is disabled. The following is assembly code to enable B-bit.

MACRO BIGENDIAN MRC p15,0,al,cl,c0,0 ORR al,al,#0x80 ;set bit7 of register1 cp15 MCR p15,0,al,cl,c0,0 ENDM

The application code built to run on the system must be compiled to match the endianness. To produce the object code which is targeted for big endian system, the compiler must be specified to work in big endian mode. For example, *-mbig-endian* switch must be specified for GNU CC because the default is in little endian. For GNUPro assembler, *-EB* switch would assemble the code for big endian. The library being used must have been compiled in the big endian mode.

# 3.0 Data transfer

This section describes the behavior of the Big Endian Intel XScale<sup>®</sup> Microarchitecture in data transfer instructions.

# 3.1 Word Accesses

in

The endianness applies when byte or half-word accesses are made to memory. For a 32-bit word memory access, the bit pattern in the memory must match the bit pattern in the processor register, regardless if the system is big or little endian.

## 3.1.1 Word Load (LDR)

If the address is not word aligned, the loaded value is rotated right by 8 times the value of bits[1:0] of the address.

| Registers                                                                                             | Memory<br>location | Byte 0 | Byte1 | Byte 2 | Byte 3 |

|-------------------------------------------------------------------------------------------------------|--------------------|--------|-------|--------|--------|

| <ul> <li>r4 = 0x0</li> <li>r5 = 0x0</li> <li>r6 = 0x0</li> <li>r7 = 0x0</li> <li>r10 = 0x0</li> </ul> | 0x0                | AA     | ВВ    | сс     | DD     |

Before code execution:

#### Code segment:

| LDR r4, [r10]     | ; word load in aligned access                      |  |

|-------------------|----------------------------------------------------|--|

| LDR r5, [r10, #1] | ; word load in unaligned access with 1 byte offset |  |

| LDR r6, [r10, #2] | ; word load in unaligned access with 2 byte offset |  |

| LDR r7, [r10, #3] | ; word load in unaligned access with 3 byte offset |  |

| Registers                                                                                                                         | Memory<br>location | Byte 0 | Byte1 | Byte 2 | Byte 3 |

|-----------------------------------------------------------------------------------------------------------------------------------|--------------------|--------|-------|--------|--------|

| <ul> <li>r4 = 0xAABBCCDD</li> <li>r5 = 0xDDAABBCC</li> <li>r6 = 0xCCDDAABB</li> <li>r7 = 0xBBCCDDAA</li> <li>r10 = 0x0</li> </ul> | 0x0                | AA     | BB    | сс     | DD     |

## 3.1.2 Word Store (STR)

In unaligned access, STR instruction ignores the least significant two bits of address.

Before code execution:

| Registers                                        | Memory<br>location | Byte 0 | Byte1 | Byte 2 | Byte 3 |

|--------------------------------------------------|--------------------|--------|-------|--------|--------|

| • r4 = 0xAABBCCDD                                | 0x0                | 00     | 00    | 00     | 00     |

| <ul> <li>r10 = 0x0</li> <li>r11 = 0x4</li> </ul> | 0x4                | 00     | 00    | 00     | 00     |

Code segment:

| STR r4, [r10]     | ;word store in aligned access   |

|-------------------|---------------------------------|

| STR r4, [r11, #1] | ;word store in unaligned access |

| Registers                                        | Memory<br>location | Byte 0 | Byte1 | Byte 2 | Byte 3 |

|--------------------------------------------------|--------------------|--------|-------|--------|--------|

| • r4 = 0xAABBCCDD                                | 0x0                | AA     | BB    | СС     | DD     |

| <ul> <li>r10 = 0x0</li> <li>r11 = 0x4</li> </ul> | 0x4                | AA     | BB    | СС     | DD     |

# 3.1.3 Word Swap (SWP)

intel

A SWP instruction performs the load and store operation. If the address is not word aligned, the loaded value is rotated right by 8 times the bits [1:0] of the address. The stored value is not rotated.

Before code execution:

| Registers                                                                 | Memory<br>location | Byte 0 | Byte1 | Byte 2 | Byte 3 |

|---------------------------------------------------------------------------|--------------------|--------|-------|--------|--------|

| • r4 = 0x11223344                                                         | 0x0                | AA     | BB    | СС     | DD     |

| <ul> <li>r5 = 0x55667788</li> <li>r10 = 0x0</li> <li>r11 = 0x4</li> </ul> | 0x4                | EE     | FF    | 00     | 99     |

Code segment:

SWP r4, r4, [r10] ; word swap in aligned access SWP r5, r5, [r11, #1] ; word swap in unaligned access with 1 byte offset

| Registers                                                                 | Memory<br>location | Byte 0 | Byte1 | Byte 2 | Byte 3 |

|---------------------------------------------------------------------------|--------------------|--------|-------|--------|--------|

| • r4 = 0xAABBCCDD                                                         | 0x0                | 11     | 22    | 33     | 44     |

| <ul> <li>r5 = 0x99EEFF00</li> <li>r10 = 0x0</li> <li>r11 = 0x4</li> </ul> | 0x4                | 55     | 66    | 77     | 88     |

# 3.2 Half-Word Access

## 3.2.1 Half Word Load (LDRH)

The loaded half word is zero-extended to a 32-bit word for half word aligned memory address. For non half word aligned memory address, the loaded value is unpredictable.

Before code execution:

| Registers                                                                                             | Memory<br>location | Byte 0 | Byte1 | Byte 2 | Byte 3 |

|-------------------------------------------------------------------------------------------------------|--------------------|--------|-------|--------|--------|

| <ul> <li>r4 = 0x0</li> <li>r5 = 0x0</li> <li>r6 = 0x0</li> <li>r7 = 0x0</li> <li>r10 = 0x0</li> </ul> | 0x0                | AA     | BB    | сс     | DD     |

Code segment:

| LDRH r4, [r10]     | ; half word load in aligned access   |

|--------------------|--------------------------------------|

| LDRH r5, [r10, #1] | ; half word load in unaligned access |

| LDRH r6, [r10, #2] | ; half word load in aligned access   |

| LDRH r7, [r10, #3] | ; half word load in unaligned access |

After code execution:

| Registers <sup>a</sup>                                                                                                        | Memory<br>location | Byte 0 | Byte1 | Byte 2 | Byte 3 |

|-------------------------------------------------------------------------------------------------------------------------------|--------------------|--------|-------|--------|--------|

| <ul> <li>r4 = 0x0000AABB</li> <li>r5 = 0xXXXXXX</li> <li>r6 = 0x0000CCDD</li> <li>r7 = 0xXXXXXX</li> <li>r10 = 0x0</li> </ul> | 0x0                | AA     | BB    | сс     | DD     |

a. XX means unpredictable

# 3.2.2 Half Word Store (STRH)

An unaligned half word memory access would cause the stored value to be unpredictable.

Before code execution:

| Registers                                        | Memory<br>location | Byte 0 | Byte1 | Byte 2 | Byte 3 |

|--------------------------------------------------|--------------------|--------|-------|--------|--------|

| • r4 = 0xAABBCCDD                                | 0x0                | 00     | 00    | 00     | 00     |

| <ul> <li>r10 = 0x0</li> <li>r11 = 0x4</li> </ul> | 0x4                | 00     | 00    | 00     | 00     |

| • r12 =0x8                                       | 0x8                | 00     | 00    | 00     | 00     |

Code segment:

| STRH r4, [r10]     | ; | halfword store in aligned access   |  |

|--------------------|---|------------------------------------|--|

| STRH r4, [r11, #1] | ; | halfword store in unaligned access |  |

STRH r4, [r12, #2]

; halfword store in aligned access

| Registers                                        | Memory<br>location | Byte 0 | Byte1 | Byte 2 | Byte 3 |

|--------------------------------------------------|--------------------|--------|-------|--------|--------|

| • r4 = 0xAABBCCDD                                | 0x0                | СС     | DD    | 00     | 00     |

| <ul> <li>r10 = 0x0</li> <li>r11 = 0x4</li> </ul> | 0x4                | ХХ     | XX    | ХХ     | ХХ     |

| • r12 = 0x8                                      | 0x8                | 00     | 00    | СС     | DD     |

# **3.3 Byte Access**

## 3.3.1 Byte Load (LDRB)

The selected byte is placed at the [7:0] of the register and [31:8] of the register is zero extended.

Before code execution:

| Registers                                                                                          | Memory<br>location | Byte 0 | Byte1 | Byte 2 | Byte 3 |

|----------------------------------------------------------------------------------------------------|--------------------|--------|-------|--------|--------|

| <ul> <li>r4 =0x0</li> <li>r5 =0x0</li> <li>r6 = 0x0</li> <li>r7 =0x0</li> <li>r10 = 0x0</li> </ul> | 0x0                | AA     | BB    | сс     | DD     |

Code segment:

| LDRB r4, [r10]     | ; byte load in aligned access                      |

|--------------------|----------------------------------------------------|

| LDRB r5, [r10, #1] | ; byte load in unaligned access with 1 byte offset |

| LDRB r6, [r10, #2] | ; byte load in unaligned access with 2 byte offset |

| LDRB r7, [r10, #3] | ; byte load in unaligned access with 3 byte offset |

| Registers                                                                                                                       | Memory<br>location | Byte 0 | Byte1 | Byte 2 | Byte 3 |

|---------------------------------------------------------------------------------------------------------------------------------|--------------------|--------|-------|--------|--------|

| <ul> <li>r4 =0x000000AA</li> <li>r5 = 0x000000BB</li> <li>r6 = 0x000000CC</li> <li>r7 = 0x00000DD</li> <li>r10 = 0x0</li> </ul> | 0x0                | AA     | BB    | сс     | DD     |

# 3.3.2 Byte Store (STRB)

intel

Before code execution:

| Registers                                                                                                     | Memory<br>location | Byte 0 | Byte1 | Byte 2 | Byte 3 |

|---------------------------------------------------------------------------------------------------------------|--------------------|--------|-------|--------|--------|

|                                                                                                               | 0x0                | 00     | 00    | 00     | 00     |

| <ul> <li>r4 = 0xAABBCCDD</li> <li>r8 = 0x0</li> <li>r9 = 0x4</li> <li>r10 = 0x8</li> <li>r11 = 0xA</li> </ul> | 0x4                | 00     | 00    | 00     | 00     |

|                                                                                                               | 0x8                | 00     | 00    | 00     | 00     |

|                                                                                                               | 0xA                | 00     | 00    | 00     | 00     |

|                                                                                                               | 0x0                | 00     | 00    | 00     | 00     |

Code segment:

STRB r4, [r8,#0] STRB r4, [r9, #1] STRB r4, [r10, #2] STRB r4, [r11, #3]

| Registers                                                                                                     | Memory<br>location | Byte 0 | Byte1 | Byte 2 | Byte 3 |

|---------------------------------------------------------------------------------------------------------------|--------------------|--------|-------|--------|--------|

|                                                                                                               | 0x0                | DD     | 00    | 00     | 00     |

| <ul> <li>r4 = 0xAABBCCDD</li> <li>r8 = 0x0</li> <li>r9 = 0x4</li> <li>r10 = 0x8</li> <li>r11 = 0xA</li> </ul> | 0x4                | 00     | DD    | 00     | 00     |

|                                                                                                               | 0x8                | 00     | 00    | DD     | 00     |

|                                                                                                               | 0xA                | 00     | 00    | 00     | DD     |

|                                                                                                               | 0x0                | DD     | 00    | 00     | 00     |

### 3.3.3 Byte Swap (SWPB)

A SWPB instruction works as the LDRB and STRB.

Before code execution:

| Registers                                              | Memory<br>location | Byte 0 | Byte1 | Byte 2 | Byte 3 |

|--------------------------------------------------------|--------------------|--------|-------|--------|--------|

| <ul> <li>r4 = 0x11223344</li> <li>r10 = 0x0</li> </ul> | 0x0                | AA     | BB    | СС     | DD     |

Code segment:

SWPB r4, r4, [r10] ;byte swap

After code execution:

| Registers                                              | Memory<br>location | Byte 0 | Byte1 | Byte 2 | Byte 3 |

|--------------------------------------------------------|--------------------|--------|-------|--------|--------|

| <ul> <li>r4 = 0x112233AA</li> <li>r10 = 0x0</li> </ul> | 0x0                | 44     | BB    | СС     | DD     |

# 3.4 Endianness Test Code

The following is simple C code to test the endianness of the system.

This code would place character AB or ABCD in the memory array. Pointer is used to read back the memory array. A big endian system would return the characters as the same byte order, where the little endian system would return the characters in reverse order.

```

/* This program store a value of Return value of 1 if the byte for int is neither 2 or 4 bytes, OR neither little or big endian*/ \!\!\!

```

```

#include <stdio.h>

static int w[1];

static char * bytes;

int main(void)

{

printf ("This is an Endianness test:\n");

if (sizeof (int) == 2)

{

w[0] = 0x4142;

bytes = (char *) w;

if (strcmp(bytes, "AB") == 0)

printf ("big endian\n");

```

# Intel XScale<sup>®</sup> Microarchitecture Programmer Model for Big Endian

# intel®

```

else if (strcmp(bytes, "BA") == 0)

printf ("little endian\n");

else

{

printf ("Not big nor little endian\n");

return 1;

}

}

else if (sizeof (int) == 4)

{

w[0] = 0x41424344;

bytes = (char *) w;

if (strcmp(bytes, "ABCD") == 0)

printf ("big endian\n");

else if (strcmp(bytes, "DCBA") == 0)

printf ("little endian\n");

else

{

printf ("Not big nor little endian\n");

return 1;

}

}

else

{

printf ("unexpected size of int\n");

return 1;

}

return 0;

```