# Intel® 413808 and Intel® 413812 I/O Controllers

**Design Guide**

May 2007

Order Number: 315055-002US

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or by visiting Intel's Web Site.

[When the doc contains software source code, include a copy of the software license or a hyperlink to its permanent location.]

Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families. See http://www.intel.com/products/processor\_number for details.

Code Names are only for use by Intel to identify products, platforms, programs, services, etc. ("products") in development by Intel that have not been made commercially available to the public, i.e., announced, launched or shipped. They are never to be used as "commercial" names for products. Also, they are not intended to function as trademarks.

BunnyPeople, Celeron, Celeron Inside, Centrino, Centrino logo, Core Inside, FlashFile, i960, InstantIP, Intel, Intel logo, Intel386, Intel486, Intel740, IntelDX2, IntelDX4, IntelSX2, Intel Core, Intel Inside, Intel Inside logo, Intel. Leap ahead., Intel. Leap ahead. logo, Intel NetBurst, Intel NetMerge, Intel NetStructure, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel Viiv, Intel vPro, Intel XScale, Itanium, Itanium Inside, MCS, MMX, Oplus, OverDrive, PDCharm, Pentium, Pentium Inside, skoool, Sound Mark, The Journey Inside, VTune, Xeon, and Xeon Inside are trademarks of Intel Corporation in the U.S. and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2007, Intel Corporation. All rights reserved.

## Contents

| 1.0 | Introduction81.1About This Document.81.2About the Intel® 413808 and Intel® 413812 I/O Controllers9                                                                                                                                                                                                                                                                                                                                                   |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.0 | Package Information122.1Package Introduction12                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3.0 | Board Layout Guidelines163.1Motherboard Stack Up Information163.2Adapter Card Topology183.3PCB Impedance Targets19                                                                                                                                                                                                                                                                                                                                   |

| 4.0 | PCI-X Layout Guidelines224.1PCI/PCI-X Frequency Selection224.2PCI-X Layout Recommendations234.2.1PCI-X Clock Routing234.2.2133 MHz One Slot Topology244.2.3Embedded 133 MHz Topology254.2.4Mixed 133 MHz Topology264.2.5100 MHz Two Slot Topology274.2.6Embedded 100 MHz Topology284.2.7Mixed 100 MHz Topology294.2.866 MHz PCIX Four Slot Topology304.2.9Embedded 66 MHz Topology314.2.10Mixed 66 MHz Topology324.2.11Additional PCI Layout Notes33 |

| 5.0 | PCI Express Layout.       34         5.1       Optional PCI Express Lane Reversal       35         5.2       PCI Express Layout recommendations       36         5.2.1       PCI Express Motherboard Layout Guidelines       36         5.2.2       PCI Express Layout Motherboard-Adapter Card Guidelines       37         5.2.3       Clock Routing Guidelines       39                                                                            |

| 6.0 | SATA/SAS Bus Layout                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 7.0 | Peripheral Local Bus467.1Peripheral Bus Signals467.2PBI Bus Width467.3Flash Memory Support477.4PBI Topology Layout Guidelines47                                                                                                                                                                                                                                                                                                                      |

| 8.0 | Power Delivery528.1Power Plane Layout528.2Decoupling Recommendations568.3Power Sequencing56                                                                                                                                                                                                                                                                                                                                                          |

| 9.0 | Debug and Test589.1PCI-X Debugging589.2PCI Express Debugging589.2.1Physical Layer Debugging589.2.2Data Link and Transaction Layer Testing599.2.3PCI Express Analyzer/Exercisers599.2.4Mid-bus Probing59                                                                                                                                                                                                                                              |

|      | 9.3   | SAS Debugging                                                                | 59 |

|------|-------|------------------------------------------------------------------------------|----|

|      | 9.4   | SAS Debugging                                                                | 59 |

| 10.0 | Ther  | nal Solutions                                                                | 50 |

| 11.0 | Term  | inations                                                                     | 52 |

|      | 11.1  | Important Design and Debug Requirements6                                     |    |

|      | 11.2  | Checklist Recommendations6                                                   |    |

|      | 11.3  | Reset Straps                                                                 | 59 |

|      | 11.4  | Analog Filters                                                               | 71 |

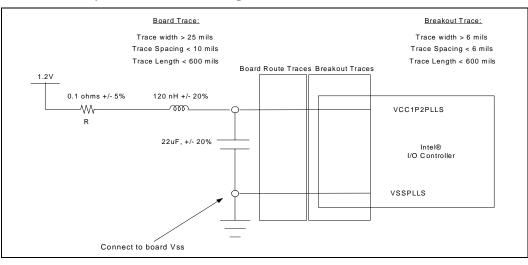

|      |       | 11.4.1 V <sub>CC1P2PLLS0</sub> , V <sub>CC1P2PLLS1</sub> Filter Requirements | 71 |

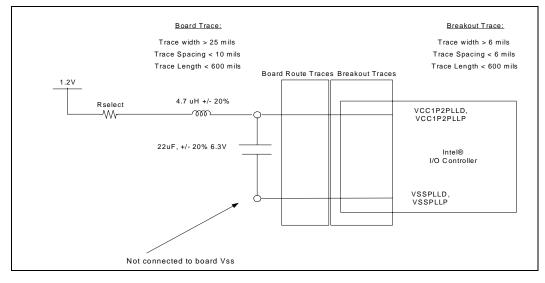

|      |       | 11.4.2 V <sub>CC1P2PLLP</sub> , V <sub>CC1P2PLLD</sub> Filter Requirements   | 73 |

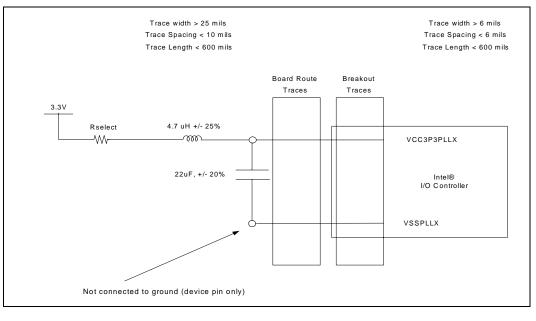

|      |       | 11.4.3 V <sub>CC3P3PLLX</sub> PLL Requirements                               | 74 |

|      | 11.5  | PCI Resistor Calibration                                                     |    |

|      | 11.6  | PCI Express Resistor Compensation                                            | 77 |

| 12.0 | Layou | ut Checklist٤                                                                | 30 |

|      | 12.1  | Layout Checklist                                                             | 30 |

| 13.0 | Refer | rences                                                                       | Э2 |

|      | 13.1  | Relevant Documents                                                           | 92 |

|      | 13.2  | Electronic Information                                                       | ЭЗ |

| Α    | Арре  | ndix                                                                         | 94 |

|      | A.1   | Terminology                                                                  | 94 |

|      | A.2   | Simulation Conditions                                                        |    |

|      |       |                                                                              |    |

## Figures

| 1  | Dual Core Processor                                                                |

|----|------------------------------------------------------------------------------------|

| 2  | Intel® 413808 and Intel® 413812 I/O Controllers 1357-ball FCBGA Package Diagram 13 |

| 3  | Top View Ball Map With Interfaces14                                                |

| 4  | Motherboard Stackup Recommendations17                                              |

| 5  | Adapter Card Stackup                                                               |

| 6  | P_PCIXCAP Layout Guidelines                                                        |

| 7  | 133 MHz One Slot Topology25                                                        |

| 8  | Embedded 133 MHz Topology26                                                        |

| 9  | Mixed 133 MHz Topology 27                                                          |

| 10 | 100 MHz Dual Slot Topology                                                         |

| 11 | Embedded 100 MHz Topology29                                                        |

| 12 | Mixed 100 MHz Topology                                                             |

| 13 | 66 MHz Four Slot Topology                                                          |

| 14 | Embedded 66 MHz Topology32                                                         |

| 15 | Mixed 66 MHz Topology                                                              |

| 16 | PCI Express Lane Reversal To Improve PCB Routing35                                 |

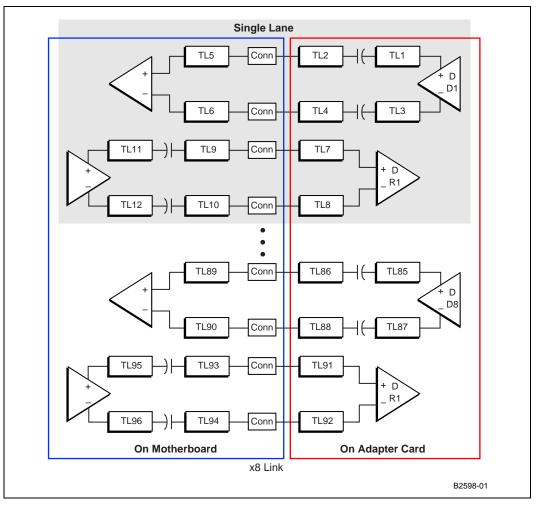

| 17 | Motherboard Topology                                                               |

| 18 | Motherboard-Adapter Card Topology                                                  |

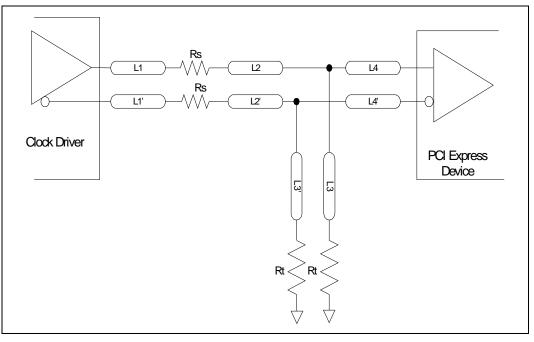

| 19 | PCI Express Clock Routing Topology40                                               |

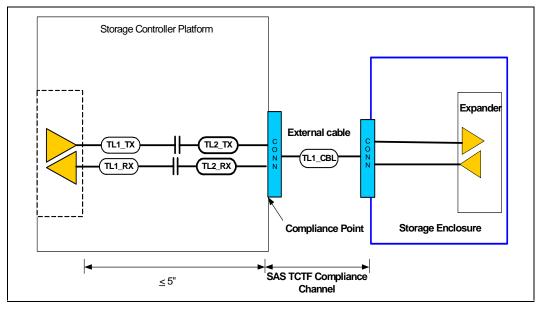

| 20 | SAS Inter-enclosure Topology43                                                     |

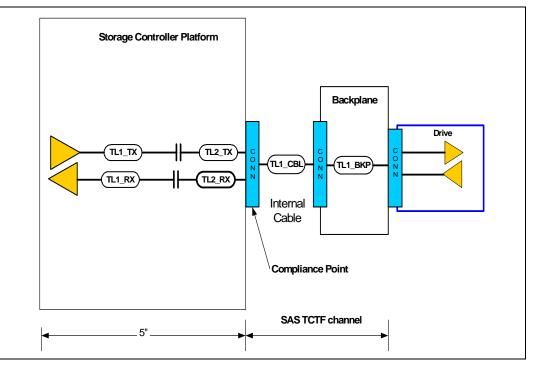

| 21 | SAS Intra-enclosure Topology44                                                     |

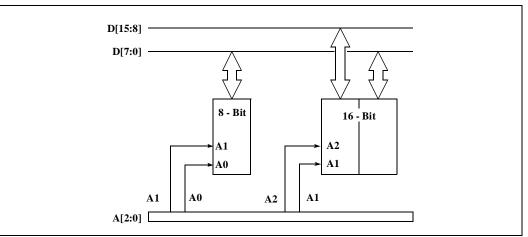

| 22 | Data Width and Low Order Address Lines46                                           |

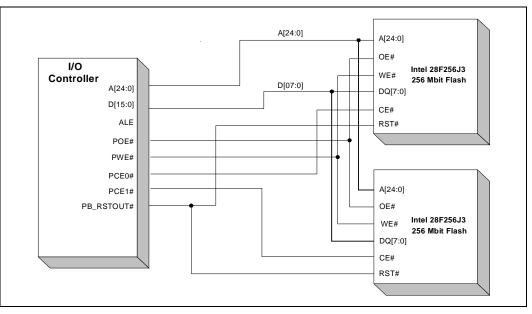

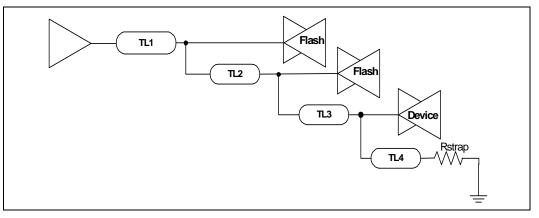

| 23 | Sixty-Four Mbyte Flash Memory System                                               |

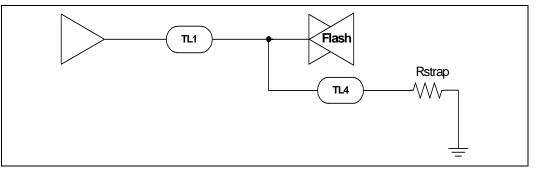

| 24 | Peripheral Bus Single Load Topology48                                              |

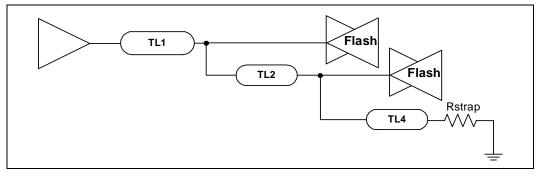

| 25 | Peripheral Bus Dual Load Topology                                                  |

| 26 | Peripheral Bus Three Load Topology50                                               |

| 27 | Split Voltage Planes for Layer 3 (Top View)54                                      |

| 28 | Split Voltage Planes for Layer 4 (Top View)54                                      |

| 29 | Split Voltage Planes for Layer 6 (Top View)55                                      |

| 30 | Split Voltage Planes for Layer 8 (Top View)55                                      |

| 31 | VCC1P2PLLS0, VCC1P2PLLS1 Configuration73                                           |

| 32 | VCC1P2PLLD, VCC1P2PLL Lowpass Filter Configuration74                               |

| 33 | VCC3P3PLL Filter Configuration                                                     |

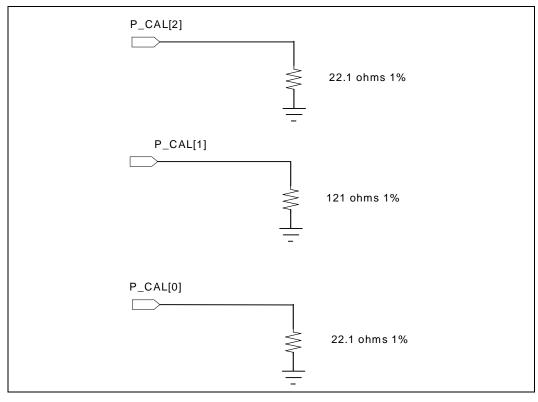

| 34 | PCI Resistor Calibration77                                                         |

| 35 | PCI Express RCOMP77                                                                |

| 36 | RBIAS[0], RBIAS_SENSE[0] Connections78                                             |

## Tables

| 1  | Motherboard Stack Up, Stripline and Microstrip16                     |

|----|----------------------------------------------------------------------|

| 2  | Adapter Card Stack Up, Microstrip and Stripline                      |

| 3  | Single-ended Trace Parameters                                        |

| 4  | Differential Trace Dimensions                                        |

| 5  | PCI-X Initialization Pattern                                         |

| 6  | PCI-X Clock Layout Guidelines                                        |

| 7  | PCI-X REQ#/GNT# Layout Guidelines                                    |

| 8  | 133 MHz Single-Slot Topology                                         |

| 9  | Embedded 133 MHz Topology                                            |

| 10 | Mixed 133 MHz Topology                                               |

| 11 | 100 MHz Two Slot Topology                                            |

| 12 | Embedded 100 MHz Topology                                            |

| 13 | Mixed 100 MHz Topology                                               |

| 14 | 66 MHz Four Slot Topology                                            |

| 15 | Embedded 66 MHz Topology                                             |

| 16 | Mixed 66 MHz Topology                                                |

| 17 | PCI Express Layout for a Motherboard                                 |

| 18 | PCI Express Layout for Motherboard-Adapter Card Topology             |

| 19 | PCI Express Layout for Clock Routing41                               |

| 20 | SAS Compliant Guidelines                                             |

| 21 | Interpair (Between Pair) Spacing Requirements45                      |

| 22 | PBI Routing Guideline Single Load48                                  |

| 23 | PBI Routing Guidelines for Two Loads49                               |

| 24 | PBI Routing Guideline for Three Loads50                              |

| 25 | Supply Voltages                                                      |

| 26 | Customer Reference Board Voltage Planes53                            |

| 27 | Customer Reference Board Layer Stackup53                             |

| 28 | Decoupling Recommendations                                           |

| 29 | Design and Debug Checklist62                                         |

| 30 | Terminations: Pull-up/Pull-down63                                    |

| 31 | Reset Straps                                                         |

| 32 | PCI Express/PCI-X Strap Configuration Table71                        |

| 33 | Required PLLs                                                        |

| 34 | V <sub>CC1P2PLLS0</sub> , V <sub>CC1P2PLLS1</sub> Layout Guideline72 |

| 35 | V <sub>CC1P2PILP</sub> , V <sub>CC1P2PILD</sub> , Layout Guideline   |

| 36 | V <sub>CC3P3PLL</sub> Layout Guideline                               |

| 37 | Layout Checklist                                                     |

| 38 | Design References                                                    |

| 39 | Intel Related Documentation                                          |

| 40 | Electronic Information                                               |

| 41 | Terminology and Definitions                                          |

## **Revision History**

| Date           | Revision | Description                                                                       |  |

|----------------|----------|-----------------------------------------------------------------------------------|--|

| May 2007       | 002      | Updated product naming conventions and fixed links.<br>Converted to new template. |  |

| September 2006 | 001      | Initial release                                                                   |  |

## **1.0** Introduction

### **1.1** About This Document

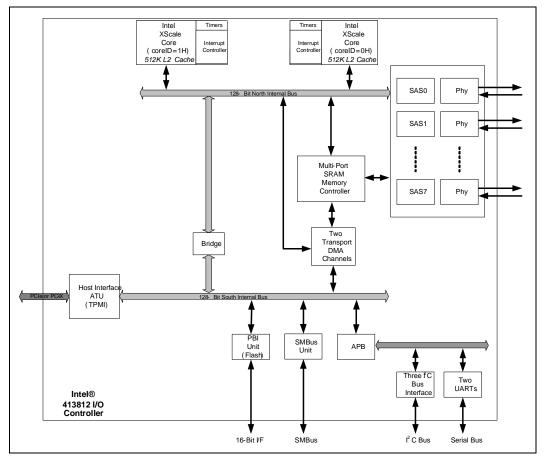

This document provides layout information and guidelines for designing platform or add-in board applications with Intel® 413808 and Intel® 413812 I/O Controllers (Figure 1). The Intel® 413808 I/O Controller is an 800 MHz controller and the Intel® 413812 I/O Controller is a 1200 MHz controller.

Intel recommends employing best-known design practices using board-level simulation, signal integrity testing and validation to create a robust design. Designers should note that this guide focuses on specific design considerations for this part and is not intended to be an all-inclusive list of good design practices. It is recommended that this guide is used in conjunction with empirical data to optimize your particular design.

The simulation conditions used for each of the interfaces are listed in Appendix A. The simulations were performed for motherboard and adapter card topologies. The impedance used for the motherboard is 50 ohm +/- 15% and the adapter card trace impedance is 60 ohm +/- 15%. These results are based on the six layer board stackup that is provided in Chapter 3.0.

#### **1.2 Document Details**

This document is partitioned into the following chapters:

- The top level block diagram and package dimensions are provided in Chapter 2.0, "Package Information".

- The example stackups for a motherboards and adapter cards are provided in Chapter 3.0, "Board Layout Guidelines".

- The layout guidelines external interfaces are listed in the following chapters: Chapter 4.0, "PCI-X Layout Guidelines", Chapter 5.0, "PCI Express Layout", Chapter 6.0, "SATA/SAS Bus Layout", and Chapter 7.0, "Peripheral Local Bus".

- The required terminations are listed in Chapter 11.0, "Terminations". This chapter also details the recommended filtering.

- The summary of the layout guidelines for each of the interfaces and the filters is listed in Chapter 12.0, "Layout Checklist".

- The details on power sequencing and decoupling recommendations are provided in Chapter 8.0, "Power Delivery".

- The details on our recommended heatsink solutions are listed in Chapter 10.0, "Thermal Solutions".

- The details on test equipment are listed in Chapter 9.0, "Debug and Test".

- The references are listed in Chapter 13.0, "References".

- The definitions and the simulation conditions (used for all the simulations described in this document) are provided in Appendix A.

Figure 1. Two Core I/O Controller

## 2.0 Package Information

## 2.1 Package Introduction

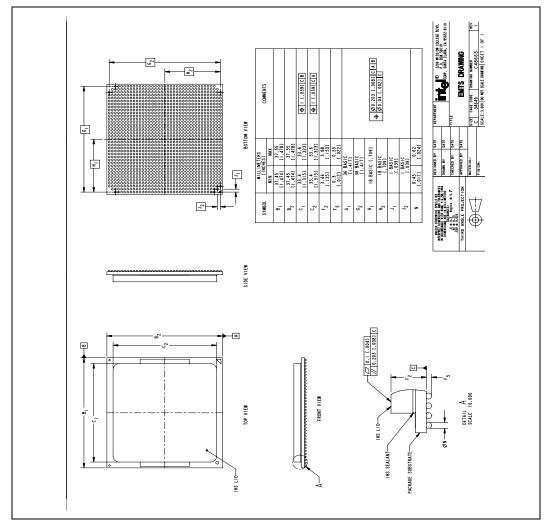

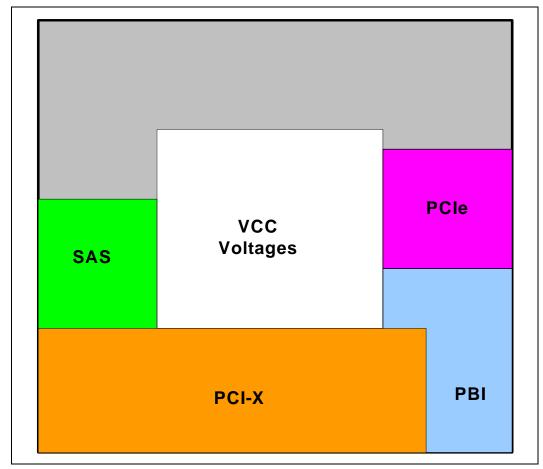

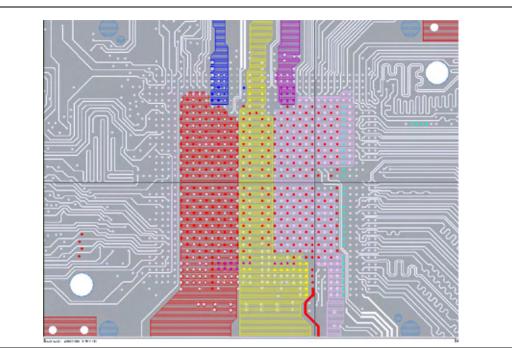

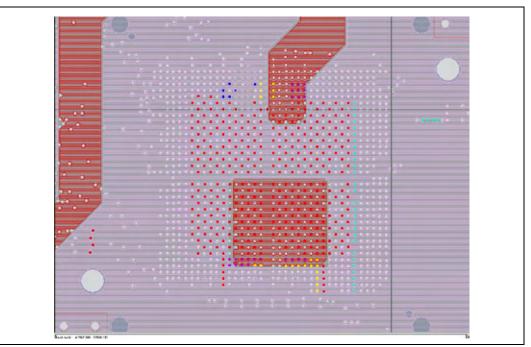

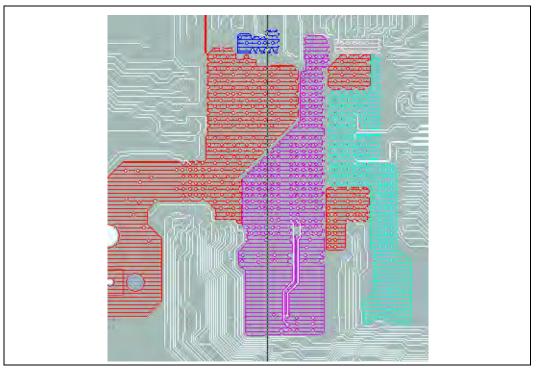

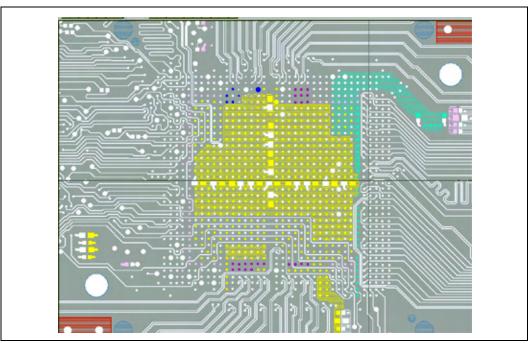

Intel® 413808 and Intel® 413812 I/O Controllers are offered in a 1357-ball FCBGA5 package. This package is shown in Figure 2. Figure 3 shows the top view of the package with the interfaces labeled and color coded. This figure is helpful during board layout. The signals are located on the FCBGA package to simplify signal routing and system implementation.

#### Figure 2. Intel® 413808 and Intel® 413812 I/O Controllers 1357-ball FCBGA Package Diagram

Figure 3. Top View Ball Map With Interfaces

## **3.0 Board Layout Guidelines**

This chapter provides an example of a motherboard and a adapter card stackup implementation. This stackup was used for all simulations listed in this design guide. It is highly recommended that signal integrity simulations be conducted to verify each PCB layout. This is especially true when the layout deviates from the recommendations listed in these design guidelines.

## 3.1 Motherboard Stack Up Information

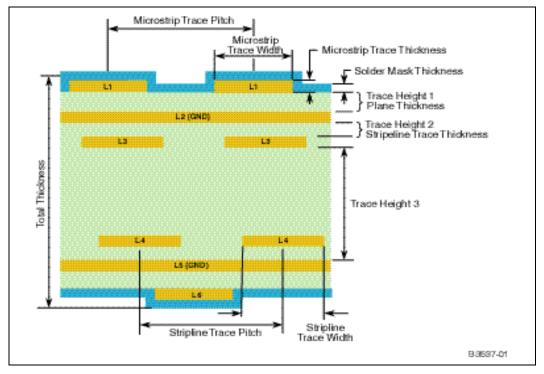

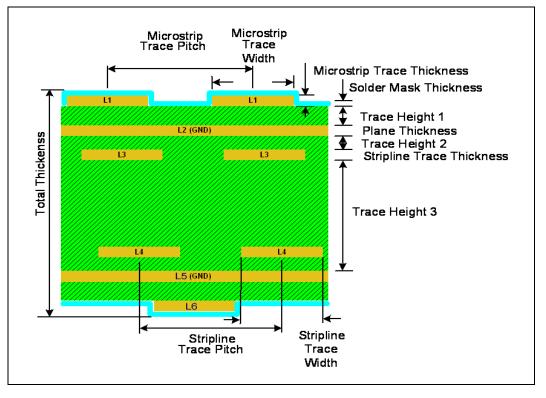

When the Intel® 413808 and Intel® 413812 I/O Controllers are used in server and workstation Raid On Mother Board (ROMB) applications, the motherboard is implemented on six layers. The specified impedance range for all board implementations is 500hms +/-15%. Adjustments are made for interfaces specified at other impedances. Table 1 defines the typical layer geometries for a six layer board.

The motherboard impedance guidelines are based on the typical server/workstation impedance for their processor and memory subsystem of 50-ohms. Dimensions and tolerances for the motherboard are listed in Table 1. Refer to Figure 4 for location of variables in Table 1.

| Variable                       | Туре        | Nominal | Minimum | Maximu<br>m | Notes                                                                                                                                                                                                                                                                                                          |

|--------------------------------|-------------|---------|---------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Solder Mask<br>Thickness (mil) | N/A         | 0.8     | 0.6     | 1.0         |                                                                                                                                                                                                                                                                                                                |

| Solder Mask E <mark>r</mark>   | N/A         | 3.65    | 3.65    | 3,65        |                                                                                                                                                                                                                                                                                                                |

| Core Thickness<br>(mil)        | N/A         | 9.8     | 9.6     | 10          |                                                                                                                                                                                                                                                                                                                |

| Core E <mark>r</mark>          | N/A         | 4.30    | 3.75    | 4.85        | 2113 material                                                                                                                                                                                                                                                                                                  |

| Plane Thickness                | Power       | 2.7     | 2.5     | 2.9         |                                                                                                                                                                                                                                                                                                                |

| (mil)                          | Ground      | 1.35    | 1.15    | 1.55        |                                                                                                                                                                                                                                                                                                                |

| Trace Height                   | 1           | 3.5     | 3,3     | 3,7         | The trace height is determined to achieve a nominal 50 ohms.                                                                                                                                                                                                                                                   |

| (mil)                          | 2           | 3.5     | 3,3     | 3.7         |                                                                                                                                                                                                                                                                                                                |

|                                | 3           | 10.5    | 9,9     | 11.1        |                                                                                                                                                                                                                                                                                                                |

|                                | Microstrip  | 4.30    | 3.75    | 4.85        |                                                                                                                                                                                                                                                                                                                |

| Preg E <mark>r</mark>          | Stripline 1 | 4.30    | 3.75    | 4.85        |                                                                                                                                                                                                                                                                                                                |

|                                | Stripline2  | 4.66    | 4.19    | 5.13        |                                                                                                                                                                                                                                                                                                                |

| Trace Thickness                | Microstrip  | 1.75    | 1.2     | 2.3         |                                                                                                                                                                                                                                                                                                                |

| (mil)                          | Stripline   | 1.4     | 1.2     | 1.6         |                                                                                                                                                                                                                                                                                                                |

| Trace Width (mil)              | Microstrip  | 5.0     | 3.5     | 6.5         |                                                                                                                                                                                                                                                                                                                |

|                                | Stripline   | 4.0     | 2.5     | 5.5         |                                                                                                                                                                                                                                                                                                                |

|                                | Microstrip  | 15.0    | -       | -           | Each interface sets the trace spacing based on its                                                                                                                                                                                                                                                             |

| Trace Spacing<br>(mil)         | Stripline   | 12.0    | -       | -           | signal integrity of differential impedance<br>requirements. For the purposes of the building the<br>transmission line models, it is assumed the artwork<br>is very accurate and therefore a constant. Thus, all<br>the variability in the trace spacing is the result of<br>the tolerances of the trace width. |

| Total Thickness<br>(mil)       | FR4         | 62.0    | 56.0    | 68.0        |                                                                                                                                                                                                                                                                                                                |

| Trace Velocity                 | Microstrip  |         | 135     | 141         | Velocity varies based on variation in Er. It cannot be                                                                                                                                                                                                                                                         |

| (ps/in)                        | Stripline   |         | 167     | 178         | controlled during the fab process.                                                                                                                                                                                                                                                                             |

| Trace Impedance                | Microstrip  | 50      | 42.5    | 57.5        |                                                                                                                                                                                                                                                                                                                |

| (ohms)                         | Stripline   | 50      | 45      | 55          |                                                                                                                                                                                                                                                                                                                |

#### Table 1. Motherboard Stack Up, Stripline and Microstrip

#### Figure 4. Motherboard Stackup Recommendations

## 3.2 Adapter Card Topology

Intel® 413808 and Intel® 413812 I/O Controllers are implemented on PCI Express or PCI-X adapter cards with six layers. The specified impedance range for all adapter card implementations is 60ohms +/-15%. Table 2 defines the typical layer geometries for a six layer board. Note that the values are the same as the motherboard stack up with the exception of the impedance.

| Variable                       | Туре       | Nominal | Minimum | Maximu<br>m | Notes                                                        |  |

|--------------------------------|------------|---------|---------|-------------|--------------------------------------------------------------|--|

| Solder Mask Thickness<br>(mil) | N/A        | 0.8     | 0.6     | 1.0         |                                                              |  |

| Solder Mask E <mark>r</mark>   | N/A        | 3.65    | 3,65    | 3.65        |                                                              |  |

| Core Thickness (mil)           | N/A        | 2.8     | 3.0     | 3.2         |                                                              |  |

| Core E <mark>r</mark>          | N/A        | 4.3     | 3.75    | 4.85        | 2113 material                                                |  |

| Diana Thialmaaa (mil)          | Power      | 2.7     | 2.5     | 2.9         |                                                              |  |

| Plane Thickness (mil)          | Ground     | 1.35    | 1.15    | 1.55        |                                                              |  |

|                                | 1          | 3.5     | 3.3     | 3.7         |                                                              |  |

| Trace Height (mil)             | 2          | 7.0     | 6.7     | 7.3         | The trace height is determined to achieve a nominal 60 ohms. |  |

|                                | 3          | 7.0     | 6.7     | 7.3         |                                                              |  |

|                                | Microstrip | 4.30    | 3,75    | 4.85        | 2113 material                                                |  |

| Preg E <sub>r</sub>            | Stripline1 | 4.30    | 3,75    | 4.85        |                                                              |  |

|                                | Stripline2 | 4.66    | 4.19    | 5.13        |                                                              |  |

| The set This lands of (mill)   | Microstrip | 1.75    | 1.2     | 2.3         |                                                              |  |

| Trace Thickness (mil)          | Stripline  | 1.4     | 1.2     | 1.6         |                                                              |  |

|                                | Microstrip | 4.0     | 2.5     | 5,5         |                                                              |  |

| Trace Width (mil)              | Stripline  | 4.0     | 2.5     | 5.5         |                                                              |  |

| Total Thickness (mil)          | FR4        | 62.0    | 56.0    | 68.0        |                                                              |  |

| Trace Velocity (ps/in)         | Microstrip |         | 135     | 141         | Velocity varies based on variation in Er. It                 |  |

|                                | Stripline  |         | 167     | 178         | cannot be controlled during the fab<br>process.              |  |

| Trace Impedance                | Microstrip | 60      | 51      | 69          |                                                              |  |

| irace impedance                | Stripline  | 60      | 51      | 69          |                                                              |  |

#### Table 2. Adapter Card Stack Up, Microstrip and Stripline

**Note:** Each interface sets the trace spacing based on its signal integrity of differential impedance requirements. For the purposes of the building the transmission line models, it is assumed the artwork is very accurate and therefore a constant. Thus, all the variability in the trace spacing is the result of the tolerances of the trace width.

Figure 5. Adapter Card Stackup

## 3.3 PCB Impedance Targets

The below tables provide the impedance ranges and the associated trace dimensions for single-ended and differential traces. Figure 4 shows an example of a differential trace.

#### Table 3.Single-ended Trace Parameters

| Single Line |      |                        |       |         |              |                |  |

|-------------|------|------------------------|-------|---------|--------------|----------------|--|

| Topology    | Ohms | Actual Impedance Range |       |         | Width (mils) | Spacing (mils) |  |

|             |      | Min                    | Max   | Nominal |              |                |  |

| Stripline   | 50   | 44.17                  | 57,47 | 50 .82  | 4            | N/A            |  |

| Stripline   | 60   | 51.16                  | 66,62 | 58,89   | 4            | N/A            |  |

| Microstrip  | 50   | 42.97                  | 57,46 | 50.22   | 5            | N/A            |  |

| Microstrip  | 60   | 51.30                  | 67.89 | 59,60   | 4            | N/A            |  |

#### Table 4. Differential Trace Dimensions

|            | Differential Pair |                        |        |         |              |                                |  |  |

|------------|-------------------|------------------------|--------|---------|--------------|--------------------------------|--|--|

| Topology   | Ohms              | Actual Impedance Range |        |         | Width (mils) | Edge to edge<br>Spacing (mils) |  |  |

|            |                   | Min                    | Мах    | Nominal |              |                                |  |  |

| Stripline  | 85                | 74.24                  | 102.28 | 92      | 4            | 8                              |  |  |

| Stripline  | 100               | 87.06                  | 121.84 | 100     | 4            | 8                              |  |  |

| Microstrip | 85                | 71.56                  | 119.36 | 88      | 5            | 7                              |  |  |

| Microstrip | 100               | 80.36                  | 114.28 | 100     | 4            | 8                              |  |  |

## 4.0 PCI-X Layout Guidelines

This section provides an overview of the PCI-X layout recommendations based on Intel's presilicon simulation results. The results were compiled for a motherboard with 50 ohm impedance and an adapter card with 60 ohm impedance.

- Section 4.1 provides details on the PCI-X Frequency control.

- Section 4.2 provides the layout recommendations for each of the topologies and PCI-X speeds.

For more information on the PCI-X standard refer to *PCI-X Addendum to the PCI Local Bus Specification*, Revision 1.0a on the www.pcisig.com website.

### 4.1 PCI/PCI-X Frequency Selection

Intel® 413808 and Intel® 413812 I/O Controllers can only function as an endpoint mode **PCIX\_EP#** = 0 strap is set with a pull-down.

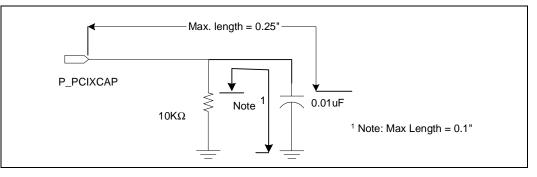

Figure 6 provides layout guidelines for locating the connections from the PCIXCAP pin on the card edge connector for an adapter card. With Intel® 413808 and Intel® 413812 I/O Controllers on an adapter card the P\_PCIXCAP pin should be pulled-up with an 8.2K resistor.

#### Figure 6. P\_PCIXCAP Layout Guidelines

Table 5 describes the PCI-X bus mode and frequency initialization pattern. Intel® 413808 and Intel® 413812 I/O Controllers will decode this initialization pattern to determine the bus frequency.

#### Table 5. PCI-X Initialization Pattern

| DEVSEL#    | STOP#      | TRDY#      | Mode   | Clock Pe | riod (ns) | Clock Frequency (MHz) |     |

|------------|------------|------------|--------|----------|-----------|-----------------------|-----|

| DEVSEL#    |            |            |        | Max      | Min       | Min                   | Max |

| Deasserted | Deasserted | Deasserted | PCI 33 | 60       | 30        | 16                    | 33  |

| Deasserted |            |            | PCI 66 | 30       | 15        | 33                    | 66  |

| Deasserted | Deasserted | Asserted   | PCI-X  | 20       | 15        | 50                    | 66  |

| Deasserted | Asserted   | Deasserted | PCI-X  | 15       | 10        | 66                    | 100 |

| Deasserted | Asserted   | Asserted   | PCI-X  | 10       | 7.5       | 100                   | 133 |

## 4.2 PCI-X Layout Recommendations

This section provides the layout recommendations for PCI-X topologies in the following subsections:

- Section 4.2.1, "PCI-X Clock Routing"

- Section 4.2.2, "133 MHz One Slot Topology"

- Section 4.2.3, "Embedded 133 MHz Topology"

- Section 4.2.4, "Mixed 133 MHz Topology"

- Section 4.2.5, "100 MHz Two Slot Topology"

- Section 4.2.6, "Embedded 100 MHz Topology"

- Section 4.2.7, "Mixed 100 MHz Topology"

- Section 4.2.8, "66 MHz PCIX Four Slot Topology"

- Section 4.2.9, "Embedded 66 MHz Topology"

- Section 4.2.10, "Mixed 66 MHz Topology"

#### 4.2.1 PCI-X Clock Routing

This section lists general recommendations for routing the PCI-X clock to the Intel® 413808 and Intel® 413812 I/O Controllers PCI-X clock input.

#### Table 6. PCI-X Clock Layout Guidelines

| Parameter                                                                   | Routing Guidelines                                                                                                                                                               |

|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reference Plane                                                             | Route over unbroken ground plane.                                                                                                                                                |

| Recommended Layer                                                           | Stripline                                                                                                                                                                        |

| Trace Impedance: Motherboard                                                | Microstrip: 50 ohm +/- 15%, stripline: 50 ohm +/- 10%                                                                                                                            |

| Trace Impedance: Adapter Card                                               | Microstrip or stripline: 60 ohm +/- 15%                                                                                                                                          |

| Trace Spacing (edge to edge)                                                | <ul> <li>between two different clock lines ≥ 25 mils</li> <li>between two segments of the same clock line≥ 25 mils</li> <li>between clock and other signals ≥ 50 mils</li> </ul> |

| Series Resistors                                                            | 28 ohms 1% for an adapter card with a connector<br>26 ohms 1% for embedded (device to device)                                                                                    |

| Trace Length TL1 from clock input to the resistor                           | 1.0″ max                                                                                                                                                                         |

| Total Trace Length: from device ball to device (including resistor segment) | 11″ max                                                                                                                                                                          |

| Length Matching:                                                            | Match all clock lines to within 0.25 mils                                                                                                                                        |

| Vias                                                                        | $\leq 2$ vias                                                                                                                                                                    |

#### 4.2.1.1 **Point-to-Point Signals (REQ#/GNT#)**

This section provides the layout guidelines for REQ# and GNT# lines. Topology in Figure 7 for 133MHz slot design is the same as the one used for point-to-point signals.

#### Table 7. PCI-X REQ#/GNT# Layout Guidelines

| Parameter                                         | Routing Guidelines                                                                                                                    |

|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Signal Group                                      | REQ# and GNT# lines                                                                                                                   |

| Reference Plane                                   | Route over unbroken reference plane.                                                                                                  |

| Motherboard Impedance (microstrip)                | 50 ohm +/- 15% microstrip and 50 ohm +/- 10% stripline                                                                                |

| Motherboard Trace Spacing                         | 14 mils microstrip and 12 mils stripline                                                                                              |

| Add-in Card Impedance                             | 60 ohm +/- 15% microstrip and stripline                                                                                               |

| Add-in Card Trace Spacing                         | 18 mils microstrip and 14 mils stripline                                                                                              |

| Group Spacing: Spacing from other groups          | 25 mils minimum, edge to edge                                                                                                         |

| Trace Length TL1 - from buffer to the connector   | <ul> <li>0.5" min to 4.5" max for 133MHz</li> <li>0.5"min to 12.0" max for 100MHz</li> <li>0.5" min to 15.0" max for 66MHz</li> </ul> |

| Trace Length TL2 - from connector to the receiver | 2.4" - 2.6" max                                                                                                                       |

| Vias                                              | $\leq$ 3 vias                                                                                                                         |

### 4.2.2 133 MHz One Slot Topology

This section lists the parameters used for the address/data and control lines for 133 MHz single slot design.

#### Table 8.133 MHz Single-Slot Topology

| D                                                 | Routing Guidelines                                       |                   |

|---------------------------------------------------|----------------------------------------------------------|-------------------|

| Parameter                                         | Lower AD                                                 | Upper AD          |

| Signal Group                                      | Address, data and control lines                          |                   |

| Reference Plane                                   | Route over unbroken reference plane.                     |                   |

| Motherboard Impedance (microstrip)                | 50 ohm +/- 15% microstrip and 50 ohm +/- 10% stripline   |                   |

| Motherboard Trace Spacing                         | 14 mils microstrip<br>12 mils stripline                  |                   |

| Add-in Card Impedance                             | 60 ohm +/- 15% microstrip and stripline                  |                   |

| Add-in Card Trace Spacing                         | 14 mils microstrip and stripline                         |                   |

| Group Spacing                                     | Spacing from other groups: 25 mils minimum, edge to edge |                   |

| Trace Length TL1 - from SL ball to the connector  | 1.0″ - 6.0″ max                                          | 0.5″ - 5.0″ max   |

| Trace Length TL2 - from connector to the receiver | 0.75″- 1.5″ Max                                          | 1.75″ - 2.75″ Max |

| Vias                                              | < 3 vias                                                 |                   |

#### Figure 7. 133 MHz One Slot Topology

## 4.2.3 Embedded 133 MHz Topology

This section lists the parameters used for the address, data and control signals for 133 MHz embedded design with two embedded devices.

#### Table 9. Embedded 133 MHz Topology

| Parameter                                        | Routing Guidelines                                       |  |

|--------------------------------------------------|----------------------------------------------------------|--|

| Parameter                                        | Lower AD Upper AD                                        |  |

| Signal Group                                     | Address, Data and control line                           |  |

| Reference Plane                                  | Route over unbroken reference plane.                     |  |

| Motherboard Impedance (microstrip)               | 50 ohm +/- 15%                                           |  |

| Motherboard Impedance (Stripline                 | 50 ohm +/- 10%                                           |  |

| Motherboard Trace Spacing                        | 14 mils microstrip, 12 mils stripline                    |  |

| Group Spacing                                    | Spacing from other groups: 25 mils minimum, edge to edge |  |

| Trace Length TL1 - from ball to the junction     | 0.75" min. to 2.5" max                                   |  |

| Trace Length TL3 - from junction to junction     | 0.75" min. to 2.5" max                                   |  |

| Trace Length TL2, TL4, from junction to receiver | 0.75" min. to 2.5" max                                   |  |

| Vias                                             | < 3 vias                                                 |  |

### 4.2.4 Mixed 133 MHz Topology

This section lists the parameters used for the address, data and control signals for 133 MHz embedded design with one embedded load and one connector.

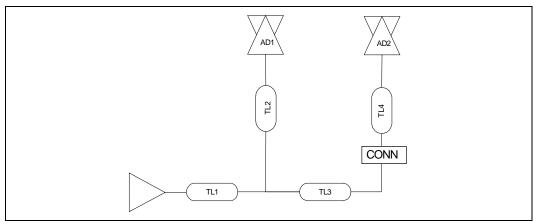

#### Figure 9. Mixed 133 MHz Topology

#### Table 10. Mixed 133 MHz Topology

| Parameter                                          | Routing Guidelines                                       |                         |

|----------------------------------------------------|----------------------------------------------------------|-------------------------|

| Parameter                                          | Lower AD Upper AD                                        |                         |

| Signal Group                                       | Data and control line                                    |                         |

| Reference Plane                                    | Route over unbroken reference plane.                     |                         |

| Motherboard Impedance (microstrip)                 | 50 ohm +/- 15% microstrip and 50 ohm +/- 10% stripline   |                         |

| Motherboard Trace Spacing                          | 18 mils microstrip<br>14 mils stripline                  |                         |

| Add-in Card Impedance                              | 60 ohm +/- 15% microstrip and stripline                  |                         |

| Add-in Card Trace Spacing                          | 18 mils microstrip and 14 mils stripline                 |                         |

| Group Spacing                                      | Spacing from other groups: 25 mils minimum, edge to edge |                         |

| Trace Length TL1 - from SL ball to the<br>junction | 0.5" min. to 2.0" max                                    | 0.5″ min. to 2.0″ max   |

| Trace Length TL2 - from junction to AD1            | 0.5" min. to 2.0" max                                    | 0.5″ min. to 2.0″ max   |

| Trace Length TL3, from junction to CONN            | 0.5" min. to 3.5" max                                    | 0.5″ min. to 2.25″ max  |

| Trace Length TL4, from CONN to adapter             | 0.75″ min. to 1.5″ max                                   | 1.75" min. to 2.75" max |

| Vias                                               | < 3 vias                                                 |                         |

## 4.2.5 100 MHz Two Slot Topology

This section lists the parameters used for the address, data and control signals for 100 MHz. This topology is shown in Figure 10.

Figure 10. 100 MHz Dual Slot Topology

#### Table 11. 100 MHz Two Slot Topology

| Parameter                                                                                             | Routing Guidelines                                       |                   |

|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------|

| Parameter                                                                                             | Lower AD                                                 | Upper AD          |

| Signal Group                                                                                          | Data and control line                                    |                   |

| Reference Plane                                                                                       | Route over unbroken reference plane.                     |                   |

| Motherboard Impedance (microstrip)                                                                    | 50 ohm +/- 15% microstrip and 50 ohm +/- 10% stripline   |                   |

| Motherboard Trace Spacing                                                                             | 18 mils microstrip<br>14 mils stripline                  |                   |

| Add-in Card Impedance                                                                                 | 60 ohm +/- 15% microstrip and stripline                  |                   |

| Add-in Card Trace Spacing                                                                             | 18 mils microstrip and 14 mils stripline                 |                   |

| Group Spacing                                                                                         | Spacing from other groups: 25 mils minimum, edge to edge |                   |

| Trace Length TL1 - from ball to the connector                                                         | 0.5″ - 12.0″ max                                         | 0.5″ - 10.0″ max  |

| Trace Lengths TL3 - Between connectors                                                                | 0.5″ - 3.0″ max                                          | 0.5″ - 3.0″ max   |

| Trace Lengths TL2 - from connector to the first receiver, TL4 - from connector to the second receiver | 0.75″ - 1.50″ max                                        | 1.75″ - 2.75″ max |

| Vias                                                                                                  | < 3 vias                                                 |                   |

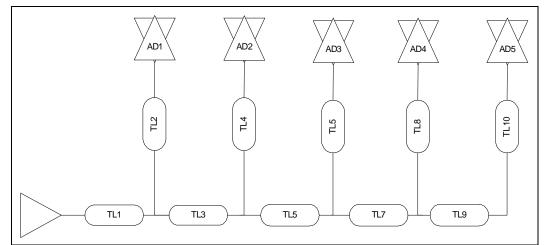

### 4.2.6 Embedded 100 MHz Topology

This section lists the parameters used for the address, data and control signals for 100 MHz embedded design with five embedded loads.

#### Table 12. Embedded 100 MHz Topology

| Parameter                                                           | Routing Guidelines                                                 |  |

|---------------------------------------------------------------------|--------------------------------------------------------------------|--|

| Parameter                                                           | Lower AD Upper AD                                                  |  |

| Signal Group                                                        | Address, data and control line                                     |  |

| Reference Plane                                                     | Route over unbroken reference plane.                               |  |

| Motherboard Impedance (microstrip)                                  | 50 ohm +/- 15% microstrip and 50 ohm +/- 10% stripline             |  |

| Motherboard Trace Spacing                                           | 18 mils microstrip<br>14 mils stripline                            |  |

| Group Spacing                                                       | spacing from other groups: 25 mils minimum, edge to edge           |  |

| Trace Length TL1 - from SL ball to the junction                     | 0.5" min. to 3.0" max (3 loads, 5 loads)                           |  |

| Trace Length TL3, TL5, TL7, TL9: from junction to junction          | 0.5° min. to 2.0″ max (3 loads)<br>0.5° min. to 1.0″ max (5 loads) |  |

| Trace Length TL2, TL4, TL6, TL8, TL10:<br>from junction to receiver | 0.5" min. to 3.0″ max (3 loads)<br>0.5″ min to 2.0″ max (5 loads)  |  |

| Vias                                                                | <u>&lt;</u> 4 vias                                                 |  |

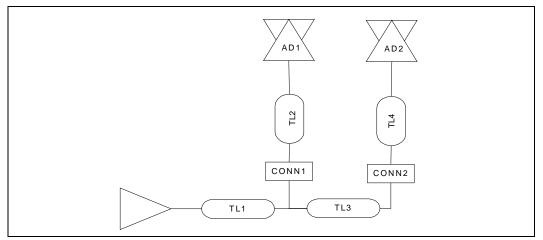

## 4.2.7 Mixed 100 MHz Topology

This section lists the parameters used for the address, data and control signals for 100 MHz embedded design with one embedded load and two connectors.

#### Figure 12. Mixed 100 MHz Topology

#### Table 13. Mixed 100 MHz Topology

| Parameter                                                                        | Routing Guidelines                                       |                         |

|----------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------|

| Parameter                                                                        | Lower AD                                                 | Upper AD                |

| Signal Group                                                                     | Address, data and control line                           |                         |

| Reference Plane                                                                  | Route over unbroken reference plane.                     |                         |

| Motherboard Impedance (microstrip)                                               | 50 ohm +/- 15% microstrip and 50 ohm +/- 10% stripline   |                         |

| Motherboard Trace Spacing                                                        | 18 mils microstrip<br>14 mils stripline                  |                         |

| Add-in Card Impedance                                                            | 60 ohm +/- 15% microstrip and stripline                  |                         |

| Add-in Card Trace Spacing                                                        | 18 mils microstrip and 14 stripline                      |                         |

| Group Spacing                                                                    | Spacing from other groups: 25 mils minimum, edge to edge |                         |

| Trace Length TL1 - from SL ball to the junction                                  | 0.5″ min. to 2.5″ max                                    | 0.5″ min. to 2.5″ max   |

| Trace Length TL2 - from junction to AD1                                          | 0.5″ min. to 2.0″ max                                    | 0.5″ min. to 2.0″ max   |

| Trace Length TL3, from junction to first CONN                                    | 0.5″ min. to 3.5″ max                                    | 0.5″ min. to 3.0″ max   |

| Trace Length TL5, from 1st CONN to 2nd<br>CONN                                   | 0.5" min. to 3.5" max                                    | 0.5″ min. to 3.5″ max   |

| Trace Length TL4, from 1st CONN to AD2<br>Trace Length TL6, from 2nd CONN to AD3 | 0.75" min. to 1.5" max                                   | 1.75″ min. to 2.75″ max |

| Vias                                                                             | <u>&lt;</u> 3 vias                                       |                         |

## 4.2.8 66 MHz PCIX Four Slot Topology

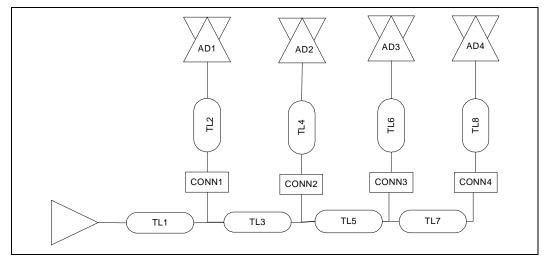

This section lists the parameters used for the address, data and control signals for 66 MHz. This topology is shown in Figure 13.

Figure 13. 66 MHz Four Slot Topology

#### Table 14. 66 MHz Four Slot Topology

| Parameter                                                         | Routing Guidelines                                       |                   |

|-------------------------------------------------------------------|----------------------------------------------------------|-------------------|

| Parameter                                                         | Lower AD                                                 | Upper AD          |

| Signa  Group                                                      | Data and control line                                    |                   |

| Reference Plane                                                   | Route over unbroken reference plane.                     |                   |

| Motherboard Impedance (microstrip)                                | 50 ohm +/- 15% microstrip and 50 ohm +/- 10% stripline   |                   |

| Motherboard Trace Spacing                                         | 18 mils microstrip<br>14 mils stripline                  |                   |

| Add-in Card Impedance                                             | 60 ohm +/- 15% microstrip and stripline                  |                   |

| Add-in Card Trace Spacing                                         | 12 mils microstrip and 12 mils stripline                 |                   |

| Group Spacing                                                     | Spacing from other groups: 25 mils minimum, edge to edge |                   |

| Trace Length TL1 - from ball to the connector                     | 0.5″ - 12.0″ max                                         | 0.5″-9.0″ max     |

| Trace Lengths TL3, TL5, TL7 - Between connectors                  | 0.5″ - 2.0″ max                                          | 0.5″ - 2.0″ max   |

| Trace Lengths TL2, TL4, TL6, TL8- from connector to the receivers | 0.75″ - 1.50″ max                                        | 1.75″ - 2.75″ max |

| Vias                                                              | <u>&lt;</u> 4 vias                                       | •                 |

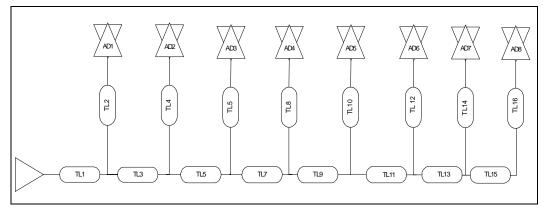

## 4.2.9 Embedded 66 MHz Topology

This section lists the parameters used for the address, data and control signals for 66 MHz embedded design with 8 embedded loads.

#### Figure 14. Embedded 66 MHz Topology

#### Table 15.Embedded 66 MHz Topology

| Parameter                                                                             | Routing Guidelines                                                 |          |

|---------------------------------------------------------------------------------------|--------------------------------------------------------------------|----------|

| raianietei                                                                            | Lower AD                                                           | Upper AD |

| Signa   Group                                                                         | Address, data and control line                                     |          |

| Reference Plane                                                                       | Route over unbroken reference plane.                               |          |

| Motherboard Impedance (microstrip)                                                    | 50 ohm +/- 15% microstrip and 50 ohm +/- 10% stripline             |          |

| Motherboard Trace Spacing                                                             | 18 mils microstrip<br>14 mils stripline                            |          |

| Group Spacing                                                                         | Spacing from other groups: 25 mils minimum, edge to edge           |          |

| Trace Length TL1 - from SL ball to the junction                                       | 0.5° min. to 3.0″ max (8 loads)<br>0.5° min. to 3.5″ max (6 loads) |          |

| Trace Length TL3, TL5, TL7,<br>TL9,TL11,TL13,TL15: from junction to<br>junction       | 0.5° min. to 1.5″ max (8 loads)<br>0.5° min. to 2.5″ max (6 loads) |          |

| Trace Length TL2, TL4, TL6, TL8,<br>TL10,TL12,TL14,TL16: from junction to<br>receiver | 0.5" min. to 1.5" max (8 loads)<br>0.5" min to 2.0" max (6 loads)  |          |

| Vias                                                                                  | <u>&lt;</u> 4 vias                                                 |          |

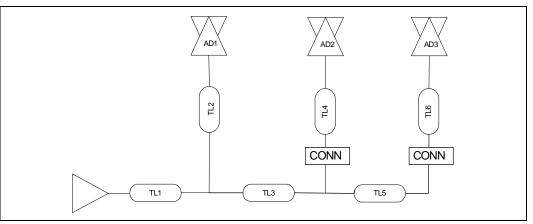

### 4.2.10 Mixed 66 MHz Topology

This section lists the parameters used for the address, data and control signals for 66 MHz embedded design with one embedded load and two connectors.

#### Figure 15. Mixed 66 MHz Topology

#### Table 16.Mixed 66 MHz Topology

| Parameter                                                           | Routing Guidelines                                       |                         |

|---------------------------------------------------------------------|----------------------------------------------------------|-------------------------|

| Parameter                                                           | Lower AD                                                 | Upper AD                |

| Signal Group                                                        | Address, data and control line                           |                         |

| Reference Plane                                                     | Route over unbroken reference plane.                     |                         |

| Motherboard Impedance (microstrip)                                  | 50 ohm +/- 15% microstrip and 50 ohm                     | n +/- 10% stripline     |

| Motherboard Trace Spacing                                           | 18 mils microstrip<br>14 mils stripline                  |                         |

| Add-in Card Impedance                                               | 60 ohm +/- 15% microstrip and stripline                  |                         |

| Add-in Card Trace Spacing                                           | 12 mils microstrip and 12 mils stripline                 |                         |

| Group Spacing                                                       | Spacing from other groups: 25 mils minimum, edge to edge |                         |

| Trace Length TL1 - from SL ball to the junction                     | 0.5″ min. to 11″ max                                     | 0.5″ min. to 10″ max    |

| Trace Length TL2, TL4 - from junction to AD1, AD2                   | 0.5″ min. to 4.5″ max                                    | 0.5″ min. to 4.0″ max   |

| Trace Length TL3, TL5, TL7 from junction to junction                | 0.5″ min. to 4.0″ max                                    | 0.5″ min. to 4.0″ max   |

| Trace Length TL6 from 1st CONN to AD3,<br>TL8: from 2nd CONN to AD4 | 0.75″ min. to 1.5″ max                                   | 1.75″ min. to 2.75″ max |

| Vias                                                                | <u>&lt;</u> 4 vias                                       |                         |

### 4.2.11 Additional PCI Layout Notes

- The **P\_INT[D:A]#** signals do not have any length restrictions.

- When PCIX\_PULLUP# is pulled-low, it enables internal pull-ups on the following PCI signals: P\_AD[63:32], P\_C/BE[7:4]#, P\_PAR64, P\_REQ64#, P\_ACK64#, P\_FRAME#, P\_IRDY#, P\_TRDY#, P\_STOP#, P\_DEVSEL#, P\_SERR#, P\_INT[D:A]#, and P\_PERR#.

- If application requires external pull-ups on the upper P\_AD bus make sure that the location of the pull-up is less than  $\leq 1''$  from the ball.

413808 and 413812 - PCI Express Layout

## 5.0 PCI Express Layout

This section provides an overview of the PCI Express layout recommendation based on simulation results. PCI Express is a serial differential low-voltage point-to-point interconnect. The PCI Express was designed to support 20 inches between components with standard FR4.

For more information on the PCI Express standard refer to PCI Express Base Specification 1.0a and the *PCI Express Card Electromechanical Specification*, revision1.0a, found on the http://www.pcisig.com/home website.

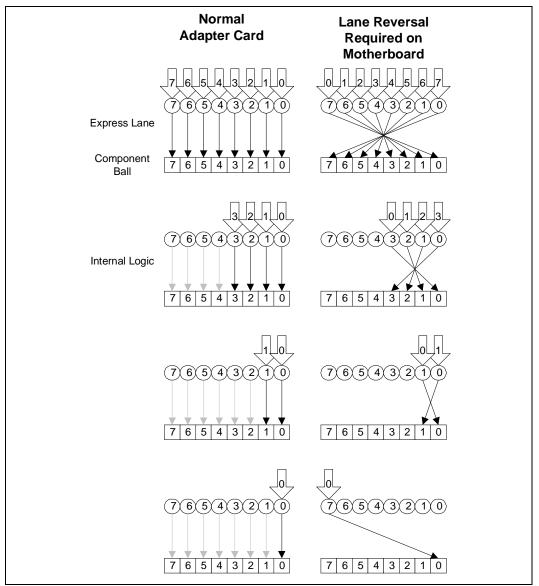

## 5.1 Optional PCI Express Lane Reversal

The following Figure 16 describes the lane reversal which can be considered when you are designing a PCI-E x8 motherboard slot or an adapter card to improve PCB routing. Note that the adapter card PCI-E pins map with a straight through connection but the motherboard can implement lane reversal in x8, x4, x2 and x1 configurations as shown in Figure 16.

#### Figure 16. PCI Express Lane Reversal To Improve PCB Routing

## 5.2 **PCI Express Layout recommendations**

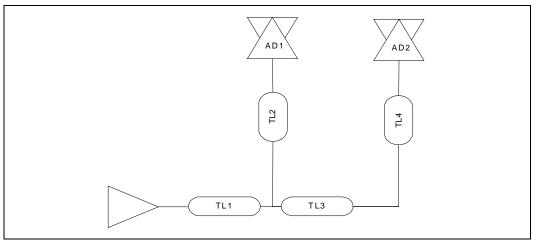

The following recommendations are summarized based on our presilicon simulation results for the following topologies:

- 1. motherboard topology with the PCI Express device on the board Section 5.2.1.

- 2. motherboard topology with a PCI Express connector and an adapter card topology with the device on the card Section 5.2.2.

The PCI Express clock layout recommendations are listed in Section 5.2.3.

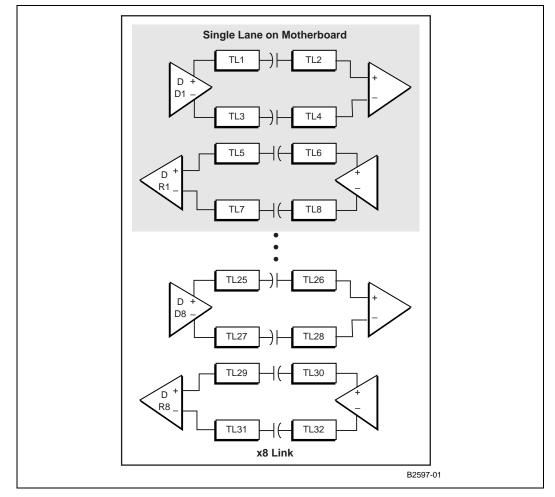

#### 5.2.1 PCI Express Motherboard Layout Guidelines

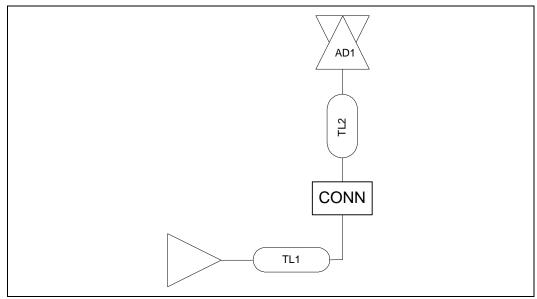

The following layout recommendations were determined for a motherboard application with the PCI Express device on the board.

#### Figure 17. Motherboard Topology

| Parameter                                                                                                                                                | Routing Guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Signal Group                                                                                                                                             | Transmit and receive differential pairs                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| Reference Plane                                                                                                                                          | Routing over unbroken ground plane is preferred. If unbroken ground plane is not available, route over unbroken voltage plane.                                                                                                                                                                                                                                                                                                                     |  |

| Characteristic Trace Impedance:                                                                                                                          | Single-ended: 50 ohms +/- 15%<br>Differential: 85 ohms nominal +/-15%                                                                                                                                                                                                                                                                                                                                                                              |  |

| Microstrip Trace Width                                                                                                                                   | 5 mils (Refer to Table Note)                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| Microstrip Trace Spacing                                                                                                                                 | <ul> <li>Between + (P) and - (N) of pair: 7 mils edge to edge</li> <li>Between other signals: ≥ 25 mils edge to edge</li> <li>Transmit and receive pairs should be interleaved. If interleaving is not possible, then the spacing between pairs (inter pair) should be increased to ≥ 45 mils (edge to edge). Edge to Edge of inter pair is defined as edge of Positive of one pair to edge of Negative of the next pair or vice versa.</li> </ul> |  |

| Stripline Trace Width                                                                                                                                    | 5 mils (Refer to Table Note below)                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| Stripline Trace Spacing                                                                                                                                  | <ul> <li>Between + (P) and - (N) of pair: 7 mils edge to edge</li> <li>Between other pairs : ≥ 25 mils edge to edge</li> <li>Transmit and receive pairs should be interleaved. If interleaving is not possible, then inter pair spacing should be increased to 45 mils (edge to edge). Edge to Edge of inter pair is defined as edge of Positive of one pair to edge of Negative of the next pair or vice versa.</li> </ul>                        |  |

| Group Spacing                                                                                                                                            | Spacing from other groups: > 25 mils minimum from edge to edge for microstrip or stripline.                                                                                                                                                                                                                                                                                                                                                        |  |

| AC Coupling                                                                                                                                              | AC Coupling capacitors must be located at the transmitter. Required values of 75 nF to 200 nF.                                                                                                                                                                                                                                                                                                                                                     |  |

| Total Trace Length - (Transmitter/Receiver)<br>from device signal pin to AC coupling<br>capacitor and AC coupling capacitor to PCI<br>Express device pin | 1.0″ min 30.0″ max                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |